オライリーのコンピュータ作りの話では、論理回路からごく簡単なCPUを作り、それでいわゆる中間言語のインタプリタを作成します。中間言語はN-BASICやMSX-BASIC等を知っている方は言葉は聞いたことがあると思います。

その上で、割と本格的なコンパイラを作って高級言語で書かれたソースプログラムを中間言語に翻訳し、実行しようという計画です。

インテル8080が登場した時にも、同様の試みがあって、ただしこの方法はtiny BASICよりも周辺機器が充実している必要があるので見送った覚えがあります。

この中間言語インタプリタを仮想マシンと称しています。OSの仮想マシン(OS自体が動作する)とは異なります。独自の命令体系とレジスタ構成を持つ、仮想CPUとでも言えるものです。

この本の中間言語は現在のCPUの機械語に近い感じがします。こちらで考えると、CPUの一命令を実行するたびに数個のマイクロプログラムが実行されることになります。

やっと本題に近づいてきました。現在では中間言語は広範に使用されていると思います。しかし組み込みマイコンなどではC言語などのいわゆるネイティブコンパイラが好まれると思います。階層が1段異なりますが、ここではCPUの機械語が内部ではマイクロプログラムで実行されると考えます。マイクロプログラムは1語がたとえば40bitとかで、演算を指定するだけで無く、条件分岐の条件と次のアドレスまでが含まれます。そのままではメモリの使用効率が悪いので、機械語を上位に置く、ということ。

これで割と高級なCPUが比較的に少量の論理回路で組めます。しかしその代償として一命令の実行に数クロックを費やすことになります。ハードを追加して、命令ごとのクロック数を減らすのが次の段階です。

もちろん私はこの段階を実際の回路で試したことはないので、ここからの文章にかなりの私の勝手な想像が入ります。

命令実行には命令解釈と実行の2段階がまず分けられます。なので回路を分離して流れ作業させます。さらに作業を分割して…、私が大型機を扱った時代には4段階程度のパイプラインは実現されていました。

マイコンではある程度普及してから大型機への追従が始まり、今は最先端になっていると思います。かつては20段のパイプラインとかを聞いたことがあります。ええ、CPUの中身の話ですから本当かどうかは確かめることができません。

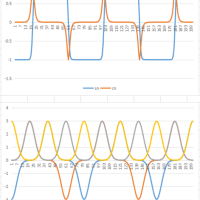

しかし、パイプラインが流れるためには命令が継続して実行される必要があります。普通に考えるとそう。そして、コンパイラが生成する機械語には5~6命令ごとに条件分岐の命令が入るそうです。元のC言語などではif文とかwhile文とかです。

分岐してしまうと流れ作業は中断して、パイプラインをご破算にします。なので長大なパイプラインが必ずしも実行速度の向上に寄与しない事態が起こってしまったようです。

RISCと呼ばれるCPUの設計方針が話題になった初期には、この実行の流れの分岐時の取り扱いにかなりの注意が払われていました。たとえば、ARMの命令に中に名残が見られます。

しかし、命令パイプラインをもっと伸ばして、分岐命令を含む塊を取り込んでしまえばパイプライン内のいくつかのデータは廃棄されるものの、依然としてCPU内の高速メモリ内で処理が続行されるでしょう。つまり、直接確認することはできないものの、私の感触では現在では2段階程度の分岐先がCPU内で同時に取り扱われているようです。

LISPではCOND形式のみで関数が書ける方には想像の範囲内と思います。PROLOGでは述語を構成する数行に相当します。形式上は木構造になっていて、いわゆる末尾再帰でループが実現されます。

まあ、ちょっと考えるだけでも変数のつじつま合わせとか、考慮事項は大変な規模になると予想されます。一方で、気の利いたコンパイラの最適化では思い切った再構成をやっているみたいで、だとするとこれをハードでやってしまおう、と言う発想は自然な流れのような気がします。

その上で、割と本格的なコンパイラを作って高級言語で書かれたソースプログラムを中間言語に翻訳し、実行しようという計画です。

インテル8080が登場した時にも、同様の試みがあって、ただしこの方法はtiny BASICよりも周辺機器が充実している必要があるので見送った覚えがあります。

この中間言語インタプリタを仮想マシンと称しています。OSの仮想マシン(OS自体が動作する)とは異なります。独自の命令体系とレジスタ構成を持つ、仮想CPUとでも言えるものです。

この本の中間言語は現在のCPUの機械語に近い感じがします。こちらで考えると、CPUの一命令を実行するたびに数個のマイクロプログラムが実行されることになります。

やっと本題に近づいてきました。現在では中間言語は広範に使用されていると思います。しかし組み込みマイコンなどではC言語などのいわゆるネイティブコンパイラが好まれると思います。階層が1段異なりますが、ここではCPUの機械語が内部ではマイクロプログラムで実行されると考えます。マイクロプログラムは1語がたとえば40bitとかで、演算を指定するだけで無く、条件分岐の条件と次のアドレスまでが含まれます。そのままではメモリの使用効率が悪いので、機械語を上位に置く、ということ。

これで割と高級なCPUが比較的に少量の論理回路で組めます。しかしその代償として一命令の実行に数クロックを費やすことになります。ハードを追加して、命令ごとのクロック数を減らすのが次の段階です。

もちろん私はこの段階を実際の回路で試したことはないので、ここからの文章にかなりの私の勝手な想像が入ります。

命令実行には命令解釈と実行の2段階がまず分けられます。なので回路を分離して流れ作業させます。さらに作業を分割して…、私が大型機を扱った時代には4段階程度のパイプラインは実現されていました。

マイコンではある程度普及してから大型機への追従が始まり、今は最先端になっていると思います。かつては20段のパイプラインとかを聞いたことがあります。ええ、CPUの中身の話ですから本当かどうかは確かめることができません。

しかし、パイプラインが流れるためには命令が継続して実行される必要があります。普通に考えるとそう。そして、コンパイラが生成する機械語には5~6命令ごとに条件分岐の命令が入るそうです。元のC言語などではif文とかwhile文とかです。

分岐してしまうと流れ作業は中断して、パイプラインをご破算にします。なので長大なパイプラインが必ずしも実行速度の向上に寄与しない事態が起こってしまったようです。

RISCと呼ばれるCPUの設計方針が話題になった初期には、この実行の流れの分岐時の取り扱いにかなりの注意が払われていました。たとえば、ARMの命令に中に名残が見られます。

しかし、命令パイプラインをもっと伸ばして、分岐命令を含む塊を取り込んでしまえばパイプライン内のいくつかのデータは廃棄されるものの、依然としてCPU内の高速メモリ内で処理が続行されるでしょう。つまり、直接確認することはできないものの、私の感触では現在では2段階程度の分岐先がCPU内で同時に取り扱われているようです。

LISPではCOND形式のみで関数が書ける方には想像の範囲内と思います。PROLOGでは述語を構成する数行に相当します。形式上は木構造になっていて、いわゆる末尾再帰でループが実現されます。

まあ、ちょっと考えるだけでも変数のつじつま合わせとか、考慮事項は大変な規模になると予想されます。一方で、気の利いたコンパイラの最適化では思い切った再構成をやっているみたいで、だとするとこれをハードでやってしまおう、と言う発想は自然な流れのような気がします。