PWM制御VFOの実験をしていましたが、PWM制御ではなくなったのでタイトルを変更しました。

VFOは一応完成しましたが、周波数可変範囲が300kHz強と広いにもかかわらず8BitのPWMなので256ステップとなり、スプレッドVRを付けましたが操作性が良くありません。

Tanukinoのポートも3ポートしか使っていないので余っています。

そこで、D/Aコンバータで制御する方式を検討してみました。

D/Aコンバータは専用のICがあるのですが、抵抗だけでできるR-2Rラダー方式のD/Aコンバーターを作ってみました。

回路図です。

Rと2Rの値の抵抗から構成されるラダーに0Vか5Vを出力するだけです。

とりあえずAVRの一辺に出ている11ポートを使って11Bitにしてみました。

2Rの抵抗として33kΩの抵抗を使いました。

Rは2本を並列にしました。

200本くらいの中からデジタルテスタで選別しました。

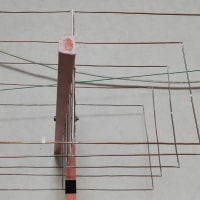

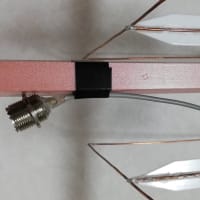

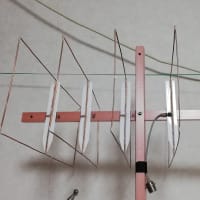

できた基板です。

33kΩの抵抗を各ポートに立てて、その間を空中配線で2本ずつRの部分を配線しました。

合計29本でなかなか痺れる半田付けでした。

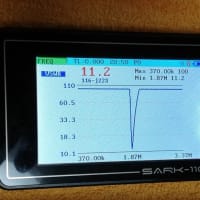

とりあえずロータリーエンコダーを回してテスタで電圧を確認しました。

あと、0~2047を繰り返し出力してオシロで鋸波を観測してみました。

単純計算ですが、1ステップあたり150Hz程度なのでいい感じですね。

VFOは一応完成しましたが、周波数可変範囲が300kHz強と広いにもかかわらず8BitのPWMなので256ステップとなり、スプレッドVRを付けましたが操作性が良くありません。

Tanukinoのポートも3ポートしか使っていないので余っています。

そこで、D/Aコンバータで制御する方式を検討してみました。

D/Aコンバータは専用のICがあるのですが、抵抗だけでできるR-2Rラダー方式のD/Aコンバーターを作ってみました。

回路図です。

Rと2Rの値の抵抗から構成されるラダーに0Vか5Vを出力するだけです。

とりあえずAVRの一辺に出ている11ポートを使って11Bitにしてみました。

2Rの抵抗として33kΩの抵抗を使いました。

Rは2本を並列にしました。

200本くらいの中からデジタルテスタで選別しました。

できた基板です。

33kΩの抵抗を各ポートに立てて、その間を空中配線で2本ずつRの部分を配線しました。

合計29本でなかなか痺れる半田付けでした。

とりあえずロータリーエンコダーを回してテスタで電圧を確認しました。

あと、0~2047を繰り返し出力してオシロで鋸波を観測してみました。

単純計算ですが、1ステップあたり150Hz程度なのでいい感じですね。

それにしても、抵抗の選別、お疲れ様でした。

基板に余裕があるので、OPアンプで1.5倍位にしてみます。

また、VCOの調整をしないといけませんがバリキャップの電圧を0~7.5Vまで広げられます。

8bit程度なら適当に組んでも大丈夫ですが、11bitは結構しんどいかも知れませんね。

そのあたりどうなんでしょうか?