先日製作した50MHzDSBトランシーバはVXOなので、周波数があまり可変できません。

そこで、周波数の安定度は少し悪くなるかもしれませんが、VFOを作ろうと思います。

周波数構成は、5.1~5.4MHzとして、15MHzの水晶を3逓倍した45MHzを加えて50.1~50.4MHzとする予定です。

回路は、ソースタップのハートレー型発振回路です。

「トロイダルコア活用百科」を参考にしました。

共振回路のVCとCの組み合わせで周波数可変範囲を決定します。

最大周波数をFmax、最低周波数をFminとすると、F=1/(2Π√(LC))ですから、以下の関係があります。

VC/C=(Fmax/Fmin)^2-1

VCには30pFのFM用のPVCを使います。

VCの最大容量は公称値を信じるとして、最小値は数pFあるはずです。

また、浮遊容量も数pF加わっています。

実際は実験してみるのが早いのですが、ここでは一応設計してみます。

Fmax=5.4MHz、Fmin=5.1MHz、VC=30pFとするとC=248pFとなりました。

30pFも可変範囲があるとは思えませんので、VC=20pFとすると、C=165pFです。

この範囲の中に正解があるはずです。

VCの容量を正確に測定してみれば参考になりますが、測定条件や実装状態によってぶれますので、今後の課題とします。

今回は、C=165pFから浮遊容量10pFを差し引いて155pFで実験してみます。

手持ちのスチコンの組み合わせで33+120pFです。

LはC=165+20pF/F=5.1MHzからL=5.26uH。T-37-6コア(AL=3.0nH/t^2)を使うので、N=√(L/AL)から42Tとなりました。

このパラメタで実際に回路を組んで測定してみました。

F=5.6~6.0MHzとなり、Cが足りません。

手持ちのスチコンの関係で、Cはそのままとして、Lを増やして45Tとしました。

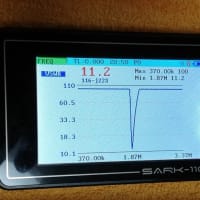

VCのトリマを調整して、5.095~5.420MHzとしました。

この回路図は水魚堂さんの「回路図エディタ BSch3V」で書きました。

水魚堂さんありがとうございました。

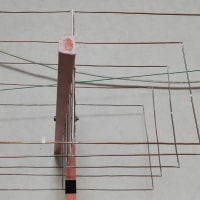

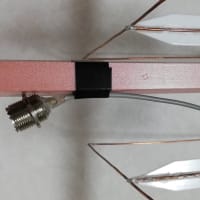

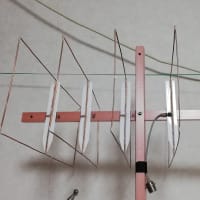

作成した基板です。

横から見たところです。

このあとトロイダルコアとスチコンをエポキシで固めて、プリント基板でシールドケースを作成して完成の予定です。

出力は9dBmでした。

そこで、周波数の安定度は少し悪くなるかもしれませんが、VFOを作ろうと思います。

周波数構成は、5.1~5.4MHzとして、15MHzの水晶を3逓倍した45MHzを加えて50.1~50.4MHzとする予定です。

回路は、ソースタップのハートレー型発振回路です。

「トロイダルコア活用百科」を参考にしました。

共振回路のVCとCの組み合わせで周波数可変範囲を決定します。

最大周波数をFmax、最低周波数をFminとすると、F=1/(2Π√(LC))ですから、以下の関係があります。

VC/C=(Fmax/Fmin)^2-1

VCには30pFのFM用のPVCを使います。

VCの最大容量は公称値を信じるとして、最小値は数pFあるはずです。

また、浮遊容量も数pF加わっています。

実際は実験してみるのが早いのですが、ここでは一応設計してみます。

Fmax=5.4MHz、Fmin=5.1MHz、VC=30pFとするとC=248pFとなりました。

30pFも可変範囲があるとは思えませんので、VC=20pFとすると、C=165pFです。

この範囲の中に正解があるはずです。

VCの容量を正確に測定してみれば参考になりますが、測定条件や実装状態によってぶれますので、今後の課題とします。

今回は、C=165pFから浮遊容量10pFを差し引いて155pFで実験してみます。

手持ちのスチコンの組み合わせで33+120pFです。

LはC=165+20pF/F=5.1MHzからL=5.26uH。T-37-6コア(AL=3.0nH/t^2)を使うので、N=√(L/AL)から42Tとなりました。

このパラメタで実際に回路を組んで測定してみました。

F=5.6~6.0MHzとなり、Cが足りません。

手持ちのスチコンの関係で、Cはそのままとして、Lを増やして45Tとしました。

VCのトリマを調整して、5.095~5.420MHzとしました。

この回路図は水魚堂さんの「回路図エディタ BSch3V」で書きました。

水魚堂さんありがとうございました。

作成した基板です。

横から見たところです。

このあとトロイダルコアとスチコンをエポキシで固めて、プリント基板でシールドケースを作成して完成の予定です。

出力は9dBmでした。

今度中をよく見せてください。

と思ったけど既に蓋されているようですね。

次回持って行こうと思います。

安定度を測定しましたが、思わしくないので、

スチコンを黒頭セラミックに交換しました。

エポキシで固めた後の交換なので、外科手術が

大変でした。結構安定してます。

今、VFO2号機の実験中で、今度はクラップです。

2号機はエアVC+エアTC+黒頭セラ+空芯コイル

で安定度を追求しています。

私はまだ使ったことがありません。

クロ頭のNP0は、スチコンよりFBのようですね。

座学先行でOZJにVFOを作るときの電圧と温度のことを質問したことがあるのですが、OZJは、3V-5V位がVFOで温度とのかねあいで扱い安いと言っていたのを記憶してます。FETだか2SCだったか何の素子を前提でいったのか、酒の席でもあり、肝心なところを忘れてしまっておりますが。。(汗)

でもやはり実験ですね。次回楽しみにしています。