またまた、50MHz AMトランシーバを作ることにします。

何台目でしょうか。

今回は周波数可変としますので、周波数構成が悩ましいです。

周波数可変とするにはVXOかVFOにする必要があります。

PLLは昨年作ったので、今回はVXOと局発に使用できそうな水晶を捜してみました。

VXO用として31.66MHzのセラロックと19.069MHzの水晶が見つかりましたので、この構成で行こうと思います。

周波数構成です。

31.66のセラロックを下に200kHzほど可変できれば50.5~50.7MHzをカバーできそうです。

送信部は19.069MHzと混合した後、DBMでDCを加えて変調します。

受信部は周波数変換後、3素子くらいのラダーフィルターを経由して2段のIF増幅後、検波、AFアンプという予定です。

今回はVXOの可変範囲が取れるかどうかが肝なので、VXOを試作してみました。

回路図です。

バリキャップをDAコンバーターで制御しようかとも思いましたが、今回はシンプルにバリコンにしました。

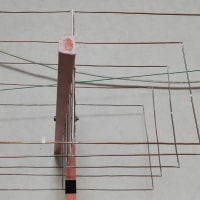

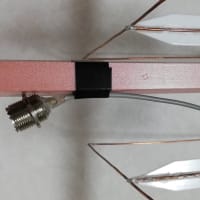

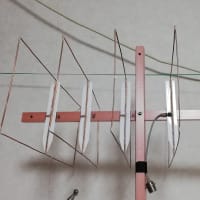

試作した実験基板です。

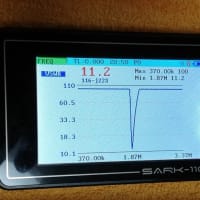

VXO用コイルを3.3μHとしてみたところ31.378~31.658MHzまで可変できました。

計画通りに行けそうです。

何台目でしょうか。

今回は周波数可変としますので、周波数構成が悩ましいです。

周波数可変とするにはVXOかVFOにする必要があります。

PLLは昨年作ったので、今回はVXOと局発に使用できそうな水晶を捜してみました。

VXO用として31.66MHzのセラロックと19.069MHzの水晶が見つかりましたので、この構成で行こうと思います。

周波数構成です。

31.66のセラロックを下に200kHzほど可変できれば50.5~50.7MHzをカバーできそうです。

送信部は19.069MHzと混合した後、DBMでDCを加えて変調します。

受信部は周波数変換後、3素子くらいのラダーフィルターを経由して2段のIF増幅後、検波、AFアンプという予定です。

今回はVXOの可変範囲が取れるかどうかが肝なので、VXOを試作してみました。

回路図です。

バリキャップをDAコンバーターで制御しようかとも思いましたが、今回はシンプルにバリコンにしました。

試作した実験基板です。

VXO用コイルを3.3μHとしてみたところ31.378~31.658MHzまで可変できました。

計画通りに行けそうです。

※コメント投稿者のブログIDはブログ作成者のみに通知されます