US9846583(XILINX INC [US])

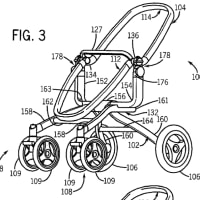

[0038] FIG. 3 is a block diagram depicting the PMU 122 according to an example. The PMU 122 includes a plurality of redundant subsystems 302 , ROM 312 , RAM 314 , and other components described below.

【0029】

図3は、一実施例に係るPMU122を示すブロック図である。PMU122は、複数の冗長サブシステム302と、ROM312と、RAM314と、以下に説明されるその他のコンポーネントとを含む。

Each of the redundant subsystems 302 includes a CPU 304 , a ROM arbiter 306 , and a RAM arbiter 308 .

各冗長サブシステム302は、CPU304と、ROMアービタ306と、RAMアービタ308とを含む。

The redundant subsystems 302 are coupled to voters 310 .

冗長サブシステム302は、多数決回路(voter)310に接続されている。

The voters 310 are configured to compare the outputs of the redundant subsystems 302 and determine the “correct output”.

多数決回路310は、冗長サブシステム302の出力を比較し、「正しい出力」を判定するよう構成されている。

For example, if two redundant subsystems 302 output a first value for a given transaction

例えば、2つの冗長サブシステム302が、所定の処理に関して第1の値を出力する場合、

and one redundant subsystem 302 outputs a second value different than the first value,

1つの冗長サブシステム302が第1値とは異なる第2の値を出力すると、

the voters 310 can select the first value as the output.

多数決回路310は、第1値を出力として選択することが可能である。

US10055316(VAREX IMAGING CORP [US])

[0064] In another example, the voting logic module compares the control signals on the at least three control lines and generates an output based on a majority of congruent control signals.

【0048】

別の例においては、多数決論理モジュールは、少なくとも3本の制御線の制御信号を比較し、過半数の一致した制御信号に基づいて出力を生成する。

The voting logic module can include a two out of three (TOOT) voting circuit, a three out of four (TOOF) voting circuit, or a two out of four voting circuit.

多数決論理モジュールは、2 out of 3(TOOT)多数決回路、3 out of 4(TOOF)多数決回路、または、2 out of 4多数決回路を含んでよい。

US9467153(FINISAR CORP [US])

[0030] The conventional digital phase-locked loop illustrated in FIG. 2 allows the digital filter 206 to be implemented without external components, an advantage when compared to the conventional analog phase-locked loop 100 illustrated in FIG. 1.

図2に図示する従来のデジタル位相同期ループは外部コンポーネントなしでデジタルフィルタ206を実装でき、図1に図示する従来のアナログ位相同期ループ100と比較したときの利点である。

The architecture described with reference to FIG. 2 requires components such as adders and DAC that operate at very high clock rate.

図2を参照して説明するアーキテクチャは、非常に高いクロックレートで動作する加算器およびDACなどのコンポーネントを必要とする。

Operating adders and DAC at a high clock rate may translate to high power dissipation.

高クロックレートで加算器およびDACを動作させることは、高消費電力と言い換えることができる。

Solutions have been designed to operate these and other components at a lower clock rate.

より低いクロックレートでこれらのコンポーネントや他のコンポーネントを動作させるためのソリューションが構成されてきた。

One particular solution has been described in P. K. Hanumolu, et al., “A 1.6 Gbps Digital CDR.” IEEE Custom Integrated Circuits Conference (2006) 603-606, which employs demultiplexing and majority vote circuits.

ある具体的なソリューションが、ピー・ケー・ハヌモルら(P.K. Hanumolu, et al.)、A 1.6 Gbps Digital CDR、IEEE Custom Integrated Circuits Conference、603~606ページ(2006年)に記述されており、これは多重分離および多数決回路を採用する。

However, the demultiplexing and majority vote circuits still require many latches and adders, which may occupy a larger area and dissipate more power than the embodiments described herein.

しかし、多重分離および多数決回路にはまだ多くのラッチや加算器が必要で、本書で説明する実施形態よりも大きな面積を占め、多くの電力を消費する。

US8472130( IBM [US])

[0034] Referring to FIG. 3, while continuing to refer generally to FIG. 2, although VFO-like patterns 502 are detected at various locations in each of a group of four tracks, the VFO-detection flag is only raised if a specified number of VFO-like patterns 502 occur simultaneously in the four tracks.

【0025】

図2への全体的な参照を続けながら図3を参照すると、VFO様パターン502が4本トラックのグループ各々のさまざまな位置で検出されているが、VFO検出フラグは、4本のトラックで、規定数のVFO様パターン502が同時に現れた場合にだけ揚げられる。

Since only a single VFO-like pattern 502 occurs at any given time, the VFO voting circuitry will not raise the VFO-detection flag, as shown in FIG. 3.

図3に示されるように、どの所与の時間においても一つだけのVFO様パターン502が現れているので、VFO多数決回路はVFO検出フラグを揚げないことになる。

This contrasts with actual VFO patterns 506 which are aligned across the several tracks.

これは、本当のVFOパターン506がいくつかのトラックに亘って整列されているのと対照的である。

As shown in FIG. 3, the voting-logic circuitry raises the VFO-detection flag since a specified number of VFO patterns 506 are detected in the same along-track location.

図3に示されるように、同一のトラック沿い位置に規定数のVFOパターン506が検出されたので、多数決論理回路はVFO検出フラグを揚げている。

US8963579(INTEL CORP [US])

[0040] In another aspect of the present invention, a majority gate is included in a logic circuit.

本発明の他の一態様において、多数決回路が論理回路に含められる。

FIG. 6 illustrates a plan view of a portion of a majority gate, in accordance with an embodiment of the present invention.

図6は、本発明の一実施形態に係る多数決ゲートの一部の平面図を示している。

/////////

[0042] In another aspect of the present invention, several majority gates are included in a logic circuit.

本発明の他の一態様において、幾つかの多数決回路が論理回路に含められる。

FIG. 7 illustrates a plan view of a 1 bit stage of a full carry adder, in accordance with an embodiment of the present invention.

図7は、本発明の一実施形態に係る全(フルキャリー)加算器の1ビット段(ステージ)の平面図を示している。

US2007260939(HONEYWELL INT INC [US])

The TMR voter circuit identifies if an FPGA has been subjected to a single event upset (SEU) error.

TMRボータ回路(TMR多数決回路)は、FPGAがシングル・イベント・アプセット(SEU)・エラーを起こしたかどうか識別する。

Each time an SEU error event is detected, the FPGA is normally taken offline and reconfigured.

SEUエラー・イベントが検出される度に、FPGAは、通常、オフラインにされて再コンフィギュレーションされる。

US7372763(INTEL CORP [US])

FIG. 3 shows a majority voting circuit 300 in accordance with some embodiments, which may be used to spatially encode data for a memory as disclosed herein.

図3は、一部の実施形態に従った多数決回路300を示しており、この回路はここで開示されたようなメモリでデータを空間符号化するために用いられ得る。

The majority voting circuit 300 comprises first and second digitally-controlled variable delay elements 302A, 302B coupled to an edge-triggered latch 304.

多数決回路300は、エッジトリガー式ラッチ304に結合された第1及び第2のデジタル制御の可変遅延素子302A、302Bを有している。

Both delay elements 302A, 302B have a common clock signal (CLK) applied at their inputs, and their outputs are coupled to inputs of the edge-triggered latch 304.

何れの遅延素子302A、302Bも、それらの入力に与えられる共通のクロック信号(CLK)を有しており、それらの出力はエッジトリガー式ラッチ304の入力に

※コメント投稿者のブログIDはブログ作成者のみに通知されます