ATmega88にテトリスを書き込んで見ました。

まだ、JOYスティックがついていませんが、取りあえず画面は出ました。

R-2RDACの配線を間違えて、同じ配線の繰り返しはどうもいけません。どう間違えたのか

なかなか見つかりません。

何とか見つけてOK。

画像をよく見ると左右にじわじわ揺れています。内蔵RCのジッタ?かハムってるのか?

明日、プシュSWを付けて見ます。

FMラジオ製作(2)

2週間前

FMラジオ製作(2)

2週間前

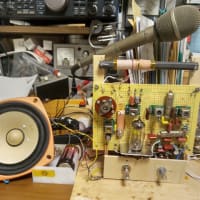

今度はFMラジオ

3週間前

今度はFMラジオ

3週間前

My favorite Radio 出来ました

2ヶ月前

My favorite Radio 出来ました

2ヶ月前

またまたラジオつくり

3ヶ月前

またまたラジオつくり

3ヶ月前

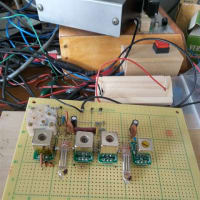

DC-DC Converter

4ヶ月前

DC-DC Converter

4ヶ月前

またラジオtづくってます(2)

5ヶ月前

またラジオtづくってます(2)

5ヶ月前

またラジオを作ってます

5ヶ月前

またラジオを作ってます

5ヶ月前

梅の花

6ヶ月前

梅の花

6ヶ月前

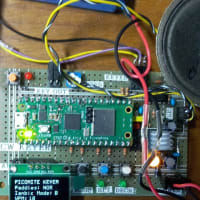

Raspberry Pi Picoでエレキーヤー

8ヶ月前

Raspberry Pi Picoでエレキーヤー

8ヶ月前

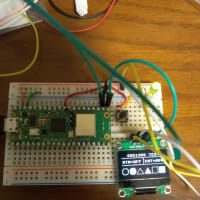

Raspberry Pi Pico W

8ヶ月前

Raspberry Pi Pico W

8ヶ月前

さすがですね。早速動作確認を行われた行動力に

敬意を表します。

画面表示の揺らぎは、以前、RC発振でTVに表示させた

ときにも経験しました。仕方なく、8MHzのセラロック

を追加しました。

RC発振の揺らぎが無いかどうかを確認してみる必要が

あります。ATmega644pならセラロックやXtalが使える

ので、それと比較してみるのも一案です。

低減させるために意図的にこうした仕様になっている、

という説がありますが、定かではありません。

私は、安定している方が嬉しいのですが、それ程単純な

ものでは無いようです。

画像を比較しますと、ジッタは有りません。やはり、内部RC発振器の影響かも?

mega88の画像は少しボケ気味かな?

兎に角、差異が認められますね。

http://elm-chan.org/docs/avr/jitter.html

結局テストはしていませんが・・・

ないようです。

昨年FPGA(というかASIC)のエッセイ本を読んでいたら、

書いていました。

ところで、ラジオ少年さん、流石です。

私は、木曜日は子供が、保育所の都合で休みだった

ので全然触れず(涙;)。

金曜は、できればmbedに移植してみます。

できるかどうかはわかりませんけど(例のSPI

のDACを使う予定です)

思います。

TVのクロマで3.58MHzのRC発振が使えるかと言うと使用出来ないでしょう。RC発振を使用すれば、ビ-トの縞模様が出ると私は、思います。

私が先に紹介したChaNさんのリポートは読みましたか?

http://elm-chan.org/docs/avr/jitter.html

読んだ上での発言とは思えません。

を読むと、世代が古いほうが安定しています。mega88ではなく、

mega8はRC発振の特性が異なることを思い出しました。

mega8に置き換えてみてはいかがでしょうか。

の付録ジャパニーノは、内蔵のRCを使っていて(外部

発振子もあるのに)、MTM05(だったか?)用にビデオ

コンポジット出力が滲むってことで話題になりました。

Mega88Vでしたか・・。

読みました。

積極的に、RCにしたと書いて有ったかも知れません。良く読み返してみます。