PetalinuxへのAXI UART Liteの追加手順がZYBOで確認できたので、

同じようにZedBoard+AD-FMCOMMS3にも追加してみます。

ターゲットのHDLはすでにビルド済みなので、これをベースに改修していきます。

https://blog.goo.ne.jp/osqzss/e/160e3ff2c3de95c1b96d0855deea759d

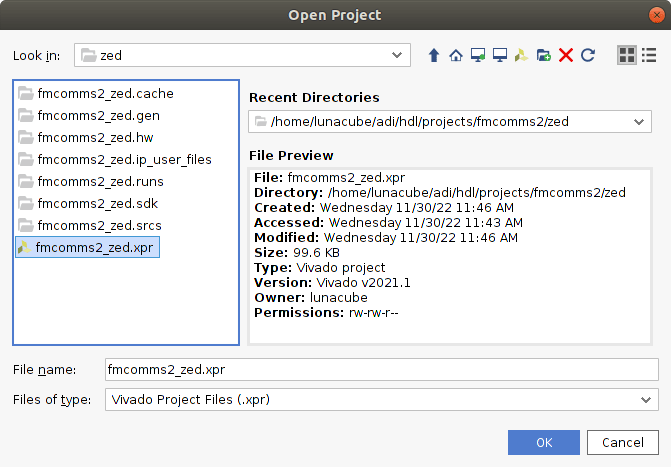

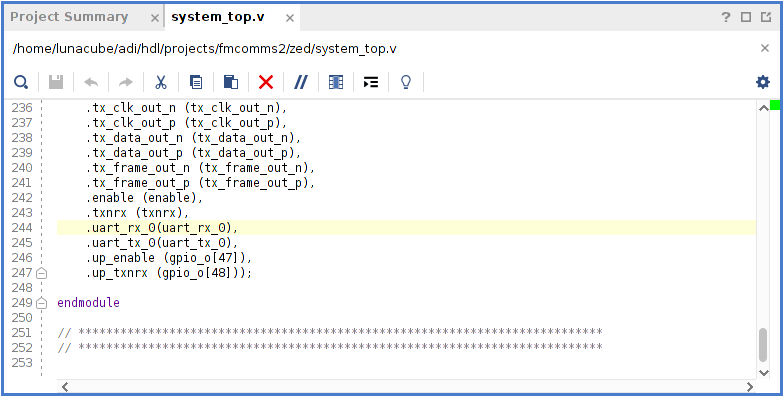

projects/fmcomms2/zedのフォルダから、Vivadoのプロジェクトファイルをopenします。

Block Designを開き、AXI UART Liteを追加します。

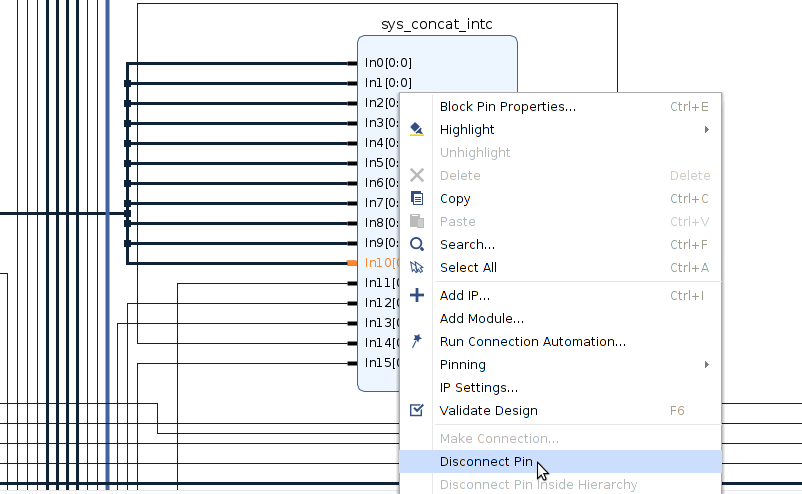

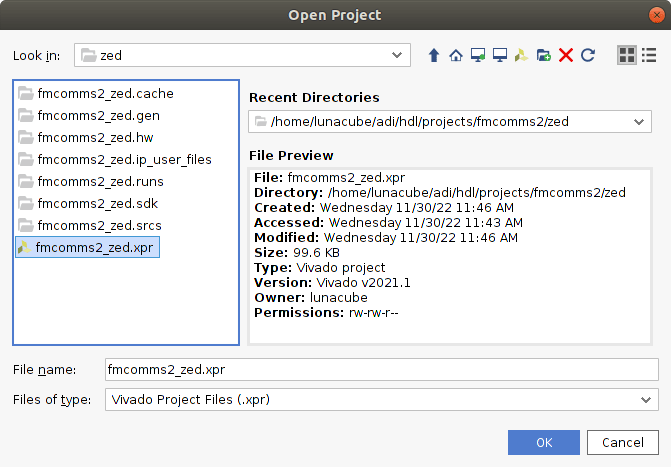

PLからPSへのinterruptは、Concatというブロックを経由しています。

まずはすでにGNDに接続されているIn10[0:0]を右クリックし、"Disconnect Pin"でピンをリリースします。

その後、In10[0:0]をAXI UART Liteのinterruptに接続します。

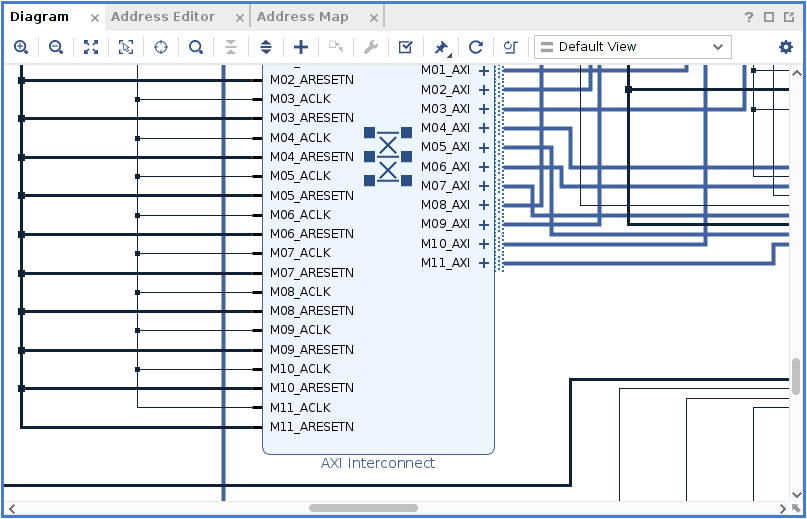

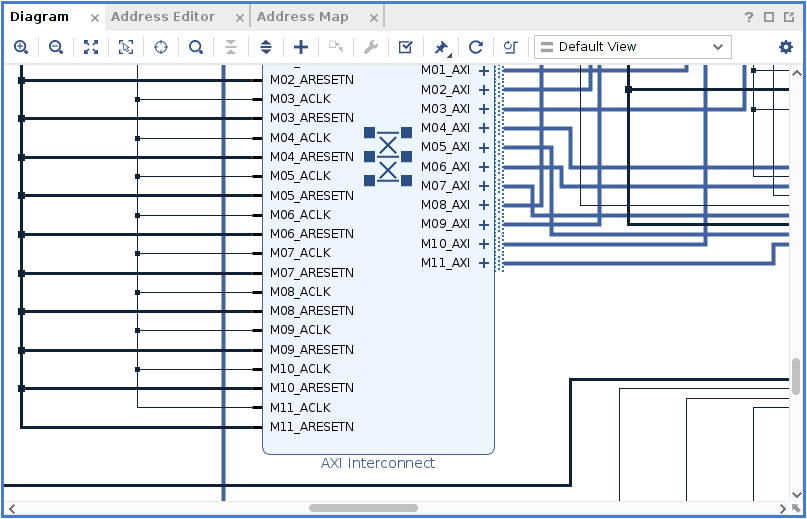

次に、AXI InterconnectにM11_AXIを追加し、それをAXI UART LiteのS_AXIと接続します。

後は、AXI UART Liteのs_axi_aclkとs_axi_aresetnを、それぞれsys_cpu_clkとsys_cpu_resetnに接続し、

rxとtxを外部に引き出します。

最後に、Address Editorのタブを開き、/axi_uartlite_0/S_AXIのアドレスをアサインします。

これで、Block Designの改修は完了。Validate Designをしてから、Create HDL Wrapperを実行します。

しかし、wrapperは生成されているようですが、"Existing Wrapper File"の警告が出て、wrapperファイルが

アップデートされません。調べてみると、Tclスクリプトで生成されたプロジェクトでは、wrapperファイルが

fmcomms2_zed.srcs/sources_1/imports/hdlから読み込まれていますが、Create HDL Wrapperは

fmcomms2_zed.gen/sources_1/bd/system/hdlにwrapperを生成しているようです。

https://support.xilinx.com/s/question/0D52E00006hpmAYSAY/wrapper-doesnt-update-when-changing-a-block-diagram

そこで、オリジナルのwrapperファイルをRemove File from Projectで、プロジェクトから削除します。

そうすると、Vivadoが自動的に階層構造をupdateして、fmcomms2_zed.gen/sources_1/bd/system/hdlの

wrapperファイルを選択してくれます。

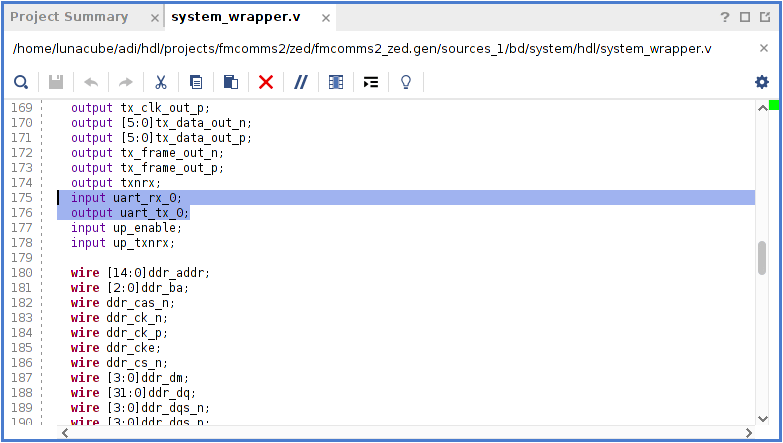

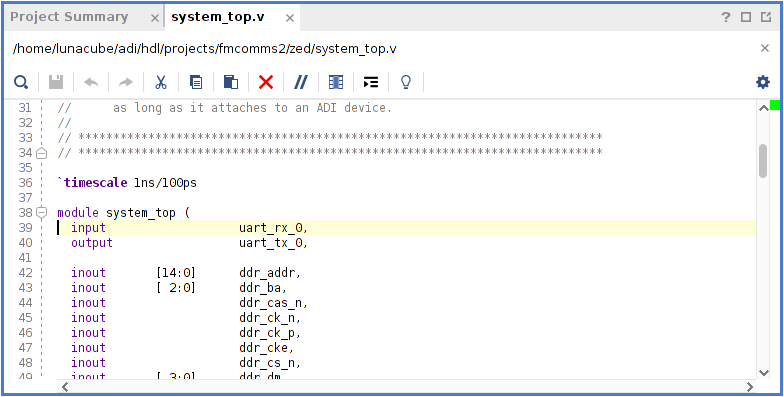

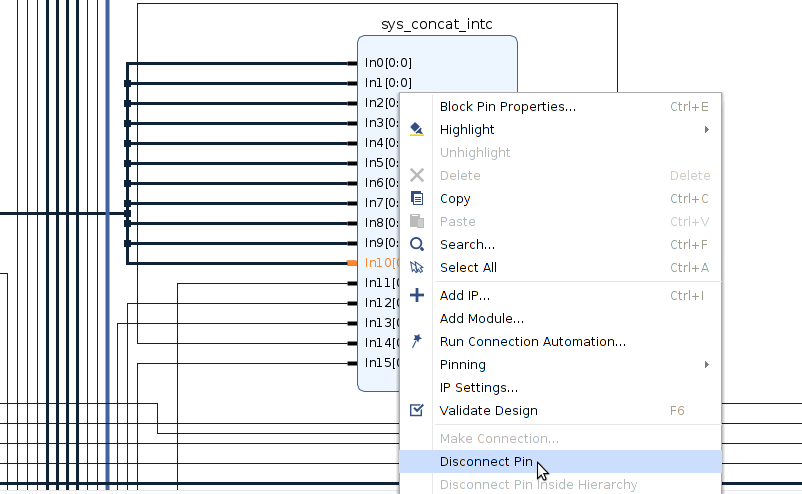

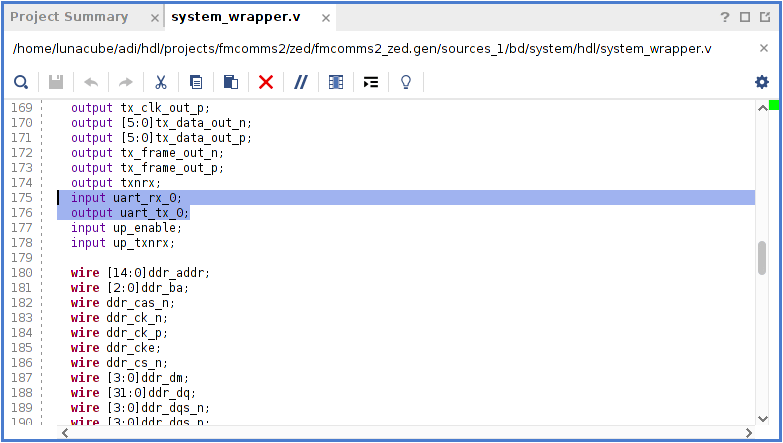

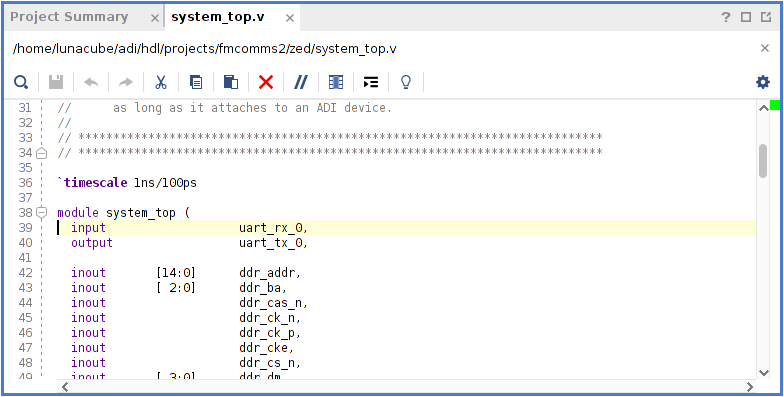

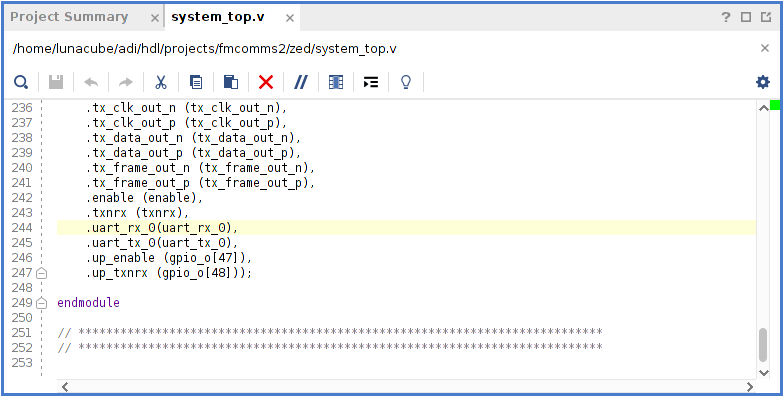

これで、system_wrapper.vにAXI UART Liteのポートが追加されたので、上位階層であるsystem_top.vも

適切に編集します。

最後にピンをアサインして、新しいxsaファイルを生成します。

さて、これでハードウェアの準備は整いました。Petalinuxのビルドは年明けかな。

同じようにZedBoard+AD-FMCOMMS3にも追加してみます。

ターゲットのHDLはすでにビルド済みなので、これをベースに改修していきます。

https://blog.goo.ne.jp/osqzss/e/160e3ff2c3de95c1b96d0855deea759d

projects/fmcomms2/zedのフォルダから、Vivadoのプロジェクトファイルをopenします。

Block Designを開き、AXI UART Liteを追加します。

PLからPSへのinterruptは、Concatというブロックを経由しています。

まずはすでにGNDに接続されているIn10[0:0]を右クリックし、"Disconnect Pin"でピンをリリースします。

その後、In10[0:0]をAXI UART Liteのinterruptに接続します。

次に、AXI InterconnectにM11_AXIを追加し、それをAXI UART LiteのS_AXIと接続します。

後は、AXI UART Liteのs_axi_aclkとs_axi_aresetnを、それぞれsys_cpu_clkとsys_cpu_resetnに接続し、

rxとtxを外部に引き出します。

最後に、Address Editorのタブを開き、/axi_uartlite_0/S_AXIのアドレスをアサインします。

これで、Block Designの改修は完了。Validate Designをしてから、Create HDL Wrapperを実行します。

しかし、wrapperは生成されているようですが、"Existing Wrapper File"の警告が出て、wrapperファイルが

アップデートされません。調べてみると、Tclスクリプトで生成されたプロジェクトでは、wrapperファイルが

fmcomms2_zed.srcs/sources_1/imports/hdlから読み込まれていますが、Create HDL Wrapperは

fmcomms2_zed.gen/sources_1/bd/system/hdlにwrapperを生成しているようです。

https://support.xilinx.com/s/question/0D52E00006hpmAYSAY/wrapper-doesnt-update-when-changing-a-block-diagram

そこで、オリジナルのwrapperファイルをRemove File from Projectで、プロジェクトから削除します。

そうすると、Vivadoが自動的に階層構造をupdateして、fmcomms2_zed.gen/sources_1/bd/system/hdlの

wrapperファイルを選択してくれます。

これで、system_wrapper.vにAXI UART Liteのポートが追加されたので、上位階層であるsystem_top.vも

適切に編集します。

最後にピンをアサインして、新しいxsaファイルを生成します。

さて、これでハードウェアの準備は整いました。Petalinuxのビルドは年明けかな。

※コメント投稿者のブログIDはブログ作成者のみに通知されます