Namuru-Nanoでは、IF信号をサンプリングするクロックを6逓倍して

システムクロックとし、サンプリングクロックはenable信号にするという

少しトリッキーな実装をしています。

これは、オリジナルのNamaruのコードをできるだけ変更しないための

苦肉の策ですが、とりあえずこのままポートします。

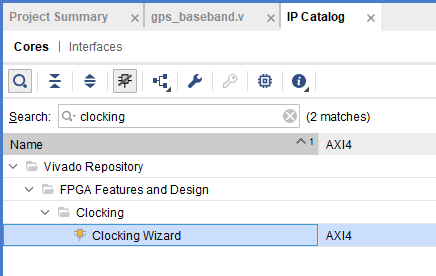

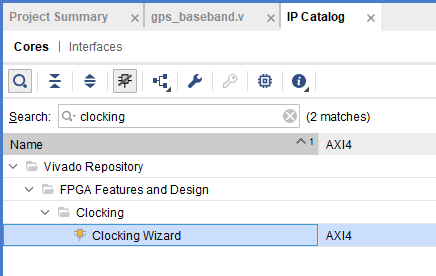

Namuru-Nanoでは、システムクロックの生成にNios IIのPLLを使っていましたが、

ZynqではClocking Wizardを使って、MMCMを追加します。

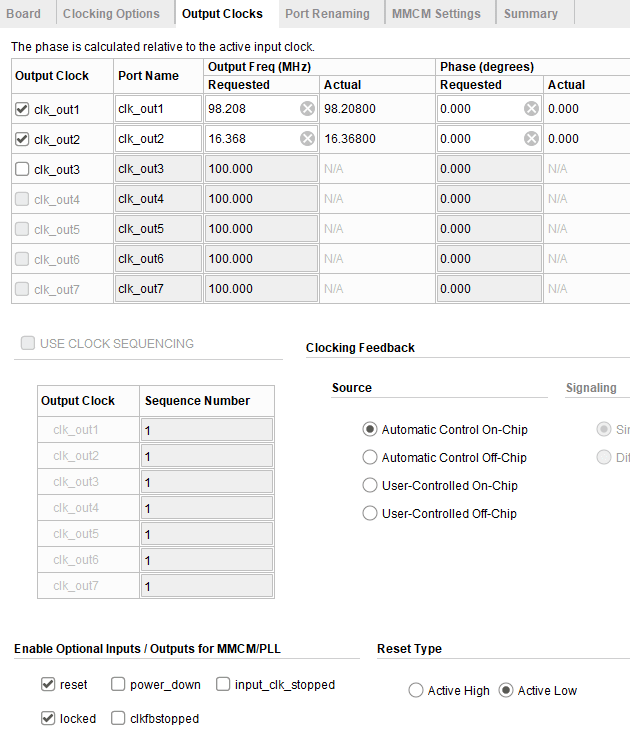

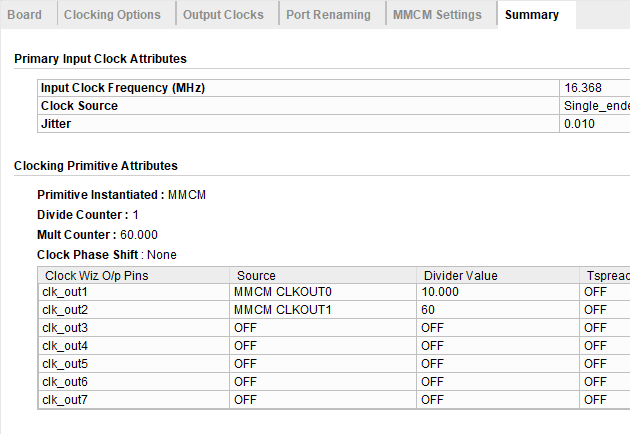

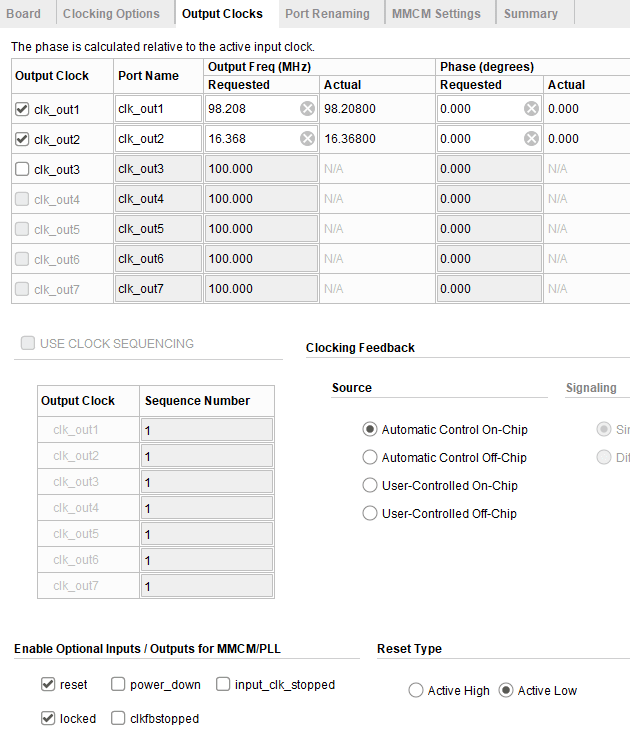

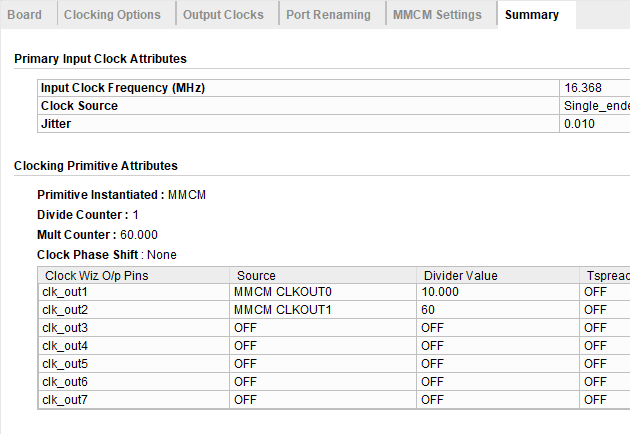

クロック入力の周波数は、とりあえずNamuru-Nanoと同じ16.368MHzとし、

それを6逓倍した90.208MHzのシステムクロックと、そのままのenable信号を

出力します。

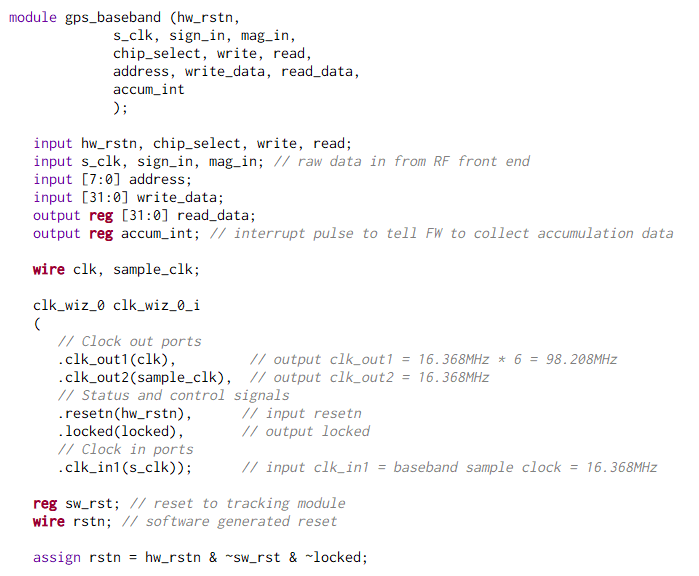

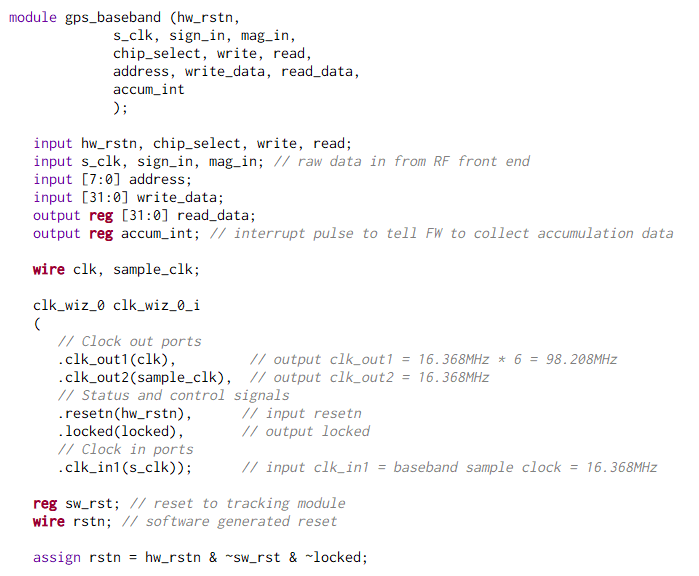

生成されたIPコアは、トップモジュールに組み込みます。

フロントエンドから供給されるサンプリング信号s_clkを入力とし、

システムクロックのclkと、enable信号のsample_clkを出力します。

MMCMのlocked信号も、basebandモジュールのリセット信号に追加しています。

次は、basebandモジュールをIP化して、AXIバスに繋げよう。

システムクロックとし、サンプリングクロックはenable信号にするという

少しトリッキーな実装をしています。

これは、オリジナルのNamaruのコードをできるだけ変更しないための

苦肉の策ですが、とりあえずこのままポートします。

Namuru-Nanoでは、システムクロックの生成にNios IIのPLLを使っていましたが、

ZynqではClocking Wizardを使って、MMCMを追加します。

クロック入力の周波数は、とりあえずNamuru-Nanoと同じ16.368MHzとし、

それを6逓倍した90.208MHzのシステムクロックと、そのままのenable信号を

出力します。

生成されたIPコアは、トップモジュールに組み込みます。

フロントエンドから供給されるサンプリング信号s_clkを入力とし、

システムクロックのclkと、enable信号のsample_clkを出力します。

MMCMのlocked信号も、basebandモジュールのリセット信号に追加しています。

次は、basebandモジュールをIP化して、AXIバスに繋げよう。

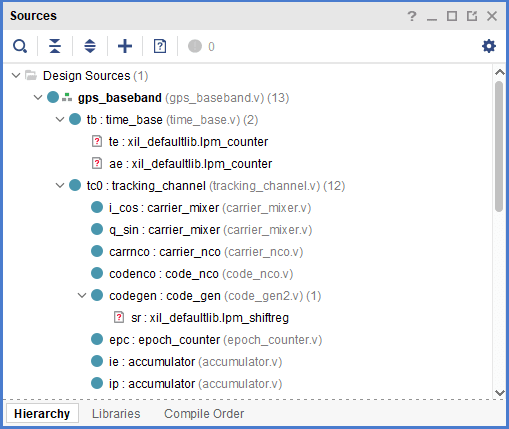

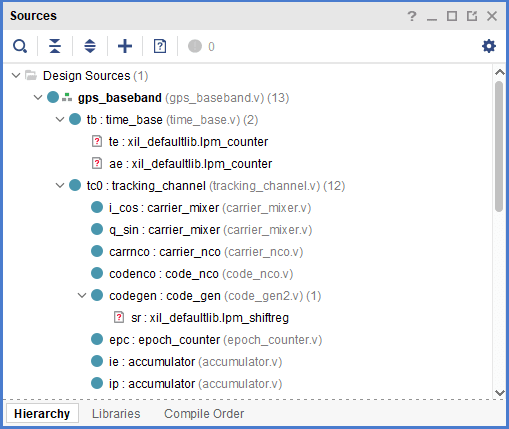

Namuru-NanoのbasebandのHDLをVivadoで合成してみると、当然、

AlteraのIPであるlpm_counterとlpm_shiftregが未定義とエラーが出ます。

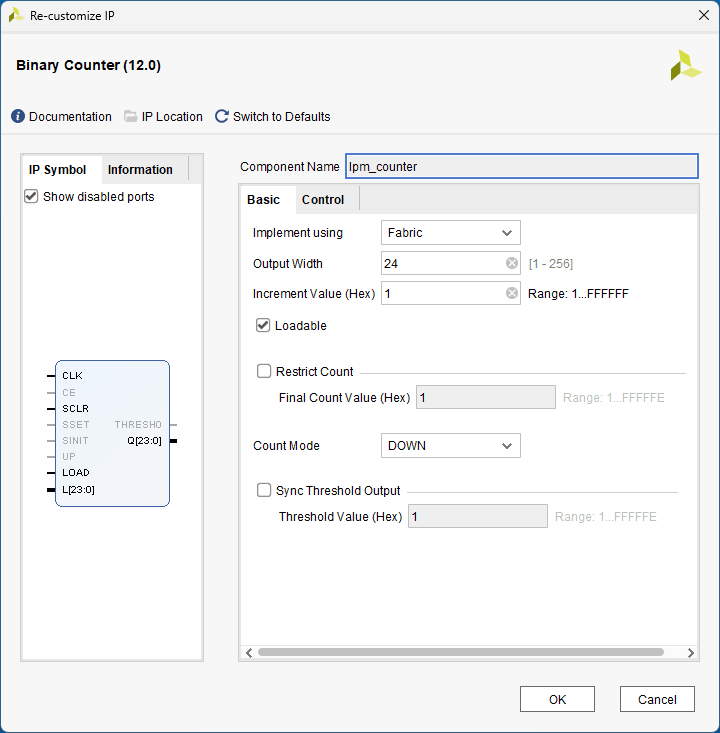

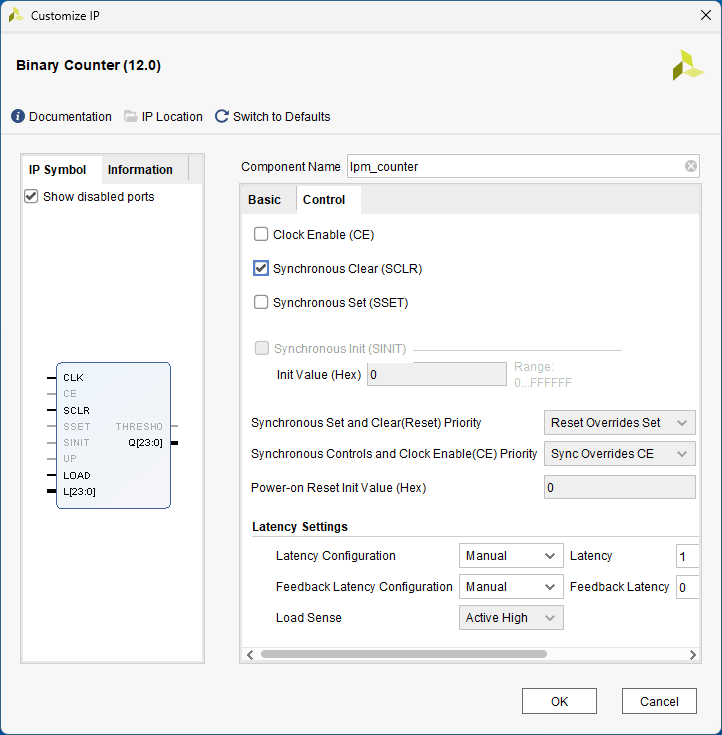

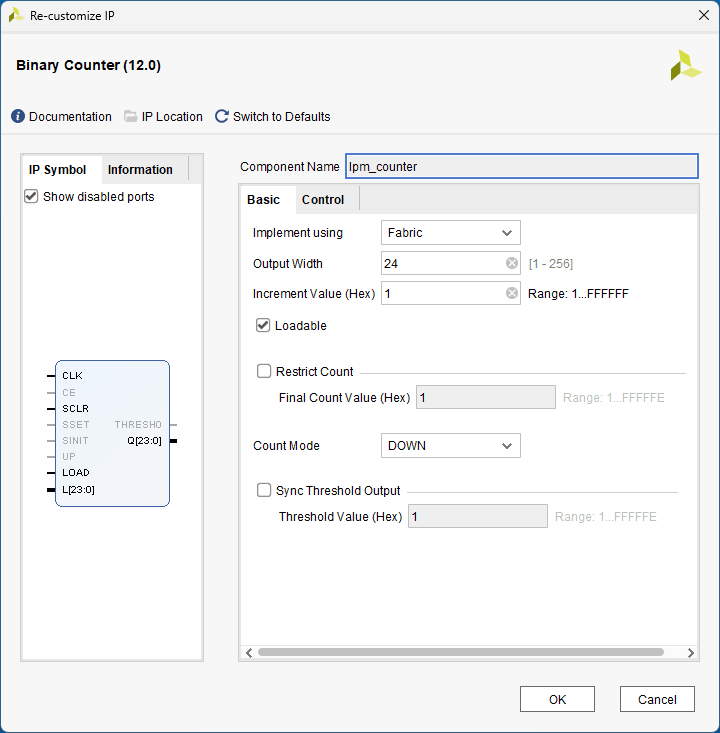

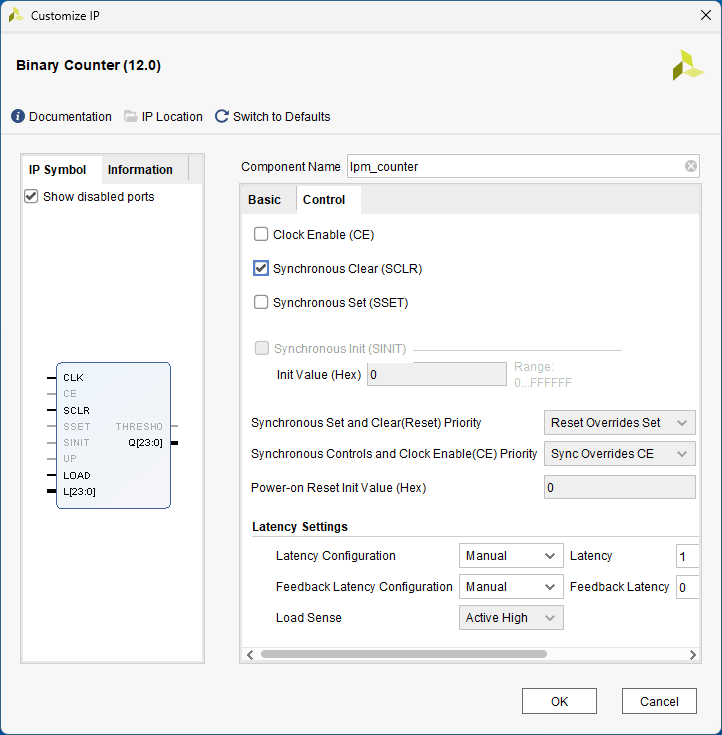

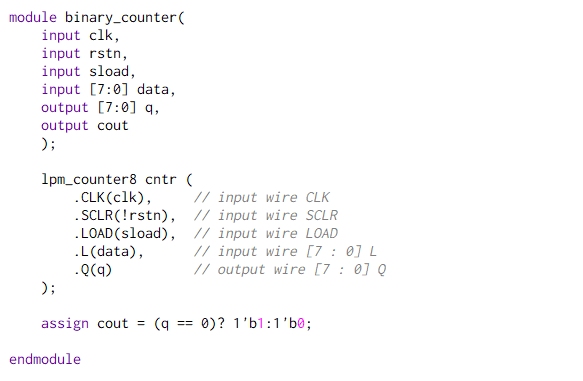

lpm_counterは、Xilinx LogiCORE IPのbinary counterに置き換えられそうでしたので、

VivadoのIPカタログからbinary counterを開き、各種パラメータを設定します。

VivadoでのIPコアの使いかたは、こちらを参考にしました。

ACRi:FPGA をもっと活用するために IP コアを使ってみよう (2)

Binary CounterのComponent Nameは、Altera IPと同じlpm_counterにします。

Output Widthは24ビット、Loadableを有効にし、Count ModeはDOWNです。

Synchronous Clearも有効にします。

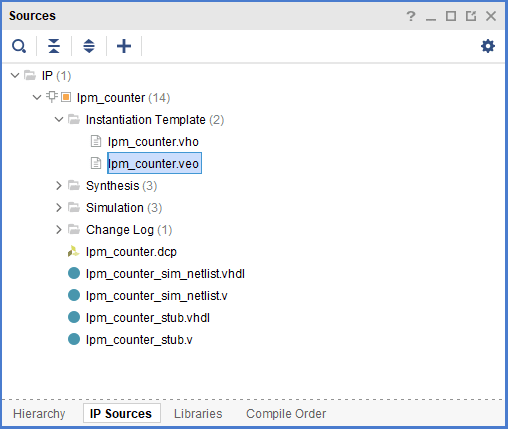

設定ダイアログのOKをクリックして閉じると、Generate Output Productsの

ダイアログが開きます。GenerateをクリックしてIPコアを合成します。

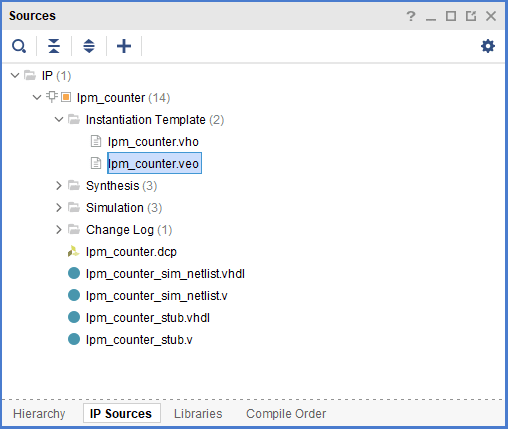

IPコアのモジュールが準備できたら、SourcesペインのIP Sourcesタブから、

テンプレートファイル(.veo)を開きます。

このインスタンス生成のテンプレートを、もとのソースコードにコピーして、

入出力ポートの信号を接続します。

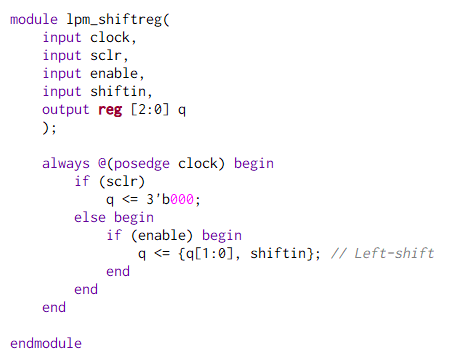

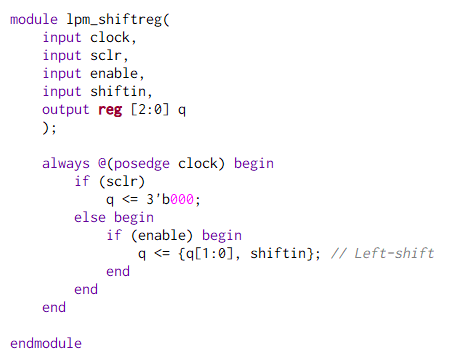

一方、lpm_shiftregは、ちょうど置き換えれるようなIPが見当たりません。

そのため、こちらはモジュールのHDLコードを追加します。

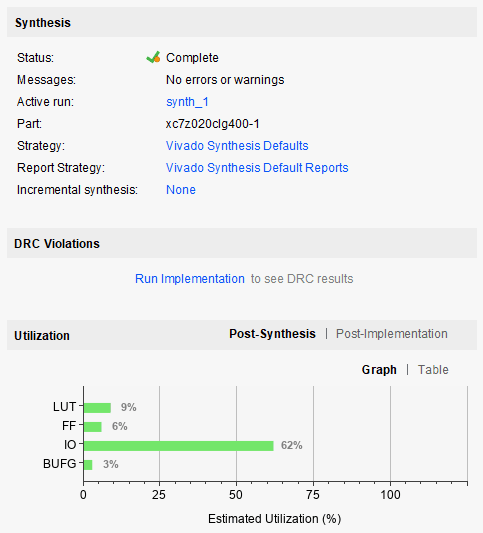

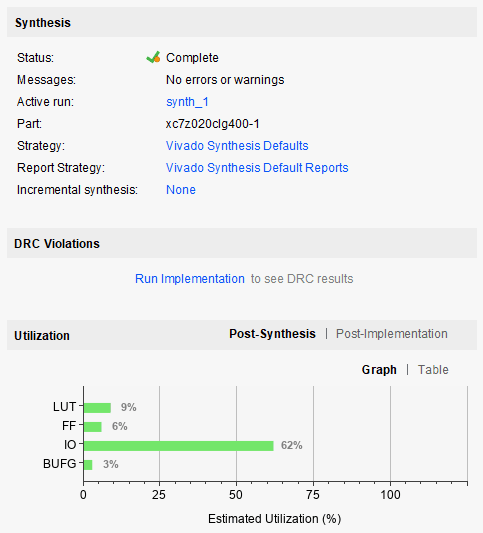

これで、Run Synthesisを実行すると、errorもwarningもなしで、合成が完了します。

P.S. Binary Counterの設定画面を見ると、Final Count Valueが1からFFFFFEまでしか選べません。

0までカウントダウンしてくれないのでしょうか?それとも、Restrict Countを有効にしなければ、

0またはFFFFFFがFinal Count Valueになるのでしょうか?別途、テストベンチを組んで確かめよう。

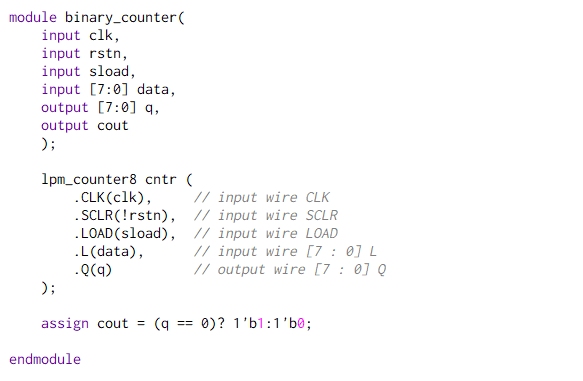

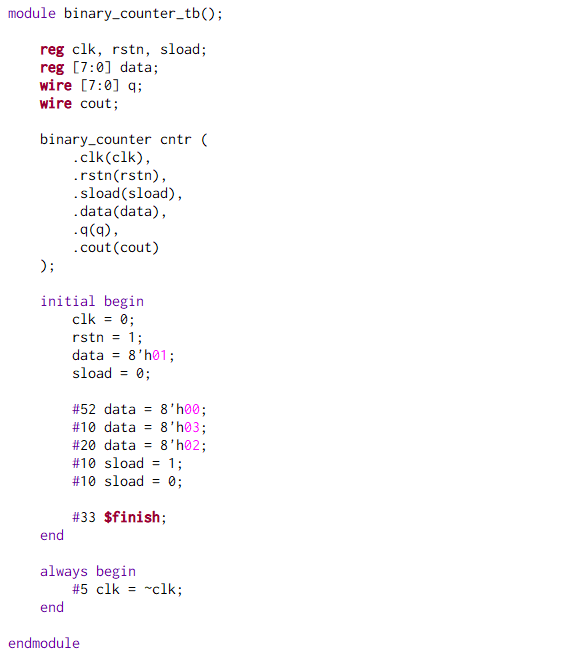

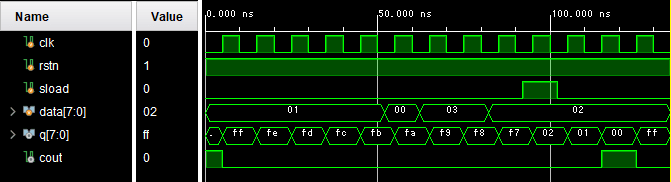

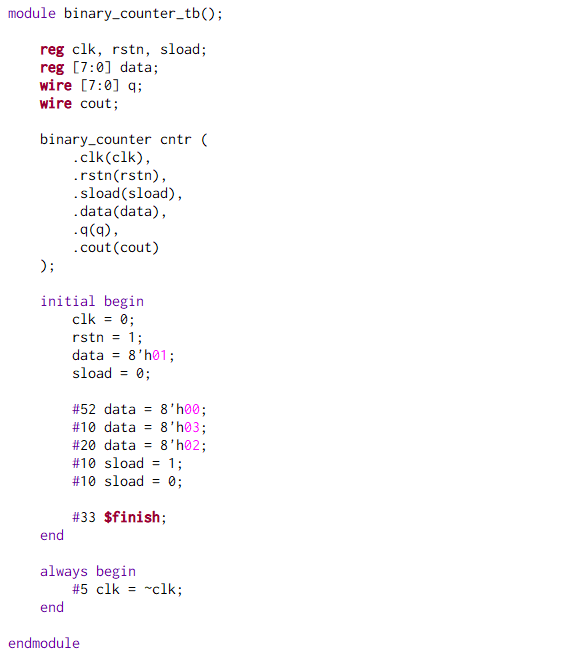

P.P.S. 8ビットのBinary Counterを作成して、テストベンチで動作を確認してみました。

lpm_counterと同様に、loadされた値から0までカウントダウンしてくれるようです。

AlteraのIPであるlpm_counterとlpm_shiftregが未定義とエラーが出ます。

lpm_counterは、Xilinx LogiCORE IPのbinary counterに置き換えられそうでしたので、

VivadoのIPカタログからbinary counterを開き、各種パラメータを設定します。

VivadoでのIPコアの使いかたは、こちらを参考にしました。

ACRi:FPGA をもっと活用するために IP コアを使ってみよう (2)

Binary CounterのComponent Nameは、Altera IPと同じlpm_counterにします。

Output Widthは24ビット、Loadableを有効にし、Count ModeはDOWNです。

Synchronous Clearも有効にします。

設定ダイアログのOKをクリックして閉じると、Generate Output Productsの

ダイアログが開きます。GenerateをクリックしてIPコアを合成します。

IPコアのモジュールが準備できたら、SourcesペインのIP Sourcesタブから、

テンプレートファイル(.veo)を開きます。

このインスタンス生成のテンプレートを、もとのソースコードにコピーして、

入出力ポートの信号を接続します。

一方、lpm_shiftregは、ちょうど置き換えれるようなIPが見当たりません。

そのため、こちらはモジュールのHDLコードを追加します。

これで、Run Synthesisを実行すると、errorもwarningもなしで、合成が完了します。

P.S. Binary Counterの設定画面を見ると、Final Count Valueが1からFFFFFEまでしか選べません。

0までカウントダウンしてくれないのでしょうか?それとも、Restrict Countを有効にしなければ、

0またはFFFFFFがFinal Count Valueになるのでしょうか?別途、テストベンチを組んで確かめよう。

P.P.S. 8ビットのBinary Counterを作成して、テストベンチで動作を確認してみました。

lpm_counterと同様に、loadされた値から0までカウントダウンしてくれるようです。

10年以上も前に、NamuruのHDLコードをAlteraのDE0-Nano+MAX2771の

組み合わせに移植しています。

https://blog.goo.ne.jp/osqzss/e/e088b635bc33084117b7e9606316a569

すっかり放置しており、細かなところを忘れていますが、HDLに関しては

ほぼこのままZynqベースのPocketGNSSに移植できるかと思います。

CPUがソフトコアのNios IIから、Zynq内蔵のARMに変わりますので、

バス回りは調整が必要です。FPGAに実装される相関器が汎用的に使えるよう、

相関器とCPUとのインターフェイスはSPIなどにした方が良いかもしれません。

オリジナルのNamuru-NanoのソースコードをGoogle Driveにソースコードを

アップしましたので、興味のある方は開発に参加してもらえると嬉しいです。

https://drive.google.com/drive/folders/141BSfAa7lHga43nRK0nXX9STol0DK0OE?usp=sharing

組み合わせに移植しています。

https://blog.goo.ne.jp/osqzss/e/e088b635bc33084117b7e9606316a569

すっかり放置しており、細かなところを忘れていますが、HDLに関しては

ほぼこのままZynqベースのPocketGNSSに移植できるかと思います。

CPUがソフトコアのNios IIから、Zynq内蔵のARMに変わりますので、

バス回りは調整が必要です。FPGAに実装される相関器が汎用的に使えるよう、

相関器とCPUとのインターフェイスはSPIなどにした方が良いかもしれません。

オリジナルのNamuru-NanoのソースコードをGoogle Driveにソースコードを

アップしましたので、興味のある方は開発に参加してもらえると嬉しいです。

https://drive.google.com/drive/folders/141BSfAa7lHga43nRK0nXX9STol0DK0OE?usp=sharing

PocketGNSSに実装予定の相関器の構成を示します。

まずは、スタンダードにGPS L1 C/Aコードの相関器を組んで行きます。

ひとつの衛星の信号処理には、この相関器が2つ必要になります。

一方の相関器では、搬送波NCOによって同位相の搬送波レプリカが、

もう一方の相関器では直交位相の搬送波レプリカが生成されます。

P.S. 相関器は、オープンソースのNAMURUをベースに開発します。

DE0-Nanoに移植したのが10年以上前なのね。すっかり忘れている。

https://blog.goo.ne.jp/osqzss/e/e088b635bc33084117b7e9606316a569

まずは、スタンダードにGPS L1 C/Aコードの相関器を組んで行きます。

ひとつの衛星の信号処理には、この相関器が2つ必要になります。

一方の相関器では、搬送波NCOによって同位相の搬送波レプリカが、

もう一方の相関器では直交位相の搬送波レプリカが生成されます。

P.S. 相関器は、オープンソースのNAMURUをベースに開発します。

DE0-Nanoに移植したのが10年以上前なのね。すっかり忘れている。

https://blog.goo.ne.jp/osqzss/e/e088b635bc33084117b7e9606316a569

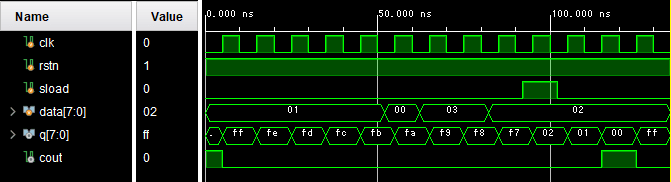

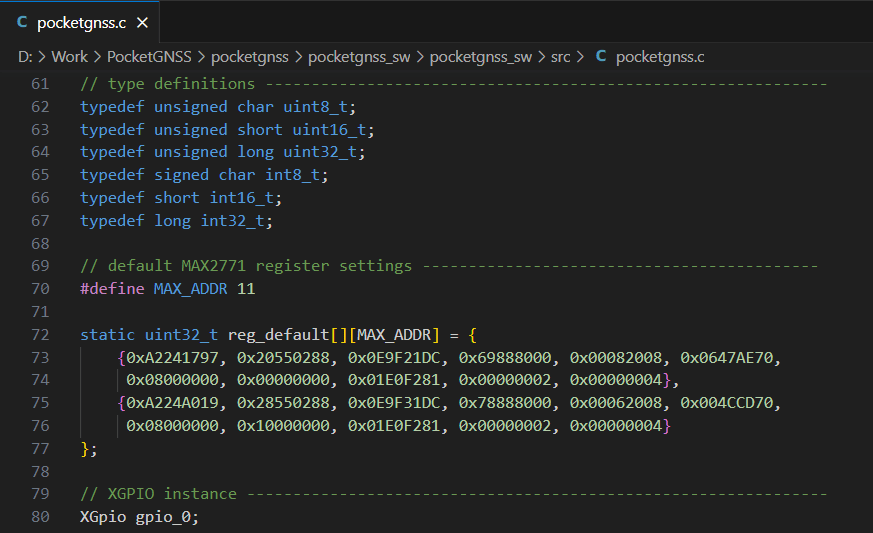

PocketSDR+FPGAの開発環境を整えるべく、まずは2つのMAX2771の中心周波数や

サンプリング周波数を設定できるようにします。基本的には↓と同じ。

https://blog.goo.ne.jp/osqzss/e/9beea46afd397912bbcebe5a57c8a14e

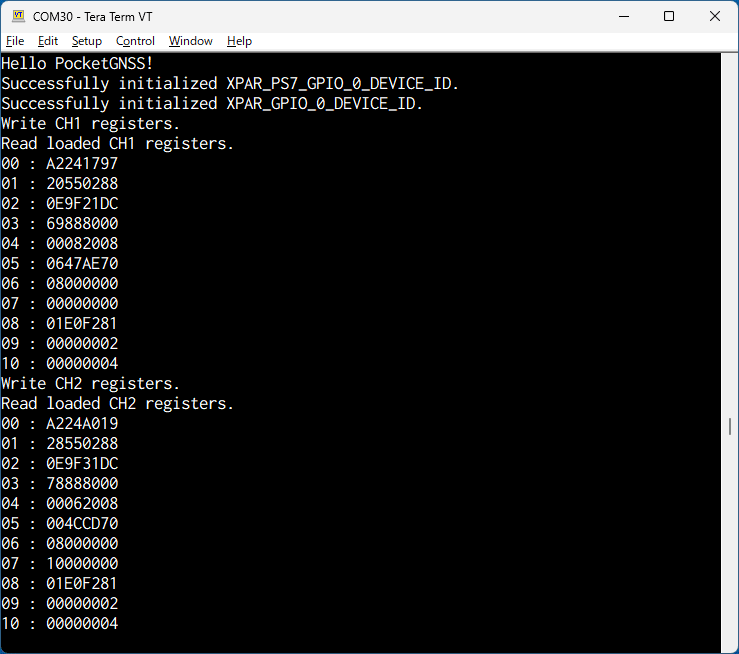

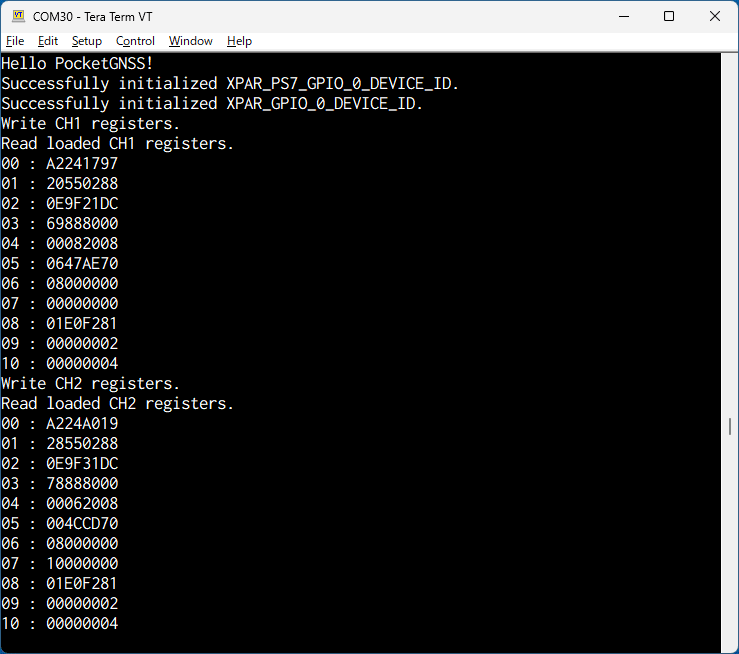

デフォルトのレジスタ値は、PocketSDRと同じにしています。

問題なくレジスタが設定できているようです。

開発のベースとなる環境は整ったので、次は相関器を実装して信号捕捉を目指します。

MATLAB/SimulinkのHDL Coderも試してみたい。

https://blog.goo.ne.jp/osqzss/e/8f2b39bbacd19d9d08f037cce23fd5de

P.S. ソースコードをGitHubで公開して行きたいのだけれども、Vivadoのプロジェクトや

Block Design、Vitisのプロジェクトをそれぞれバージョン管理する良い方法が分からない。

P.P.S. なひたふJTAG日記:Vivadoのプロジェクトをgitで管理する最小限は何か

http://nahitafu.cocolog-nifty.com/nahitafu/2019/05/post-60422b.html

サンプリング周波数を設定できるようにします。基本的には↓と同じ。

https://blog.goo.ne.jp/osqzss/e/9beea46afd397912bbcebe5a57c8a14e

デフォルトのレジスタ値は、PocketSDRと同じにしています。

問題なくレジスタが設定できているようです。

開発のベースとなる環境は整ったので、次は相関器を実装して信号捕捉を目指します。

MATLAB/SimulinkのHDL Coderも試してみたい。

https://blog.goo.ne.jp/osqzss/e/8f2b39bbacd19d9d08f037cce23fd5de

P.S. ソースコードをGitHubで公開して行きたいのだけれども、Vivadoのプロジェクトや

Block Design、Vitisのプロジェクトをそれぞれバージョン管理する良い方法が分からない。

P.P.S. なひたふJTAG日記:Vivadoのプロジェクトをgitで管理する最小限は何か

http://nahitafu.cocolog-nifty.com/nahitafu/2019/05/post-60422b.html

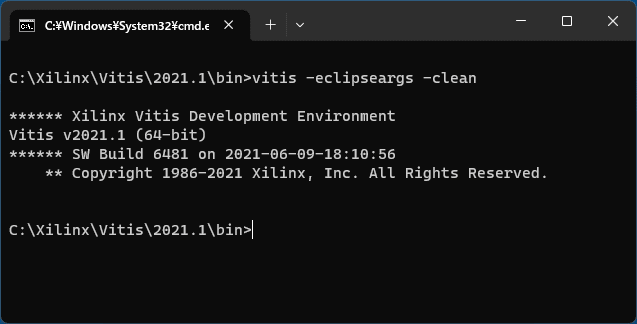

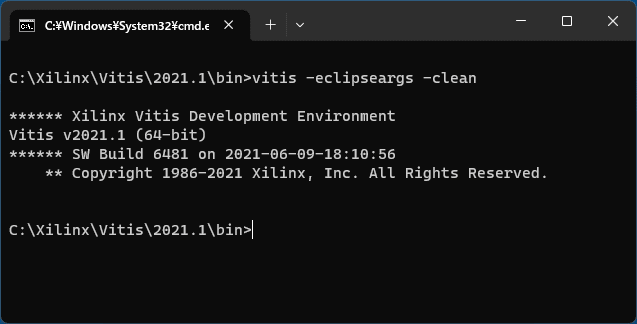

今度はVitisを起動してworkspaceを選んでも、「Vits IDE 応答なし」のまま

Vitis IDEが立ち上がらない。

原因不明だけれども、「eclipse.exe -clean」で解決するらしい。

https://marsee101.blog.fc2.com/blog-entry-5551.html

魔法の言葉、「vitis -eclipseargs -clean」でVitisを起動してworkspaceを選ぶと、

無事にVitis IDEが起動しました

Vitis IDEが立ち上がらない。

原因不明だけれども、「eclipse.exe -clean」で解決するらしい。

https://marsee101.blog.fc2.com/blog-entry-5551.html

魔法の言葉、「vitis -eclipseargs -clean」でVitisを起動してworkspaceを選ぶと、

無事にVitis IDEが起動しました

久しぶりにZybo Z7にbitstreamを書き込もうとしたら、ターゲットを認識してくれない。

原因が不明なので、Digilentのcable driverを再インストール。インストーラは↓で見つかります。

vivadoインストールフォルダ\data\xicom\cable_drivers\nt64\digilent\install_digilent.exe

原因が不明なので、Digilentのcable driverを再インストール。インストーラは↓で見つかります。

vivadoインストールフォルダ\data\xicom\cable_drivers\nt64\digilent\install_digilent.exe

「新しいフェーズに入った衛星測位技術を加速させる人材育成」の教材に

ソフトウェア受信機を活用していますが、FPGAでスタンドアローンの

GNSS受信機を開発したいという要望も多いです。

そこで、PocketSDRのフロントエンド部だけを取り出し、ZYBO-Z7など

DIGILENT社のFPGA評価ボードに接続できる基板を作製しました。

オリジナルのPocketSDRからは、基板を4層にしたり、RF分配器に

100オームのアイソレーション抵抗を追加したり、RF性能の改善を

試みています。

ZYBO-Z7とセットで、5台ほど準備する予定です。開発に興味があり

協力していただける方は、ぜひ人材育成プロジェクトまでご連絡ください。

P.S. まずはEZ-USB FX2LP Discoveryに接続して、PocketSDRとして動作を確認。

問題なくGNSS信号の捕捉が確認できました。

ソフトウェア受信機を活用していますが、FPGAでスタンドアローンの

GNSS受信機を開発したいという要望も多いです。

そこで、PocketSDRのフロントエンド部だけを取り出し、ZYBO-Z7など

DIGILENT社のFPGA評価ボードに接続できる基板を作製しました。

オリジナルのPocketSDRからは、基板を4層にしたり、RF分配器に

100オームのアイソレーション抵抗を追加したり、RF性能の改善を

試みています。

ZYBO-Z7とセットで、5台ほど準備する予定です。開発に興味があり

協力していただける方は、ぜひ人材育成プロジェクトまでご連絡ください。

P.S. まずはEZ-USB FX2LP Discoveryに接続して、PocketSDRとして動作を確認。

問題なくGNSS信号の捕捉が確認できました。

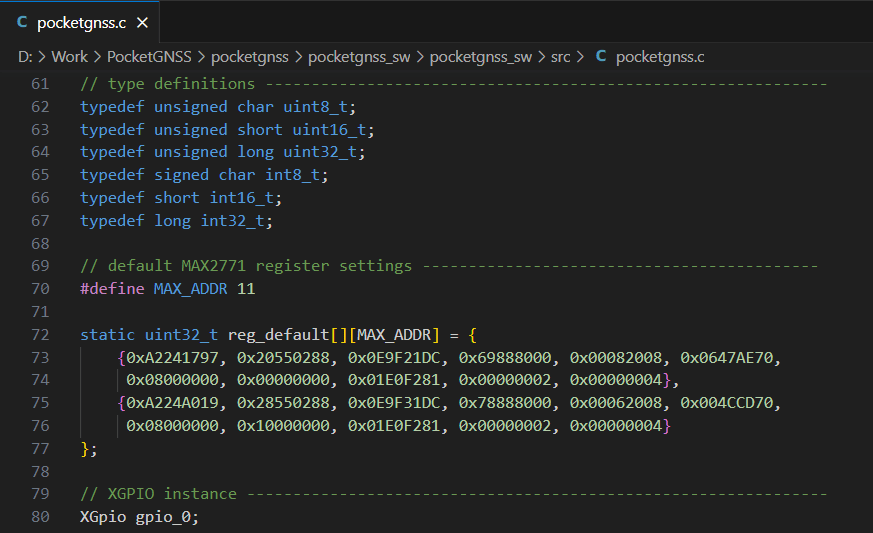

一年以上放置していたMAX2771の基板をZYBOに接続して、GNSS受信機開発を再開。

https://blog.goo.ne.jp/osqzss/e/72ac9b6eca3813b12310b58b70e4dddc

まずは、MAX2771のレジスタにアクセスして、中心周波数やサンプリング周波数を設定できるようにします。

インターフェイスには、PocketSDRで動作が確認できているGPIOによるbit bangingを採用。

データの読み書きは、同じピンをinoutで使うため、AXIO GPIOのAll InputsとAll Outputsの

どちらもチェックせずにBlock Designに組み込みます。

こうすることで、Wrapperの生成で自動的にIOBUFのプリミティブが挿入され、inoutのピンになります。

GPIOの制御は、PocketSDRのコードをほぼそのまま流用。

大きな違いは入出力の方向が0で出力、1で入力ということくらい。

問題なくMAX2771のレジスタにアクセスできました。

https://blog.goo.ne.jp/osqzss/e/72ac9b6eca3813b12310b58b70e4dddc

まずは、MAX2771のレジスタにアクセスして、中心周波数やサンプリング周波数を設定できるようにします。

インターフェイスには、PocketSDRで動作が確認できているGPIOによるbit bangingを採用。

データの読み書きは、同じピンをinoutで使うため、AXIO GPIOのAll InputsとAll Outputsの

どちらもチェックせずにBlock Designに組み込みます。

こうすることで、Wrapperの生成で自動的にIOBUFのプリミティブが挿入され、inoutのピンになります。

GPIOの制御は、PocketSDRのコードをほぼそのまま流用。

大きな違いは入出力の方向が0で出力、1で入力ということくらい。

問題なくMAX2771のレジスタにアクセスできました。