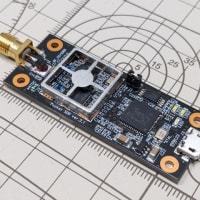

PocketSDR+FPGAの開発環境を整えるべく、まずは2つのMAX2771の中心周波数や

サンプリング周波数を設定できるようにします。基本的には↓と同じ。

https://blog.goo.ne.jp/osqzss/e/9beea46afd397912bbcebe5a57c8a14e

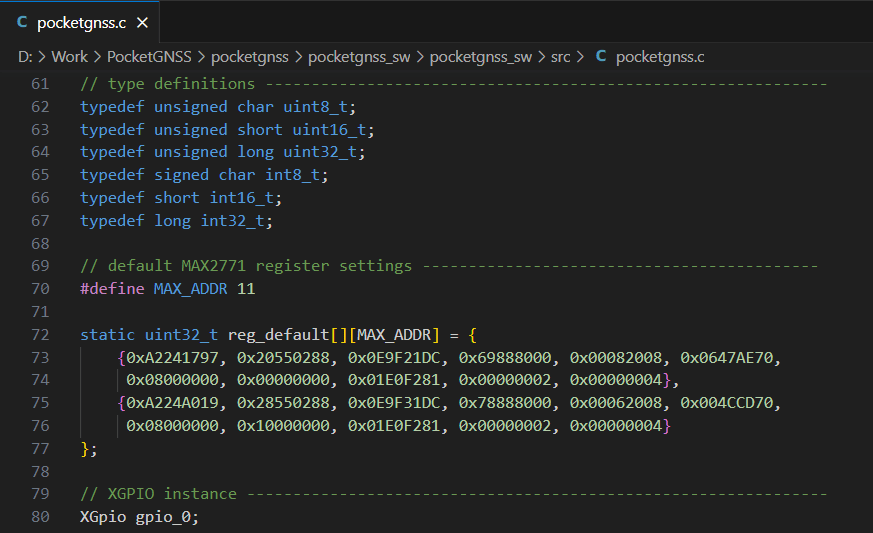

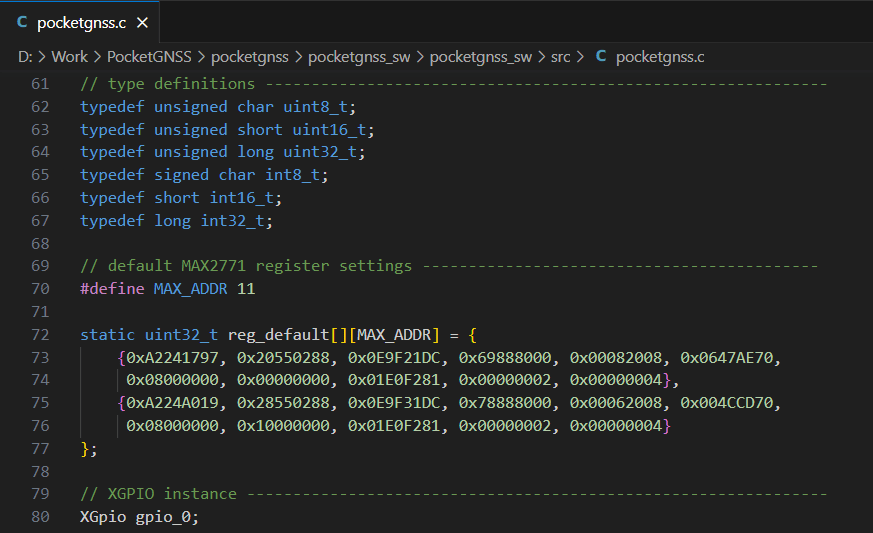

デフォルトのレジスタ値は、PocketSDRと同じにしています。

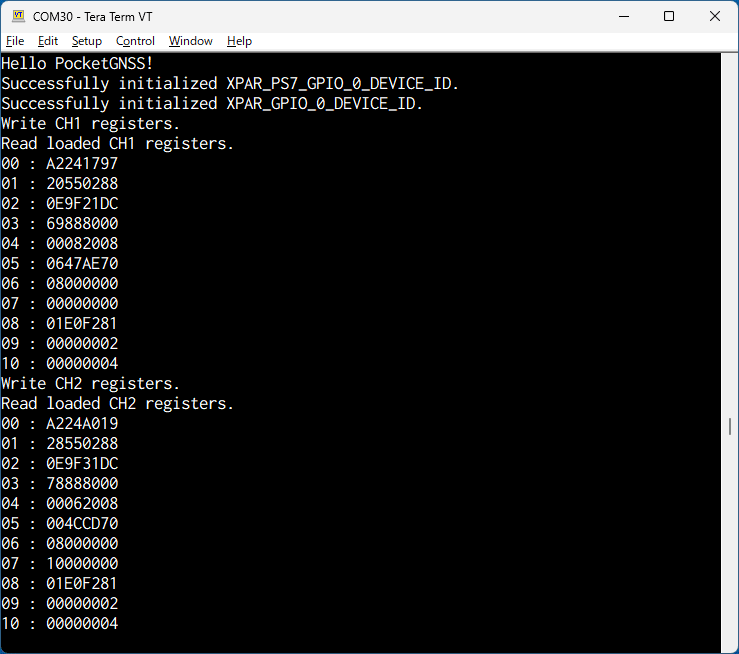

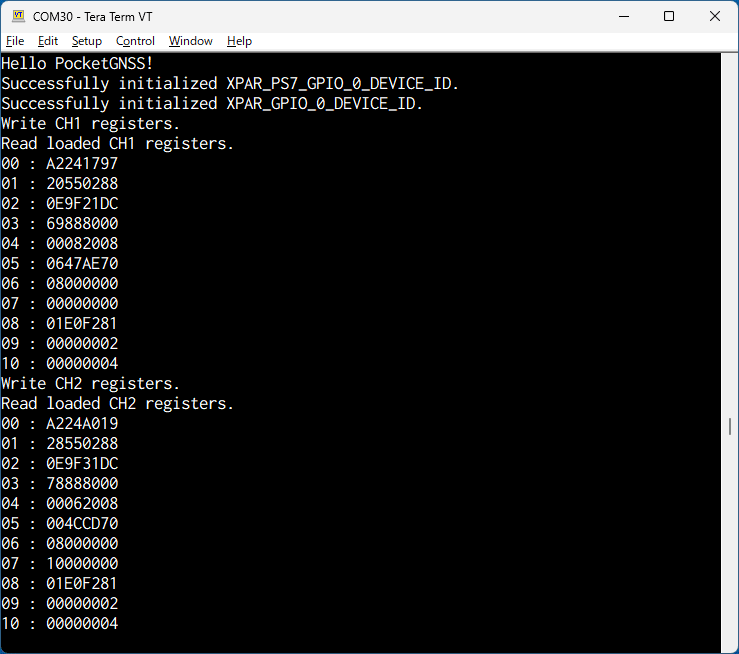

問題なくレジスタが設定できているようです。

開発のベースとなる環境は整ったので、次は相関器を実装して信号捕捉を目指します。

MATLAB/SimulinkのHDL Coderも試してみたい。

https://blog.goo.ne.jp/osqzss/e/8f2b39bbacd19d9d08f037cce23fd5de

P.S. ソースコードをGitHubで公開して行きたいのだけれども、Vivadoのプロジェクトや

Block Design、Vitisのプロジェクトをそれぞれバージョン管理する良い方法が分からない。

P.P.S. なひたふJTAG日記:Vivadoのプロジェクトをgitで管理する最小限は何か

http://nahitafu.cocolog-nifty.com/nahitafu/2019/05/post-60422b.html

サンプリング周波数を設定できるようにします。基本的には↓と同じ。

https://blog.goo.ne.jp/osqzss/e/9beea46afd397912bbcebe5a57c8a14e

デフォルトのレジスタ値は、PocketSDRと同じにしています。

問題なくレジスタが設定できているようです。

開発のベースとなる環境は整ったので、次は相関器を実装して信号捕捉を目指します。

MATLAB/SimulinkのHDL Coderも試してみたい。

https://blog.goo.ne.jp/osqzss/e/8f2b39bbacd19d9d08f037cce23fd5de

P.S. ソースコードをGitHubで公開して行きたいのだけれども、Vivadoのプロジェクトや

Block Design、Vitisのプロジェクトをそれぞれバージョン管理する良い方法が分からない。

P.P.S. なひたふJTAG日記:Vivadoのプロジェクトをgitで管理する最小限は何か

http://nahitafu.cocolog-nifty.com/nahitafu/2019/05/post-60422b.html

https://github.com/barbedo/vivado-git?ysclid=llv7v6y5su650781739

I used it and it seems to work fine.