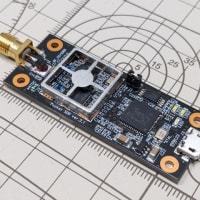

前作ではその効果がいまひとつであったHackRF向けの外部クロック.

今回はクロックバッファを入れてみました.

CDCLVC1102: Low Jitter, 1:2 LVCMOS Fan-out Clock Buffer

これでLVCMOSのCLKINがドライブできる?

周波数オフセットがどの程度改善されたのか,HackRFで出力したGPS信号を

ubloxのGPS受信機に入力して,Clock StatusのClock Driftを確認してみます.

外部クロックを付けた状態だと,Clock Driftは0.05μs/s以下になりました.

この単位は,1秒間に1μ秒の誤差という意味なので,ppmと同じです.

これは,かなり良好な値.

さて,外部クロックを外してHackRF搭載のXOで動作させると,

どうなるでしょうか.

このときのClock Driftは,8μs/sと跳ね上がります.

XOの安定性が20ppm程度なので,妥当な値です.

どうやら,外部クロックとしては,周波数オフセットを見事に解決して

くれています.しかし,相変わらずGPS受信機側の信号は安定しません.

PCからHackRFへのデータの転送の方に問題があるのでしょうか.

原因はいまだに不明です.

$100の差額があっても,GPS信号シミュレータを楽しみたいのであれば,

bladeRFを買おう!

今回はクロックバッファを入れてみました.

CDCLVC1102: Low Jitter, 1:2 LVCMOS Fan-out Clock Buffer

これでLVCMOSのCLKINがドライブできる?

周波数オフセットがどの程度改善されたのか,HackRFで出力したGPS信号を

ubloxのGPS受信機に入力して,Clock StatusのClock Driftを確認してみます.

外部クロックを付けた状態だと,Clock Driftは0.05μs/s以下になりました.

この単位は,1秒間に1μ秒の誤差という意味なので,ppmと同じです.

これは,かなり良好な値.

さて,外部クロックを外してHackRF搭載のXOで動作させると,

どうなるでしょうか.

このときのClock Driftは,8μs/sと跳ね上がります.

XOの安定性が20ppm程度なので,妥当な値です.

どうやら,外部クロックとしては,周波数オフセットを見事に解決して

くれています.しかし,相変わらずGPS受信機側の信号は安定しません.

PCからHackRFへのデータの転送の方に問題があるのでしょうか.

原因はいまだに不明です.

$100の差額があっても,GPS信号シミュレータを楽しみたいのであれば,

bladeRFを買おう!

https://github.com/osqzss/gps-sdr-sim/tree/master/extclk