まだ不完全なところがありますが,DE0-Nanoに移植したNamuruのHDLコードを公開します.

プロジェクトの名前はNamuru-Nanoにしました.

http://www.sensorcomm.co.jp/osqzss/fpga/namuru/

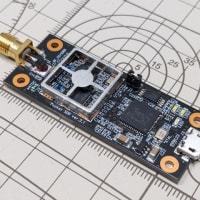

オリジナルとの大きな違いは,周波数デザインです.

Namuruに搭載されているフロントエンドICのGP2015は,40MHzの基準クロックをベースバンドに

渡し,ベースバンド側で40MHz/7=5.71MHzの信号を生成して,IF信号をサンプリングします.

一方,DE0-Nano用に設計したフロントエンドでは,16.368MHzのサンプリング信号が

基準クロックとして出力されています.

そのため,トップレベルのgps_baseband.vにおいて,サンプリング信号のsample_clkが

outputではなく,inputとなります.

オリジナルのNamuruでは,time_base.vにおいて入力された40MHzのclkから5.71MHzの

sample_clkを生成しています.

Namuru-Nanoでは,Nios IIのPLLで生成された16.368MHz*6=98.208MHzの信号をclkとして

使用します.IF信号はsample_clkの立ち上がりでサンプリングされるため,このエッジを検出し,

1clkだけaccum_sample_enableのパルスを生成します.

accumulator.vでは,この信号がhighのときだけ,相関処理を行うことになります.

また,オリジナルのNamuruでは,フロントエンドから出力される40MHzのクロックを

NCOの基準信号にしています.しかし,この信号の周波数を高くすると,同じ周波数

分解能を得るために,レジスタのビット数を増やさなければなりません.

これはあまりありがたくないので,Namuru-NanoではNCOの基準信号にも16.368MHzの

サンプリング信号を使用することにしました.そこで,NCOをaccum_sample_enable信号と

同期するために,carrier_nco.vとcode_nco.vの入力として,新たにsample_enableが

加わっています.

また,NCOのレジスタ長も,carrierは29 bit,codeは28 bitと短くなっています.

さらに,code_nco.vでは,NCOのcarryが発生した際に,0.5チップのコードに対応する

hc_enableを1clkだけ生成しなければなりません.オリジナルのNamuruでは,NCOがclkと

同期しているため,carryの発生も常に1clkですが,Namuru-Nanoでは,sample_enableの

周期がclkより長いため,1clk以上carryがhighのままになります.

そこで,carryのエッジ検出を追加して,1clkだけhc_enableのパルスを生成しています.

主な変更はこの程度です.time_base.vにおいて,tic_enableやaccum_enableの生成も

16.368MHzのサンプリングクロックに同期させたかったのですが,どうも上手く動作せず,

挫折しました.そのため,この二つの信号だけは,16.368MHz*6=98.208MHzのclk信号に

同期して動作しています.

ここさえサンプリング信号と同期が取れれば,clk信号とサンプリング信号を切り離す

ことができます.フロントエンドやシステムクロックの選択の自由度が広がるので,

なんとかしたいところです.

プロジェクトの名前はNamuru-Nanoにしました.

http://www.sensorcomm.co.jp/osqzss/fpga/namuru/

オリジナルとの大きな違いは,周波数デザインです.

Namuruに搭載されているフロントエンドICのGP2015は,40MHzの基準クロックをベースバンドに

渡し,ベースバンド側で40MHz/7=5.71MHzの信号を生成して,IF信号をサンプリングします.

一方,DE0-Nano用に設計したフロントエンドでは,16.368MHzのサンプリング信号が

基準クロックとして出力されています.

そのため,トップレベルのgps_baseband.vにおいて,サンプリング信号のsample_clkが

outputではなく,inputとなります.

オリジナルのNamuruでは,time_base.vにおいて入力された40MHzのclkから5.71MHzの

sample_clkを生成しています.

Namuru-Nanoでは,Nios IIのPLLで生成された16.368MHz*6=98.208MHzの信号をclkとして

使用します.IF信号はsample_clkの立ち上がりでサンプリングされるため,このエッジを検出し,

1clkだけaccum_sample_enableのパルスを生成します.

accumulator.vでは,この信号がhighのときだけ,相関処理を行うことになります.

また,オリジナルのNamuruでは,フロントエンドから出力される40MHzのクロックを

NCOの基準信号にしています.しかし,この信号の周波数を高くすると,同じ周波数

分解能を得るために,レジスタのビット数を増やさなければなりません.

これはあまりありがたくないので,Namuru-NanoではNCOの基準信号にも16.368MHzの

サンプリング信号を使用することにしました.そこで,NCOをaccum_sample_enable信号と

同期するために,carrier_nco.vとcode_nco.vの入力として,新たにsample_enableが

加わっています.

また,NCOのレジスタ長も,carrierは29 bit,codeは28 bitと短くなっています.

さらに,code_nco.vでは,NCOのcarryが発生した際に,0.5チップのコードに対応する

hc_enableを1clkだけ生成しなければなりません.オリジナルのNamuruでは,NCOがclkと

同期しているため,carryの発生も常に1clkですが,Namuru-Nanoでは,sample_enableの

周期がclkより長いため,1clk以上carryがhighのままになります.

そこで,carryのエッジ検出を追加して,1clkだけhc_enableのパルスを生成しています.

主な変更はこの程度です.time_base.vにおいて,tic_enableやaccum_enableの生成も

16.368MHzのサンプリングクロックに同期させたかったのですが,どうも上手く動作せず,

挫折しました.そのため,この二つの信号だけは,16.368MHz*6=98.208MHzのclk信号に

同期して動作しています.

ここさえサンプリング信号と同期が取れれば,clk信号とサンプリング信号を切り離す

ことができます.フロントエンドやシステムクロックの選択の自由度が広がるので,

なんとかしたいところです.

※コメント投稿者のブログIDはブログ作成者のみに通知されます