NamuruのHDLコードをGPS受信機として動作させるためには,それを制御するための

マイコンが必要になります.そこで,Simさんが公開されているNios IIのサンプルに

新しいコンポーネントとしてGPSを追加します.

Sim's blog:Qsysを使ってみた

サンプルと大きく異なる点は,Namuruと同様にクロック周波数です.

SimさんのNios IIはDE0-Nanoに搭載されている50MHzのクロックで動作していますが,

Namuru-Nanoではフロントエンドの16.368MHzのクロックを入力します.

そこで,まずclk_0をダブルクリックして,Clock Sourceを開き,周波数を変更します.

(クリックで拡大)

(クリックで拡大)

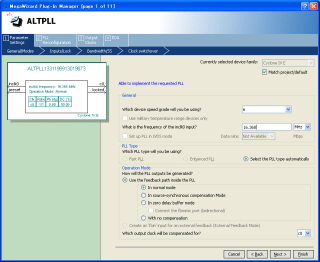

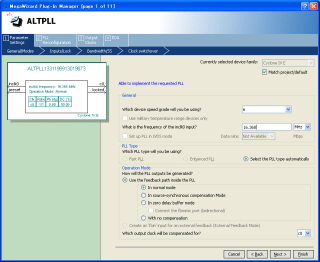

次に,ALTPLLを開き,こちらも入力周波数を16.368MHzに変更します.

(クリックで拡大)

(クリックで拡大)

さらに,PLLからの出力であるc0のClock multiplication factorを6に設定します.

Nios IIは,16.368MHz*6=98.208MHzで動作することになります.

(クリックで拡大)

(クリックで拡大)

SDRAMのクロックとなるc1も,同様にClock multiplication factorを6に設定します.

(クリックで拡大)

(クリックで拡大)

サンプルからの変更はこれだけです.

次に,New Componentをクリックして,GPSコンポーネントを追加して行きます.

まず,HDL Filesのタブで,NamuruのHDLファイルをすべて追加します.

Top Levelのモジュールには,gps_baseband.vを選択します.

(クリックで拡大)

(クリックで拡大)

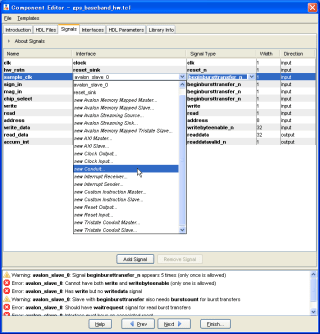

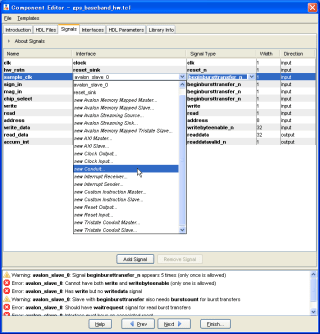

次に,Signalsのタブで,信号のインターフェイスやタイプを設定して行きます.

自動に設定された初期状態ではエラーばかりですので,ひとつひとつ消して行きます.

(クリックで拡大)

(クリックで拡大)

時々,変更を加えてもエラーや警告が更新されないことがあります.

そんなときは,FileメニューからReanalyze HDL Filesを実行してみてください.

リセット信号のインターフェイスには,new Reset Inputからreset_sinkを選択します.

プルダウンメニューに表示される名称と,選択後にInterfaceとして表示される名称が

異なるので混乱します.これ,なんとかなりませんか,Alteraさん?

(クリックで拡大)

(クリックで拡大)

さらに,Signal Typeにはreset_nを選びます.

実はこれも紛らわしい.コンポーネントによっては,実際のSignal TypeとSystem Contentsの

画面で表示される名称が異なるものがあります.表示はresetなのに,Signal Typeはreset_nだったり.

これもなんとかして欲しい…

(クリックで拡大)

(クリックで拡大)

フロントエンドと接続され,外部からの入力となるsample_clk,sign_in,mag_inには

Interfaceとしてnew Conduitからconduit_endを選びます.Signal Typeはexportです.

(クリックで拡大)

(クリックで拡大)

Nios IIへの割り込み信号となるaccum_intにはInterfaceとしてinterrupt_senderを

選びます.Signal Typeはirqです.

(クリックで拡大)

(クリックで拡大)

最終的なSignalsのタブは,以下のようになります.これでエラーが2つまで減りました.

(クリックで拡大)

(クリックで拡大)

次に,Interfacesタブに移り,残りのエラーを解消して行きます.

まず1つめのエラーであるavalon_slave_0のAssociated Resetにreset_sinkを選びます.

(クリックで拡大)

(クリックで拡大)

続いて,interrupt_senderのAssociated addressable interfaceにavalon_slave_0を選択します.

(クリックで拡大)

(クリックで拡大)

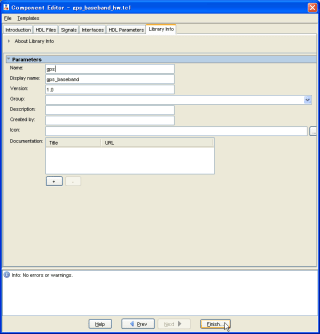

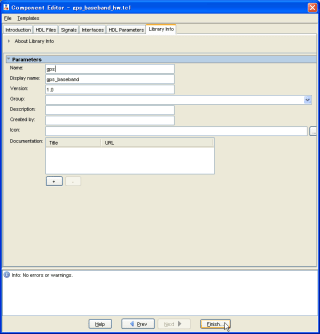

これでエラーがすべて消えましたので,Library Infoタブでコンポーネントの名称を入力して,

Finishをクリックします.

(クリックで拡大)

(クリックで拡大)

Component Libraryには,新たにgps_basebandが追加されました.これをダブルクリックして

System Contentsに追加します.

他のコンポーネントと同様に,gps_0.clockはaltpll_0.c0に,gps_0.avalon_slave_0は

nios2_qsys_0.data_masterに,gps_0.reset_sinkはclk_0.clk_resetに接続します.

gps_0.conduit_endには,Exportの欄をクリックしてgps_0_conduit_endに設定します.

さらに,gps_0.avalon_slave_0のirqをnios2_qsys_0に接続します.割り込みの優先度は

jtag_uart_0より高く設定します.ここでは0を選びました.

Base adressは0x06000000としています.

(クリックで拡大)

(クリックで拡大)

これでシステムの生成ができます.GenerationタブでGenerationボタンをクリックしてください.

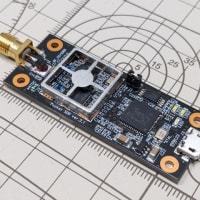

次に,GPSコンポーネントを追加したQsysモジュールを呼び出すように,DE0_Nano.vを修正します.

Simさんのサンプルとは異なり,.clk_clkにはフロントエンドのサンプリング信号であるGPIO_0_IN[0]が

接続されます.また,GPSモジュールの外部インターフェイスであるgps_0_conduit_endが追加されています.

sample_clk,sign_in,mag_inをそれぞれGPIO_0_IN[0],GPIO_0[1],GPIO_0[0]に接続します.

フロントエンド基板の回路図はこちら.

(クリックで拡大)

(クリックで拡大)

以上で作業は終了です.あとは論理合成をするだけ.

論理合成の結果を見ると,ロジックエレメントがまだ半分近く余っています.

GPSモジュールのチャンネルを倍近く増やすことができそうです.すばらしい!

GPS+GLONASS受信機が作れると良いけれど,まだまだ妄想の域だな.

マイコンが必要になります.そこで,Simさんが公開されているNios IIのサンプルに

新しいコンポーネントとしてGPSを追加します.

Sim's blog:Qsysを使ってみた

サンプルと大きく異なる点は,Namuruと同様にクロック周波数です.

SimさんのNios IIはDE0-Nanoに搭載されている50MHzのクロックで動作していますが,

Namuru-Nanoではフロントエンドの16.368MHzのクロックを入力します.

そこで,まずclk_0をダブルクリックして,Clock Sourceを開き,周波数を変更します.

(クリックで拡大)

(クリックで拡大)次に,ALTPLLを開き,こちらも入力周波数を16.368MHzに変更します.

(クリックで拡大)

(クリックで拡大)さらに,PLLからの出力であるc0のClock multiplication factorを6に設定します.

Nios IIは,16.368MHz*6=98.208MHzで動作することになります.

(クリックで拡大)

(クリックで拡大)SDRAMのクロックとなるc1も,同様にClock multiplication factorを6に設定します.

(クリックで拡大)

(クリックで拡大)サンプルからの変更はこれだけです.

次に,New Componentをクリックして,GPSコンポーネントを追加して行きます.

まず,HDL Filesのタブで,NamuruのHDLファイルをすべて追加します.

Top Levelのモジュールには,gps_baseband.vを選択します.

(クリックで拡大)

(クリックで拡大)次に,Signalsのタブで,信号のインターフェイスやタイプを設定して行きます.

自動に設定された初期状態ではエラーばかりですので,ひとつひとつ消して行きます.

(クリックで拡大)

(クリックで拡大)時々,変更を加えてもエラーや警告が更新されないことがあります.

そんなときは,FileメニューからReanalyze HDL Filesを実行してみてください.

リセット信号のインターフェイスには,new Reset Inputからreset_sinkを選択します.

プルダウンメニューに表示される名称と,選択後にInterfaceとして表示される名称が

異なるので混乱します.これ,なんとかなりませんか,Alteraさん?

(クリックで拡大)

(クリックで拡大)さらに,Signal Typeにはreset_nを選びます.

実はこれも紛らわしい.コンポーネントによっては,実際のSignal TypeとSystem Contentsの

画面で表示される名称が異なるものがあります.表示はresetなのに,Signal Typeはreset_nだったり.

これもなんとかして欲しい…

(クリックで拡大)

(クリックで拡大)フロントエンドと接続され,外部からの入力となるsample_clk,sign_in,mag_inには

Interfaceとしてnew Conduitからconduit_endを選びます.Signal Typeはexportです.

(クリックで拡大)

(クリックで拡大)Nios IIへの割り込み信号となるaccum_intにはInterfaceとしてinterrupt_senderを

選びます.Signal Typeはirqです.

(クリックで拡大)

(クリックで拡大)最終的なSignalsのタブは,以下のようになります.これでエラーが2つまで減りました.

(クリックで拡大)

(クリックで拡大)次に,Interfacesタブに移り,残りのエラーを解消して行きます.

まず1つめのエラーであるavalon_slave_0のAssociated Resetにreset_sinkを選びます.

(クリックで拡大)

(クリックで拡大)続いて,interrupt_senderのAssociated addressable interfaceにavalon_slave_0を選択します.

(クリックで拡大)

(クリックで拡大)これでエラーがすべて消えましたので,Library Infoタブでコンポーネントの名称を入力して,

Finishをクリックします.

(クリックで拡大)

(クリックで拡大)Component Libraryには,新たにgps_basebandが追加されました.これをダブルクリックして

System Contentsに追加します.

他のコンポーネントと同様に,gps_0.clockはaltpll_0.c0に,gps_0.avalon_slave_0は

nios2_qsys_0.data_masterに,gps_0.reset_sinkはclk_0.clk_resetに接続します.

gps_0.conduit_endには,Exportの欄をクリックしてgps_0_conduit_endに設定します.

さらに,gps_0.avalon_slave_0のirqをnios2_qsys_0に接続します.割り込みの優先度は

jtag_uart_0より高く設定します.ここでは0を選びました.

Base adressは0x06000000としています.

(クリックで拡大)

(クリックで拡大)これでシステムの生成ができます.GenerationタブでGenerationボタンをクリックしてください.

次に,GPSコンポーネントを追加したQsysモジュールを呼び出すように,DE0_Nano.vを修正します.

Simさんのサンプルとは異なり,.clk_clkにはフロントエンドのサンプリング信号であるGPIO_0_IN[0]が

接続されます.また,GPSモジュールの外部インターフェイスであるgps_0_conduit_endが追加されています.

sample_clk,sign_in,mag_inをそれぞれGPIO_0_IN[0],GPIO_0[1],GPIO_0[0]に接続します.

フロントエンド基板の回路図はこちら.

(クリックで拡大)

(クリックで拡大)以上で作業は終了です.あとは論理合成をするだけ.

論理合成の結果を見ると,ロジックエレメントがまだ半分近く余っています.

GPSモジュールのチャンネルを倍近く増やすことができそうです.すばらしい!

GPS+GLONASS受信機が作れると良いけれど,まだまだ妄想の域だな.

※コメント投稿者のブログIDはブログ作成者のみに通知されます