高須さんにクロック分周回路を介すとCLKOUTの信号レベルが改善されると情報をいただいた.

試しに周波数を1/2にしてみると,もともと1.17VppだったCLKOUTが2.0Vppに変化する.

納得いかない仕様だけれど,これならFX2LPのIFCLKをドライブできそう.

しかし,MAX2771のADCは,CLKの立ち上がりでサンプリングして,立ち下りでValidとなる.

一方,FX2LPのsynchronous slave FIFOは,IFCLKの立ち上がりでバスのデータを読み込むので,

やはりMAX2771のCLKOUTはインバータに入力して信号レベルと一緒に極性も反転した方が

良いかもしれない.

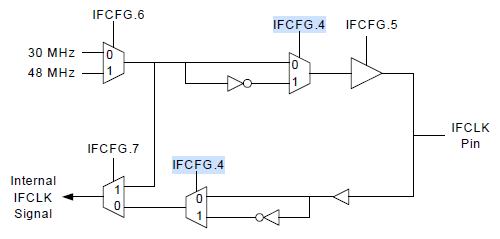

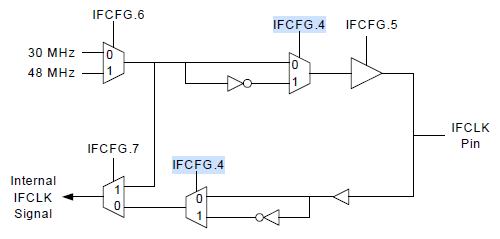

P.S. IFCLKの極性は,IFCFG.4で選べるのね.

試しに周波数を1/2にしてみると,もともと1.17VppだったCLKOUTが2.0Vppに変化する.

納得いかない仕様だけれど,これならFX2LPのIFCLKをドライブできそう.

しかし,MAX2771のADCは,CLKの立ち上がりでサンプリングして,立ち下りでValidとなる.

一方,FX2LPのsynchronous slave FIFOは,IFCLKの立ち上がりでバスのデータを読み込むので,

やはりMAX2771のCLKOUTはインバータに入力して信号レベルと一緒に極性も反転した方が

良いかもしれない.

P.S. IFCLKの極性は,IFCFG.4で選べるのね.

※コメント投稿者のブログIDはブログ作成者のみに通知されます