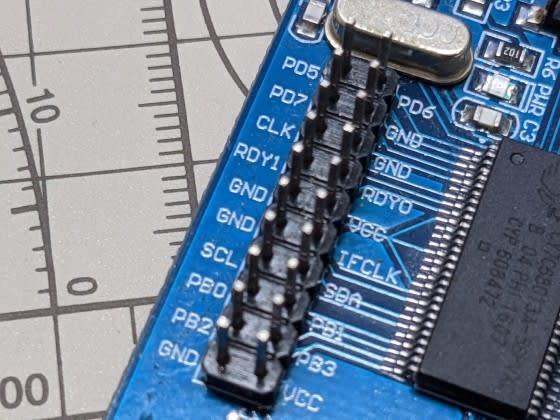

Slave FIFOのファームウェアがどうしても動作せず,納得がいかないので

高須さんからお借りしているメーカ不明のFX2LP基板のヘッダピンの結線を

ひとつひとつチェックしてみました.

そうしたら,バスの読み書きの方向を指定するRDY1/SLWRとRDY0/SLRDの

シルクが逆になっていることが判明.バスからFIFOへの書き込みのために

SLWRをアクティブにしているつもりが,その逆方向のSLRDをアクティブに

していました.

正しくSLWRをlowに,SLRDをhighに設定したところ,無事にslave FIFOの

動作が確認できました.こんなことで日曜日を丸一日溶かすことになろうとは.

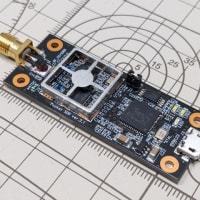

FX2LP基板単体の動作チェックでは,IFCLKに内部クロックを指定していますが,

これをMAX2771からのCLKOUTに切り替えればI/Qデータが取り込めるはず.

高須さんからお借りしているメーカ不明のFX2LP基板のヘッダピンの結線を

ひとつひとつチェックしてみました.

そうしたら,バスの読み書きの方向を指定するRDY1/SLWRとRDY0/SLRDの

シルクが逆になっていることが判明.バスからFIFOへの書き込みのために

SLWRをアクティブにしているつもりが,その逆方向のSLRDをアクティブに

していました.

正しくSLWRをlowに,SLRDをhighに設定したところ,無事にslave FIFOの

動作が確認できました.こんなことで日曜日を丸一日溶かすことになろうとは.

FX2LP基板単体の動作チェックでは,IFCLKに内部クロックを指定していますが,

これをMAX2771からのCLKOUTに切り替えればI/Qデータが取り込めるはず.

※コメント投稿者のブログIDはブログ作成者のみに通知されます