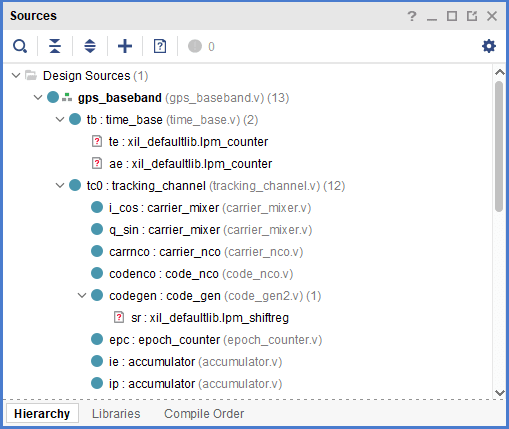

Namuru-NanoのbasebandのHDLをVivadoで合成してみると、当然、

AlteraのIPであるlpm_counterとlpm_shiftregが未定義とエラーが出ます。

lpm_counterは、Xilinx LogiCORE IPのbinary counterに置き換えられそうでしたので、

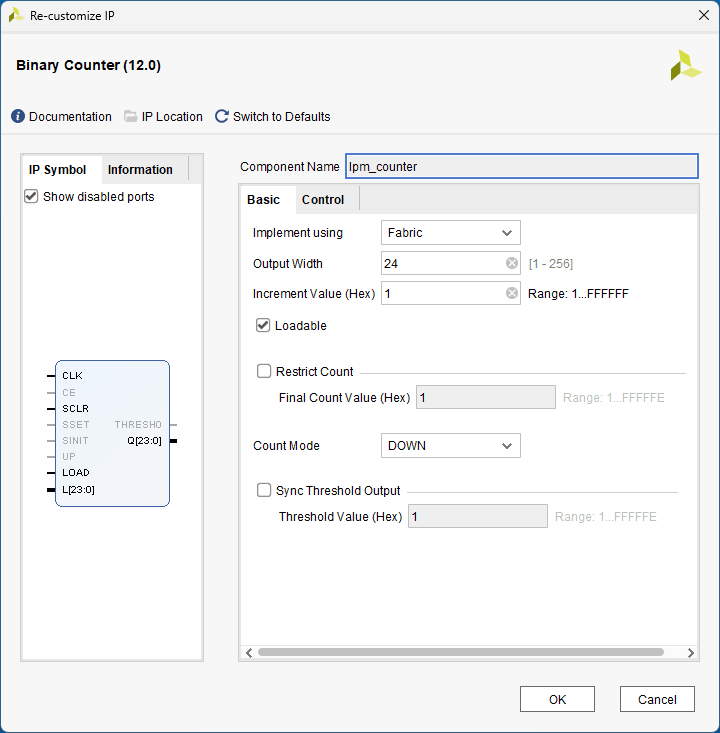

VivadoのIPカタログからbinary counterを開き、各種パラメータを設定します。

VivadoでのIPコアの使いかたは、こちらを参考にしました。

ACRi:FPGA をもっと活用するために IP コアを使ってみよう (2)

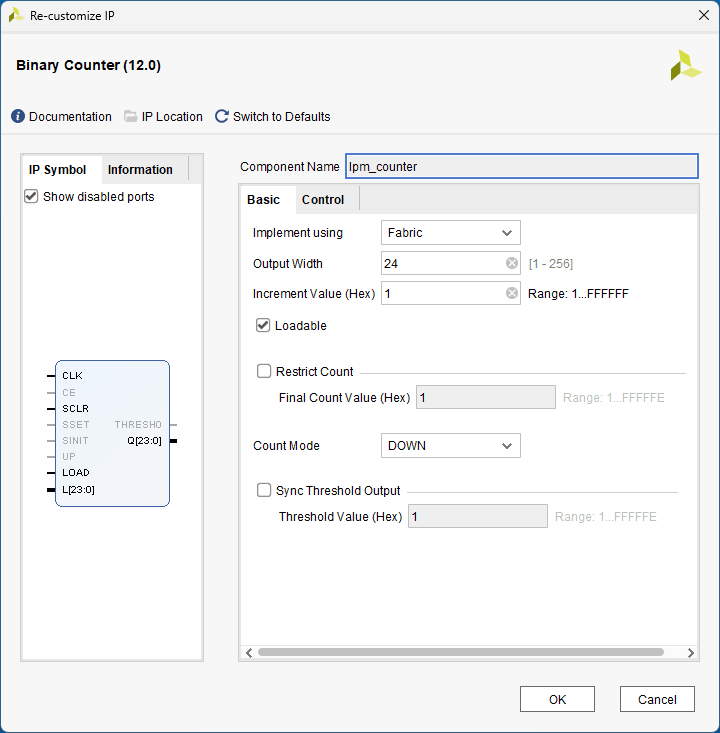

Binary CounterのComponent Nameは、Altera IPと同じlpm_counterにします。

Output Widthは24ビット、Loadableを有効にし、Count ModeはDOWNです。

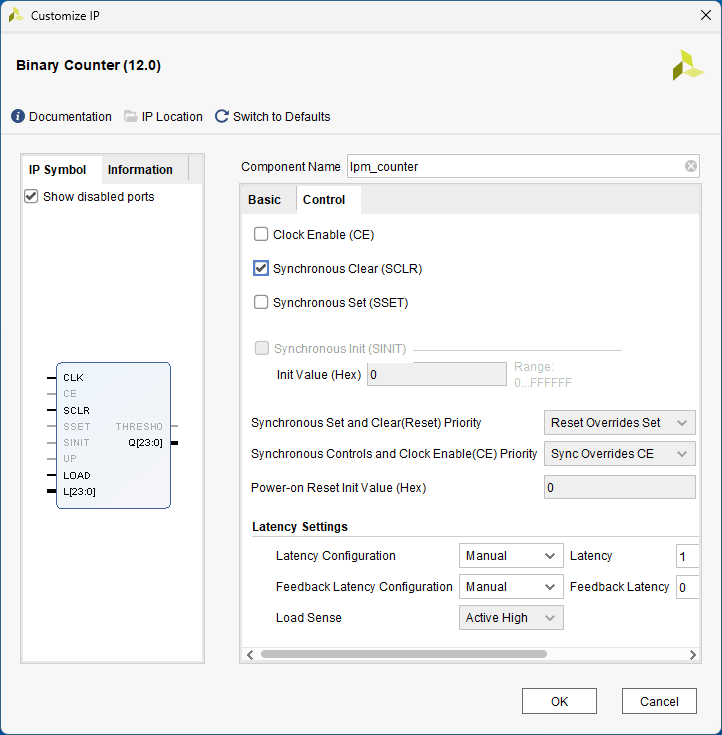

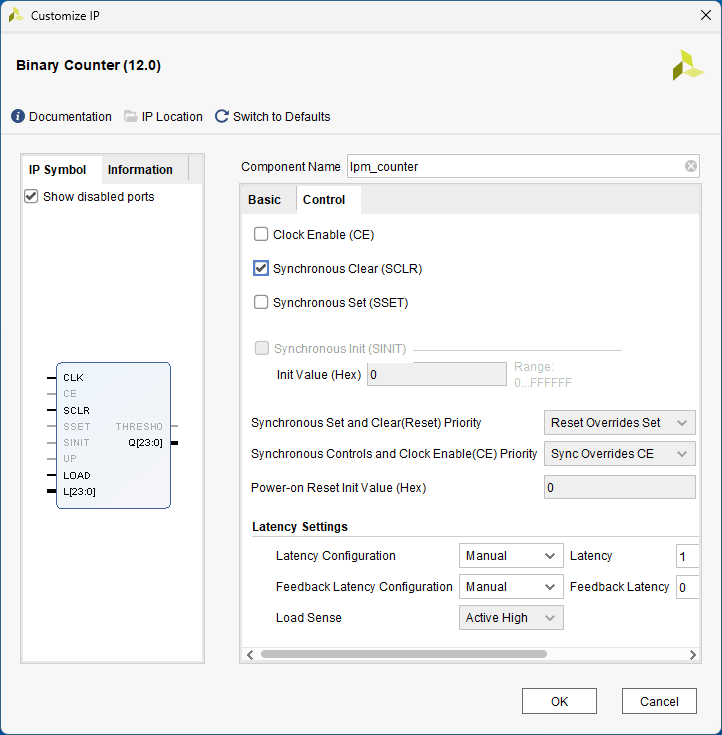

Synchronous Clearも有効にします。

設定ダイアログのOKをクリックして閉じると、Generate Output Productsの

ダイアログが開きます。GenerateをクリックしてIPコアを合成します。

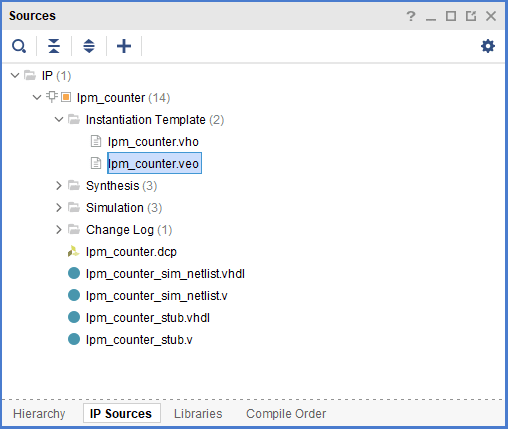

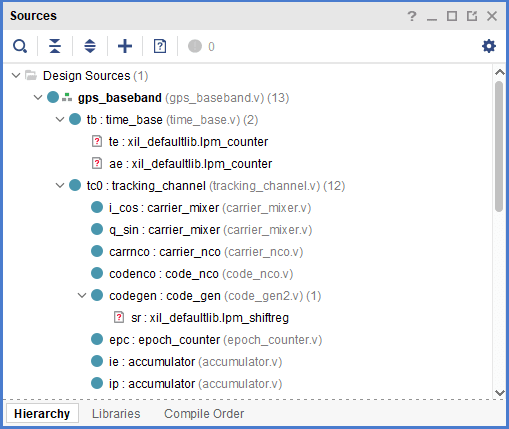

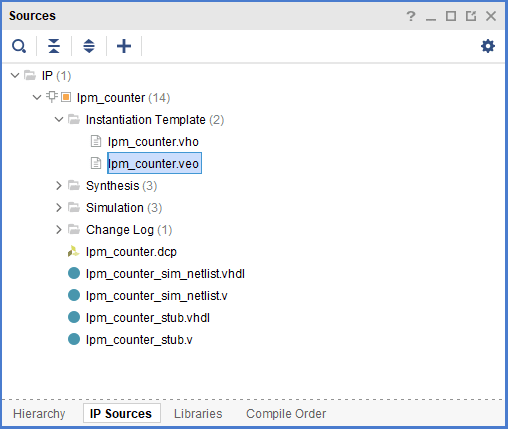

IPコアのモジュールが準備できたら、SourcesペインのIP Sourcesタブから、

テンプレートファイル(.veo)を開きます。

このインスタンス生成のテンプレートを、もとのソースコードにコピーして、

入出力ポートの信号を接続します。

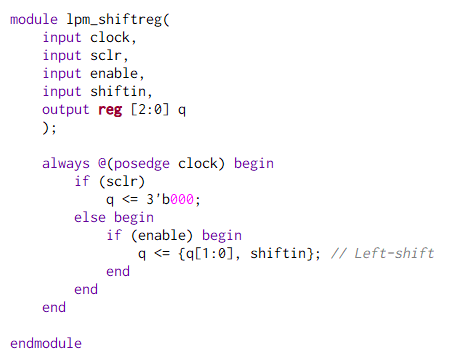

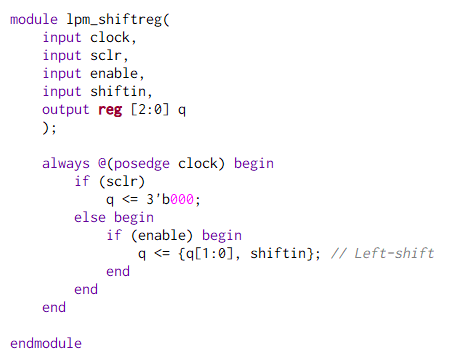

一方、lpm_shiftregは、ちょうど置き換えれるようなIPが見当たりません。

そのため、こちらはモジュールのHDLコードを追加します。

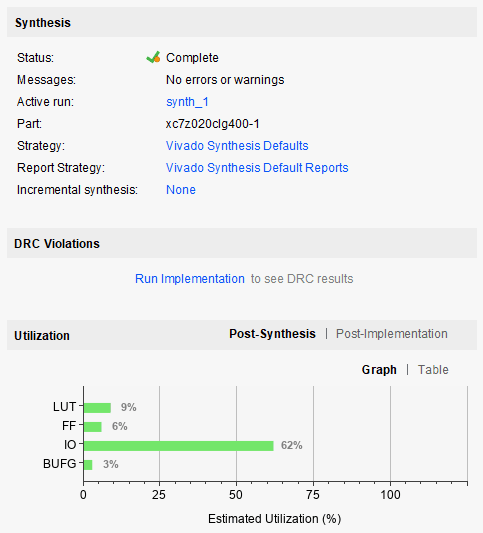

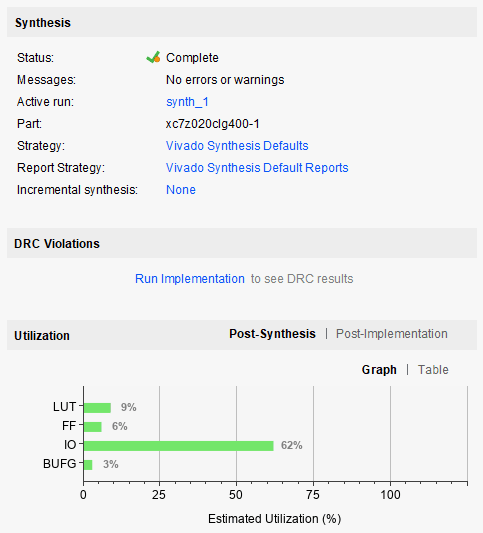

これで、Run Synthesisを実行すると、errorもwarningもなしで、合成が完了します。

P.S. Binary Counterの設定画面を見ると、Final Count Valueが1からFFFFFEまでしか選べません。

0までカウントダウンしてくれないのでしょうか?それとも、Restrict Countを有効にしなければ、

0またはFFFFFFがFinal Count Valueになるのでしょうか?別途、テストベンチを組んで確かめよう。

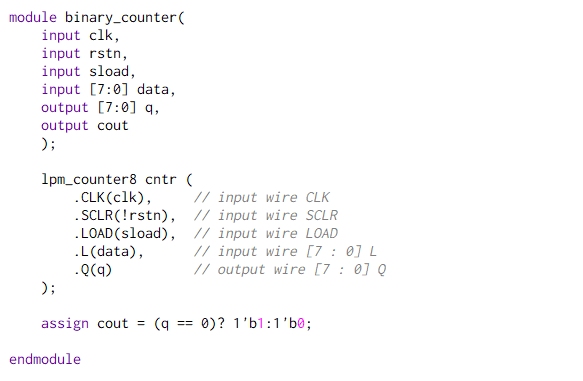

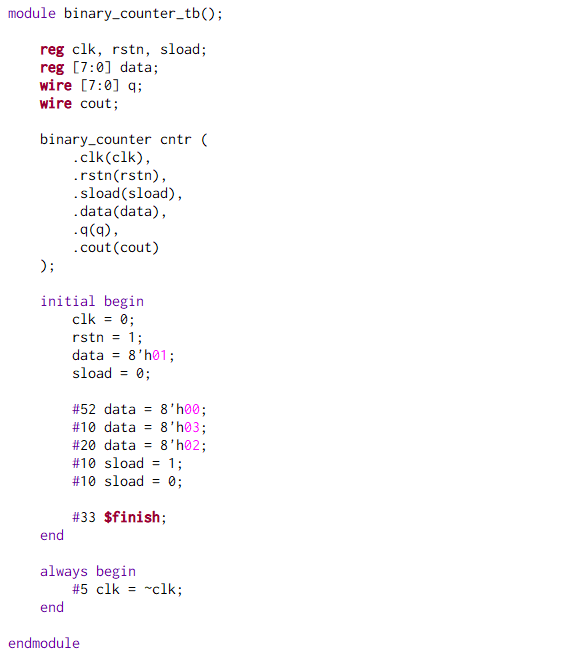

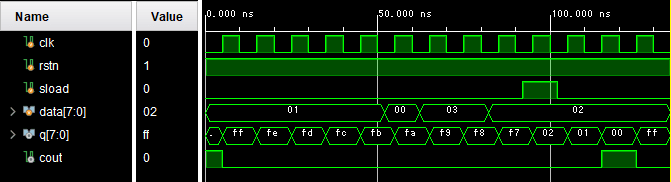

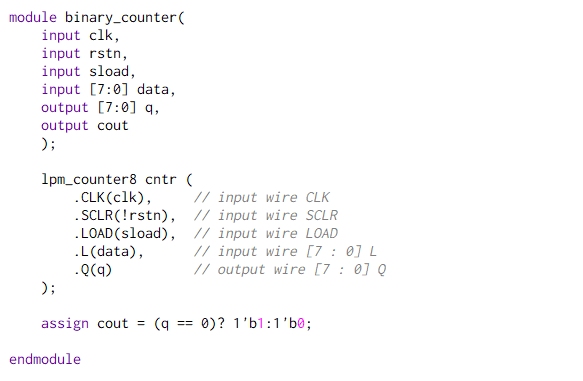

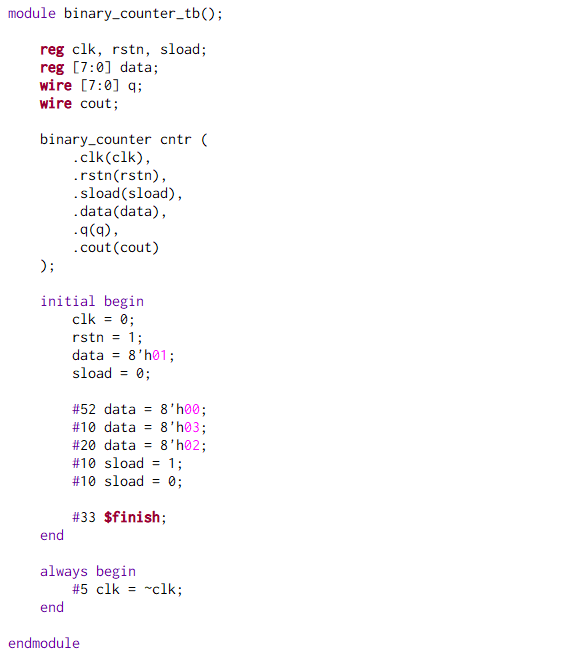

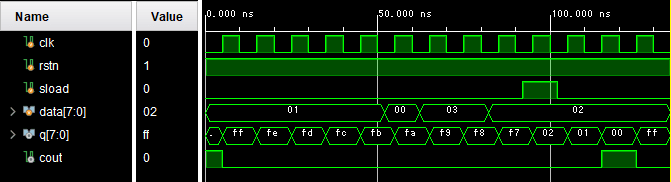

P.P.S. 8ビットのBinary Counterを作成して、テストベンチで動作を確認してみました。

lpm_counterと同様に、loadされた値から0までカウントダウンしてくれるようです。

AlteraのIPであるlpm_counterとlpm_shiftregが未定義とエラーが出ます。

lpm_counterは、Xilinx LogiCORE IPのbinary counterに置き換えられそうでしたので、

VivadoのIPカタログからbinary counterを開き、各種パラメータを設定します。

VivadoでのIPコアの使いかたは、こちらを参考にしました。

ACRi:FPGA をもっと活用するために IP コアを使ってみよう (2)

Binary CounterのComponent Nameは、Altera IPと同じlpm_counterにします。

Output Widthは24ビット、Loadableを有効にし、Count ModeはDOWNです。

Synchronous Clearも有効にします。

設定ダイアログのOKをクリックして閉じると、Generate Output Productsの

ダイアログが開きます。GenerateをクリックしてIPコアを合成します。

IPコアのモジュールが準備できたら、SourcesペインのIP Sourcesタブから、

テンプレートファイル(.veo)を開きます。

このインスタンス生成のテンプレートを、もとのソースコードにコピーして、

入出力ポートの信号を接続します。

一方、lpm_shiftregは、ちょうど置き換えれるようなIPが見当たりません。

そのため、こちらはモジュールのHDLコードを追加します。

これで、Run Synthesisを実行すると、errorもwarningもなしで、合成が完了します。

P.S. Binary Counterの設定画面を見ると、Final Count Valueが1からFFFFFEまでしか選べません。

0までカウントダウンしてくれないのでしょうか?それとも、Restrict Countを有効にしなければ、

0またはFFFFFFがFinal Count Valueになるのでしょうか?別途、テストベンチを組んで確かめよう。

P.P.S. 8ビットのBinary Counterを作成して、テストベンチで動作を確認してみました。

lpm_counterと同様に、loadされた値から0までカウントダウンしてくれるようです。

※コメント投稿者のブログIDはブログ作成者のみに通知されます