Namuru-Nanoでは、IF信号をサンプリングするクロックを6逓倍して

システムクロックとし、サンプリングクロックはenable信号にするという

少しトリッキーな実装をしています。

これは、オリジナルのNamaruのコードをできるだけ変更しないための

苦肉の策ですが、とりあえずこのままポートします。

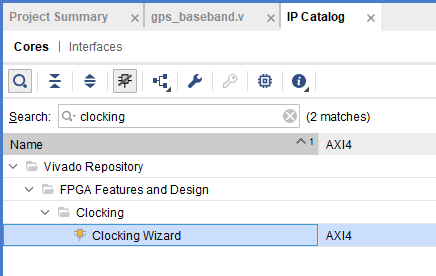

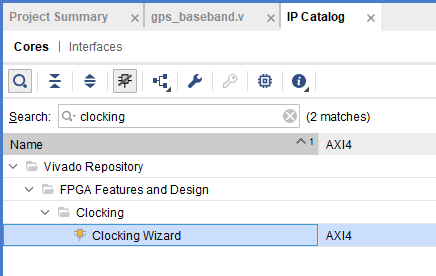

Namuru-Nanoでは、システムクロックの生成にNios IIのPLLを使っていましたが、

ZynqではClocking Wizardを使って、MMCMを追加します。

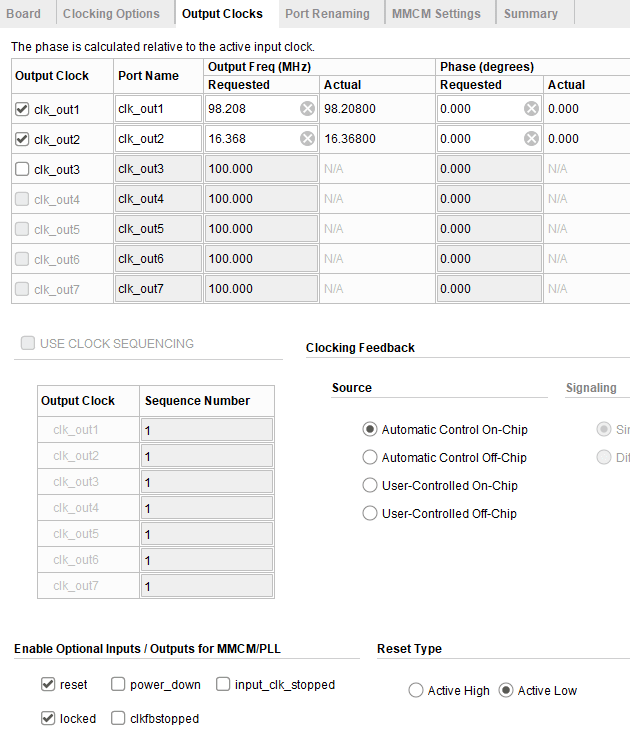

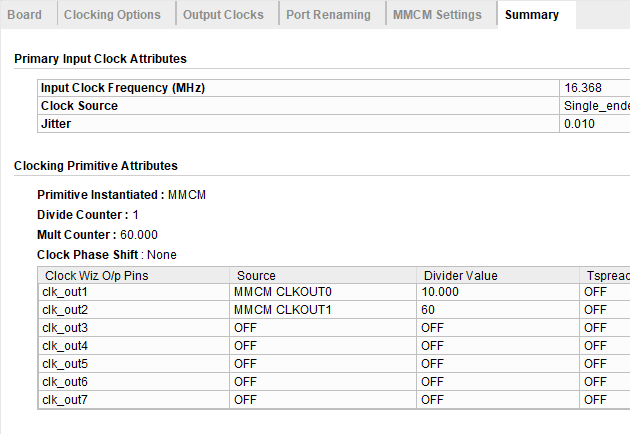

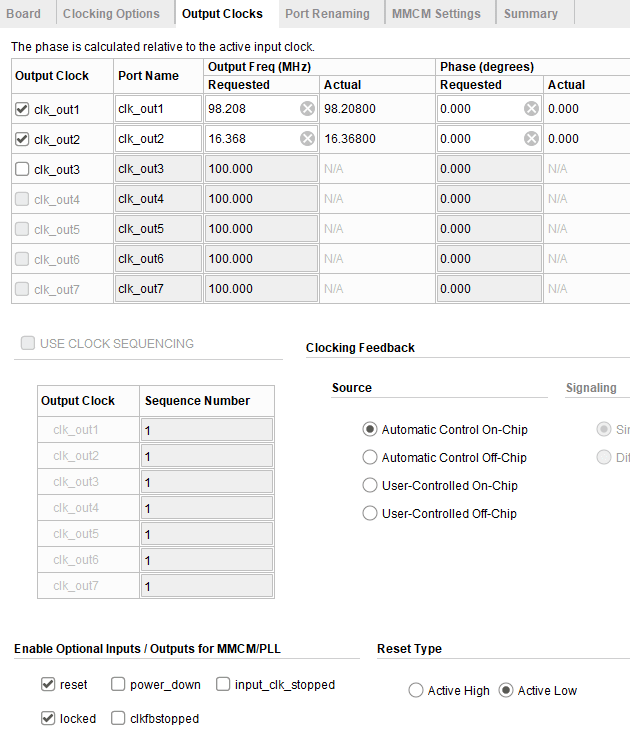

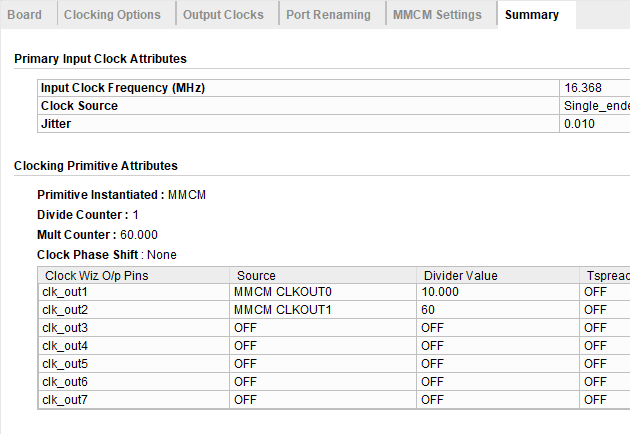

クロック入力の周波数は、とりあえずNamuru-Nanoと同じ16.368MHzとし、

それを6逓倍した90.208MHzのシステムクロックと、そのままのenable信号を

出力します。

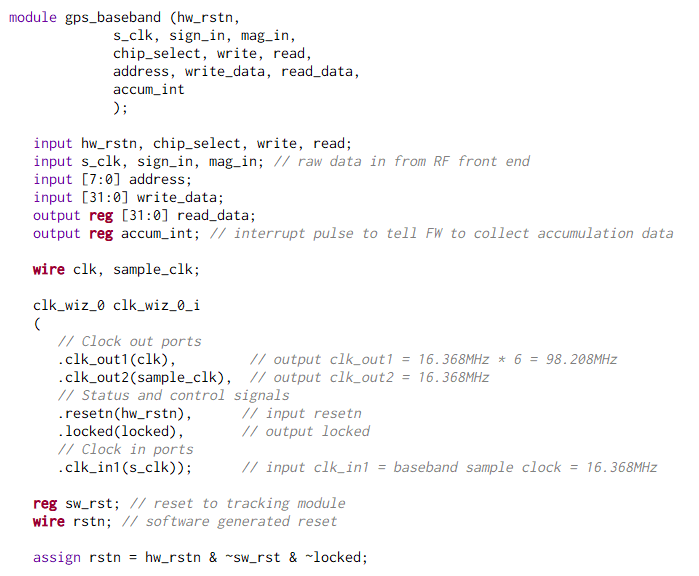

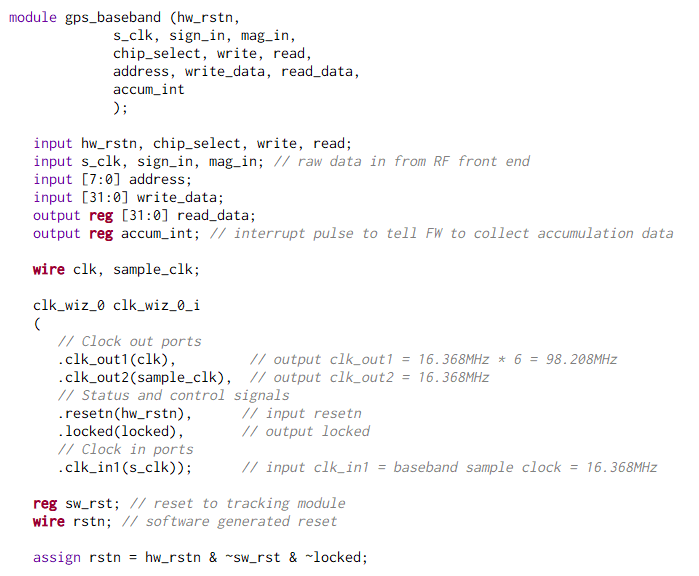

生成されたIPコアは、トップモジュールに組み込みます。

フロントエンドから供給されるサンプリング信号s_clkを入力とし、

システムクロックのclkと、enable信号のsample_clkを出力します。

MMCMのlocked信号も、basebandモジュールのリセット信号に追加しています。

次は、basebandモジュールをIP化して、AXIバスに繋げよう。

システムクロックとし、サンプリングクロックはenable信号にするという

少しトリッキーな実装をしています。

これは、オリジナルのNamaruのコードをできるだけ変更しないための

苦肉の策ですが、とりあえずこのままポートします。

Namuru-Nanoでは、システムクロックの生成にNios IIのPLLを使っていましたが、

ZynqではClocking Wizardを使って、MMCMを追加します。

クロック入力の周波数は、とりあえずNamuru-Nanoと同じ16.368MHzとし、

それを6逓倍した90.208MHzのシステムクロックと、そのままのenable信号を

出力します。

生成されたIPコアは、トップモジュールに組み込みます。

フロントエンドから供給されるサンプリング信号s_clkを入力とし、

システムクロックのclkと、enable信号のsample_clkを出力します。

MMCMのlocked信号も、basebandモジュールのリセット信号に追加しています。

次は、basebandモジュールをIP化して、AXIバスに繋げよう。

※コメント投稿者のブログIDはブログ作成者のみに通知されます