読者のアンプ製作中に発生したデバイスの破損。ペアやコンプリメンタリの片方が壊れると、もう片方も使えなくなります。それで、片割れが生じた終段の中出力MOS-FETを集めて、もう一度コンプリメンタリで使えないか測定しようと思いました。

しかし、中出力とは言えパワーMOS-FETです。テストにはヒートシンクが必要で、電源もヒューズ付きが必要。それなら、大出力MOS-FETもテストできる環境を構築したほうが後々に便利。それで、今までトランジスタ選別に使っていた、テスト用のバラックをMOS-FETのテスト用に作り直すことにしました。その前に、トランジスタ選別器を新規で作らなければなりません。

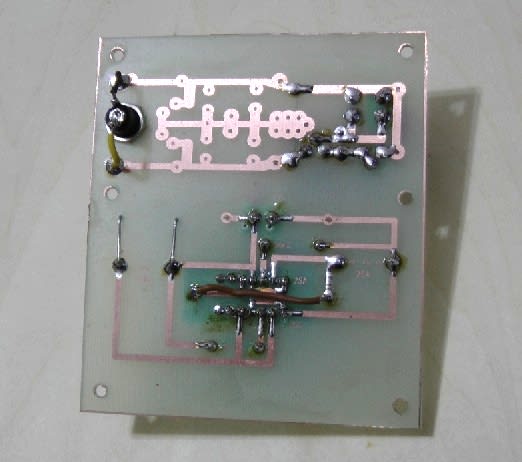

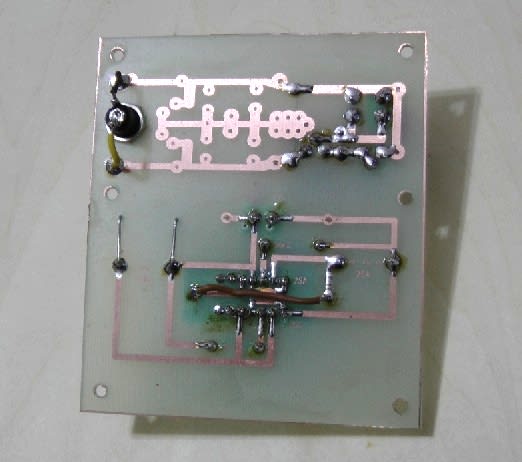

テスト用のバラックは、アンプ用の電源の後ろに電圧可変式の定電圧電源を設け、その後ろに更にトランジスタ選別基板の6v~12Vの可変式電源を設けるという無駄の連続。おかげで、作った本人も回路を思い出せないような配線が空を飛んでいます (;´Д`)

テスト用のバラック \(^o^)/

トランジスタ選別器の部分 これだけ ( ´゜д゜`)エー

ということで、まずはトランジスタの増幅率を計測する、hFE測定器と呼ばれるトランジスタ選別器の制作から→参考にしたサイト。回路は単純ですが、一つの電源で、プラスで動作するNPNトランジスタ(2SC,2SD)と、マイナスで動作するPNPトランジスタ(2SA,2SB)の両方と、足の配置の全てに対応する欲張りな設計となっています。太い足でも入るように、ICソケットはレバーで締める方式です。

hFE測定器回路の概念図(実際の電源電圧は6V)

Eはトランジスタのエミッタ、Cはコレクタ、Bはベース

どんなピンアサインにも対応できる

hFE測定器 パーツ側

hFE測定器 パターン側

このように設計思想は良かったのですが、ICソケットが想定より巨大で、テスターの鰐口クリップが咥える10Ω抵抗の居場所がなくなりました。仕方なく穴を追加して移動。実装は難しいです。また、基板製作の時にネガとポジの関係を間違って、1枚無駄にしてしまいました。使えないことはないけど、トランジスタの印字面が向こうを向くピンアサインで使うことになります。少し不便ですが、トランジスタ選別器を作りたいというメンバーには差し上げます。

パーツ側拡大

青い3W/10Ω抵抗の両端電圧×10が増幅率

右が2scなど、左が2SAなどを測定できる

パターン側 拡大

出来上がったものですが、コンパクトでスッキリ。ミニアンプの24V電源がそのまま使えます。ただ、電圧調整用の半固定抵抗を1kΩにしたので、電圧が最大で7Vまでしか上がりません。6Vで測定できるのですが、以前に測定したものと整合性を取るには、9V~12v必要なこともあるので、ここは2kΩなどに変更する予定です。

このように使う(2SA844の測定中)

このテスターは二桁までしか表示しないので使えない

それにしても、悪魔のハラワタ状態のテスト用のバラックを何とかしないと (;^ω^)

こちらの方は、初段と2段目のFETのペアを完璧にし、抵抗値も完璧に合わせ、無調整でDC漏れがゼロになる回路を作り、終段のMOS-FETを取り付けた時に、上下の差が最も少ないものをコンプリとする選別方法を取りたいと思います。機械的な測定ではなく、実装状態での誤差の少ないコンプリを選ぶということですね。

エフライム工房 平御幸

しかし、中出力とは言えパワーMOS-FETです。テストにはヒートシンクが必要で、電源もヒューズ付きが必要。それなら、大出力MOS-FETもテストできる環境を構築したほうが後々に便利。それで、今までトランジスタ選別に使っていた、テスト用のバラックをMOS-FETのテスト用に作り直すことにしました。その前に、トランジスタ選別器を新規で作らなければなりません。

テスト用のバラックは、アンプ用の電源の後ろに電圧可変式の定電圧電源を設け、その後ろに更にトランジスタ選別基板の6v~12Vの可変式電源を設けるという無駄の連続。おかげで、作った本人も回路を思い出せないような配線が空を飛んでいます (;´Д`)

テスト用のバラック \(^o^)/

トランジスタ選別器の部分 これだけ ( ´゜д゜`)エー

ということで、まずはトランジスタの増幅率を計測する、hFE測定器と呼ばれるトランジスタ選別器の制作から→参考にしたサイト。回路は単純ですが、一つの電源で、プラスで動作するNPNトランジスタ(2SC,2SD)と、マイナスで動作するPNPトランジスタ(2SA,2SB)の両方と、足の配置の全てに対応する欲張りな設計となっています。太い足でも入るように、ICソケットはレバーで締める方式です。

hFE測定器回路の概念図(実際の電源電圧は6V)

Eはトランジスタのエミッタ、Cはコレクタ、Bはベース

どんなピンアサインにも対応できる

hFE測定器 パーツ側

hFE測定器 パターン側

このように設計思想は良かったのですが、ICソケットが想定より巨大で、テスターの鰐口クリップが咥える10Ω抵抗の居場所がなくなりました。仕方なく穴を追加して移動。実装は難しいです。また、基板製作の時にネガとポジの関係を間違って、1枚無駄にしてしまいました。使えないことはないけど、トランジスタの印字面が向こうを向くピンアサインで使うことになります。少し不便ですが、トランジスタ選別器を作りたいというメンバーには差し上げます。

パーツ側拡大

青い3W/10Ω抵抗の両端電圧×10が増幅率

右が2scなど、左が2SAなどを測定できる

パターン側 拡大

出来上がったものですが、コンパクトでスッキリ。ミニアンプの24V電源がそのまま使えます。ただ、電圧調整用の半固定抵抗を1kΩにしたので、電圧が最大で7Vまでしか上がりません。6Vで測定できるのですが、以前に測定したものと整合性を取るには、9V~12v必要なこともあるので、ここは2kΩなどに変更する予定です。

このように使う(2SA844の測定中)

このテスターは二桁までしか表示しないので使えない

それにしても、悪魔のハラワタ状態のテスト用のバラックを何とかしないと (;^ω^)

こちらの方は、初段と2段目のFETのペアを完璧にし、抵抗値も完璧に合わせ、無調整でDC漏れがゼロになる回路を作り、終段のMOS-FETを取り付けた時に、上下の差が最も少ないものをコンプリとする選別方法を取りたいと思います。機械的な測定ではなく、実装状態での誤差の少ないコンプリを選ぶということですね。

エフライム工房 平御幸