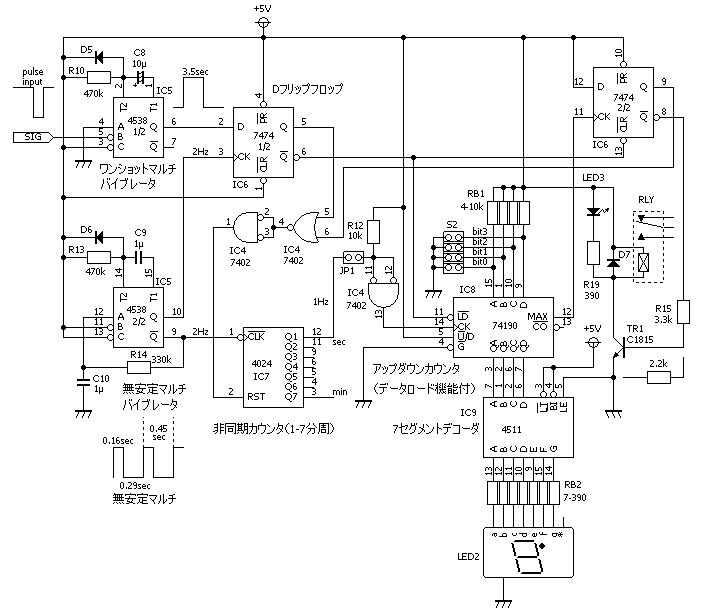

この回路は、入力端子である[SIG]に信号パルス(アクティブLo)が入力されることにより、あらかじめ設定した数値がプリセットされ、その値からダウンカウントを始めます。ダウンカウントにより数値がゼロに達したら動作を停止してスタンバイ状態になります。また、数値がゼロに達するまでに次の信号パルスが[SIG]に入力されると、再び同じ設定値がプリセットされダウンカウントを継続します。リレーの接点出力は、ダウンカウント中はONスイッチングしており、カウント値がゼロになるとOFFスイッチングします。

([SIG]端子は抵抗でプルアップされているものとします)

では具体的に回路動作を確認していきましょう。

スタンダードC-MOSの4538はタイマー回路を2個持っており、外付け部品によって1つをワンショットマルチ(単安定マルチバイブレータ)、もう1つを無安定マルチとして動作させています。

回路全体の動作タイミングは、この2つのタイマー回路によって決まります。具体的には、ワンショットマルチと無安定マルチの出力が共にHiになった時点で、非同期カウンタの4024がリセットされ、アップダウンカウンタの74HC190が4bitの設定値(S2)をロード(プリセット)します。そして、無安定マルチの次のパルス(Hi)によってダウンカウントが開始されます。

少し詳しく見てみましょう。信号入力端子[SIG]がトリガ(Loパルス入力)されると、ワンショットマルチは図に示しているような3.5secのHiパルスを出力します。一方、無安定マルチは、これも図のように、0.45secの周期でHiパルス(1.16sec)を常時出力しています。ということは、3.5secのワンパルスの間に7回、ワンショットマルチと無安定マルチの出力が共にHiになるということです。このタイミングは1回だけでシステムリセットがかかりますから、残りの6回は予備と考えればいいでしょう。

さて、ワンショットマルチの出力は74HC74(1/2)のD端子に、無安定マルチの出力は同じく74HC74(1/2)のCK端子に入力されています。74HC74はCKがトリガされるとDに入力されている論理値(Hi or Lo)をQに出力しその値を保持します。(論理値を保持するデバイスをフリップ・フロップといいます)。Q-はQの逆論理値を出力します。いまQはHiになっています。行き先を追ってみましょう。74HC02の5pinに入っています。ここで74HC02はNOR回路が2個直列になっていますが、これは1つのOR回路と見なせます。とすると、非同期カウンタの4024がリセットされることがわかりますね。

次にQ-(Lo)の行き先を追ってみましょう。アップダウンカウンタ74HC190のLD端子に入っているのでスイッチS2で設定したディジタル値がロードされます。また74HC74(2/2)のCLR端子にも入っているので、74HC74(2/2)はリセットされてQ=Lo、Q-=Hiとなります。出力Q-は3.3kΩの抵抗を経てトランジスタ(TR1)のベースに入っており、Q-の値はHiですからトランジスタはスイッチングし、コレクタ電流によってリレーがONしLED3が点灯します。これでダウンカウント開始の準備が整いました。

無安定マルチは常時パルスを出力しているので、ワンショットマルチの出力期間(3.5sec)後も74HC74(1/2)のCKをトリガします。ワンショットパルス終了後はD端子がLoになるので、ここでCKがトリガされるとQとQ-の論理値が入れ替わりQ=Loになります。すると非同期カウンタ4024のリセットが解かれ、無安定マルチバイブレータのQ-出力が4024のCLK端子に入力されているので、4024はアップカウントを開始します。また、74HC74(2/2)のCLR端子はHiに切換りますが、CLRはLo入力によってリセットするという意味ですから、Hiの場合はQとQ-の論理値は保たれリレーはON状態を継続します。

さて4024はCLKに入力されたパルスを数えて(カウントして)Q1を最小桁(LSB)、Q7を最大桁(MSB)とする7桁(7bit)の2進数として出力します。これを各出力bitに注目して具体的に考えてみましょう。初期状態のQ1~Q7の出力はすべてLoです。CLKに1つ目のパルスが入力されるとQ1がHiになります。2つ目のパルスが入力されるとQ1はLoになり、このときQ2がHiになります。3つ目のパルスでQ1はまたHiになり、4つ目のパルスでLoになって、このときQ2がLoになりQ3がHiになります。カウンタICはこのようにして、入力されるパルスの数を数えていくデバイスです。

さて動作が見えてきましたか?つまりQ1~Q7のそれぞれのパルス周波数は、必ず1つ下位の桁の1/2になるということです。無安定マルチの出力周波数は約2Hz(周期:0.45sec)ですから、Q1の周波数は1Hz、Q2の周波数は0.5Hzです。周期として見れば、2倍、4倍、8倍と長くなっていき、Q7では約1分(Q1を1秒とすると64秒)になります。

この図では、4024のQ1、つまり1Hzのパルスを(NOR回路を経て)アップダウンカウンタ74HC190のCKに入力しています。アップもしくはダウンカウントの選択はU/D端子の論理値で決まり、Hiならばダウン、Loならばアップカウントになります(回路図参照)。また、最初のリセット時に74HC190は設定値を読込んでいるので、その値からのダウンカウントになります。プリセットされた設定値やカウント中の値はQA~QDの4bitに出力されます。そしてダウンカウントが進みこの4bitすべてがLo(2進数にてゼロ)になればMAX端子がHiを出力し、これがカウント終了の合図になります。

74HC190のMAX端子がHiになると74HC74(2/2)のCKをトリガし、D端子がHiなのでQがHiになりQ-がLoになります。つまりカウント終了によってQとQ-の論理値が入替わり、これによってトランジスタ(TR1)がOFFスイッチングし、リレーがOFFしLED3が消灯します。以上が回路動作の一連の流れです。

(補足)

7セグメントデコーダ4511は74HC190の4bitバイナリ(2進数)データを入力し、7セグメントのLEDで10進数として読めるようにデコードするデバイスです。

さて、74HC190がロードする設定値を4bitの最大値である1111にして、本回路を動作させるとどのような動作を示すでしょう?[SIG]がトリガされると7セグメントLEDは「F」(10進数の15)を表示し、リレーがONします。数値表示は、その後1秒間隔でE、D、C、B、A、9、8、7・・・と減少し、トリガから16秒後にゼロを表示しリレーがOFFします。この最大ダウンカウント時間:16秒をもっと長くするにはどうすればよいでしょうか?

そもそも、いまの試みでカウント時間が16秒になったのは、非同期カウンタ4024のQ1を74HC190のCKに入力していたからです。もしQ2をCKに入力すれば2秒間隔で7セグメントの数値が切替り、ダウンカウント終了までの時間は32秒になります。同様にQ4を入力すれば64秒になり、Q7の出力を使えばダウンカウント時間は1024秒、17分になるということですね。

関連記事:

電子機器組立2級 回路解説(アナログ) 2010-09-10

74HC74の応用(カウンタ) 2010-04-07

([SIG]端子は抵抗でプルアップされているものとします)

では具体的に回路動作を確認していきましょう。

スタンダードC-MOSの4538はタイマー回路を2個持っており、外付け部品によって1つをワンショットマルチ(単安定マルチバイブレータ)、もう1つを無安定マルチとして動作させています。

回路全体の動作タイミングは、この2つのタイマー回路によって決まります。具体的には、ワンショットマルチと無安定マルチの出力が共にHiになった時点で、非同期カウンタの4024がリセットされ、アップダウンカウンタの74HC190が4bitの設定値(S2)をロード(プリセット)します。そして、無安定マルチの次のパルス(Hi)によってダウンカウントが開始されます。

少し詳しく見てみましょう。信号入力端子[SIG]がトリガ(Loパルス入力)されると、ワンショットマルチは図に示しているような3.5secのHiパルスを出力します。一方、無安定マルチは、これも図のように、0.45secの周期でHiパルス(1.16sec)を常時出力しています。ということは、3.5secのワンパルスの間に7回、ワンショットマルチと無安定マルチの出力が共にHiになるということです。このタイミングは1回だけでシステムリセットがかかりますから、残りの6回は予備と考えればいいでしょう。

さて、ワンショットマルチの出力は74HC74(1/2)のD端子に、無安定マルチの出力は同じく74HC74(1/2)のCK端子に入力されています。74HC74はCKがトリガされるとDに入力されている論理値(Hi or Lo)をQに出力しその値を保持します。(論理値を保持するデバイスをフリップ・フロップといいます)。Q-はQの逆論理値を出力します。いまQはHiになっています。行き先を追ってみましょう。74HC02の5pinに入っています。ここで74HC02はNOR回路が2個直列になっていますが、これは1つのOR回路と見なせます。とすると、非同期カウンタの4024がリセットされることがわかりますね。

次にQ-(Lo)の行き先を追ってみましょう。アップダウンカウンタ74HC190のLD端子に入っているのでスイッチS2で設定したディジタル値がロードされます。また74HC74(2/2)のCLR端子にも入っているので、74HC74(2/2)はリセットされてQ=Lo、Q-=Hiとなります。出力Q-は3.3kΩの抵抗を経てトランジスタ(TR1)のベースに入っており、Q-の値はHiですからトランジスタはスイッチングし、コレクタ電流によってリレーがONしLED3が点灯します。これでダウンカウント開始の準備が整いました。

無安定マルチは常時パルスを出力しているので、ワンショットマルチの出力期間(3.5sec)後も74HC74(1/2)のCKをトリガします。ワンショットパルス終了後はD端子がLoになるので、ここでCKがトリガされるとQとQ-の論理値が入れ替わりQ=Loになります。すると非同期カウンタ4024のリセットが解かれ、無安定マルチバイブレータのQ-出力が4024のCLK端子に入力されているので、4024はアップカウントを開始します。また、74HC74(2/2)のCLR端子はHiに切換りますが、CLRはLo入力によってリセットするという意味ですから、Hiの場合はQとQ-の論理値は保たれリレーはON状態を継続します。

さて4024はCLKに入力されたパルスを数えて(カウントして)Q1を最小桁(LSB)、Q7を最大桁(MSB)とする7桁(7bit)の2進数として出力します。これを各出力bitに注目して具体的に考えてみましょう。初期状態のQ1~Q7の出力はすべてLoです。CLKに1つ目のパルスが入力されるとQ1がHiになります。2つ目のパルスが入力されるとQ1はLoになり、このときQ2がHiになります。3つ目のパルスでQ1はまたHiになり、4つ目のパルスでLoになって、このときQ2がLoになりQ3がHiになります。カウンタICはこのようにして、入力されるパルスの数を数えていくデバイスです。

さて動作が見えてきましたか?つまりQ1~Q7のそれぞれのパルス周波数は、必ず1つ下位の桁の1/2になるということです。無安定マルチの出力周波数は約2Hz(周期:0.45sec)ですから、Q1の周波数は1Hz、Q2の周波数は0.5Hzです。周期として見れば、2倍、4倍、8倍と長くなっていき、Q7では約1分(Q1を1秒とすると64秒)になります。

この図では、4024のQ1、つまり1Hzのパルスを(NOR回路を経て)アップダウンカウンタ74HC190のCKに入力しています。アップもしくはダウンカウントの選択はU/D端子の論理値で決まり、Hiならばダウン、Loならばアップカウントになります(回路図参照)。また、最初のリセット時に74HC190は設定値を読込んでいるので、その値からのダウンカウントになります。プリセットされた設定値やカウント中の値はQA~QDの4bitに出力されます。そしてダウンカウントが進みこの4bitすべてがLo(2進数にてゼロ)になればMAX端子がHiを出力し、これがカウント終了の合図になります。

74HC190のMAX端子がHiになると74HC74(2/2)のCKをトリガし、D端子がHiなのでQがHiになりQ-がLoになります。つまりカウント終了によってQとQ-の論理値が入替わり、これによってトランジスタ(TR1)がOFFスイッチングし、リレーがOFFしLED3が消灯します。以上が回路動作の一連の流れです。

(補足)

7セグメントデコーダ4511は74HC190の4bitバイナリ(2進数)データを入力し、7セグメントのLEDで10進数として読めるようにデコードするデバイスです。

さて、74HC190がロードする設定値を4bitの最大値である1111にして、本回路を動作させるとどのような動作を示すでしょう?[SIG]がトリガされると7セグメントLEDは「F」(10進数の15)を表示し、リレーがONします。数値表示は、その後1秒間隔でE、D、C、B、A、9、8、7・・・と減少し、トリガから16秒後にゼロを表示しリレーがOFFします。この最大ダウンカウント時間:16秒をもっと長くするにはどうすればよいでしょうか?

そもそも、いまの試みでカウント時間が16秒になったのは、非同期カウンタ4024のQ1を74HC190のCKに入力していたからです。もしQ2をCKに入力すれば2秒間隔で7セグメントの数値が切替り、ダウンカウント終了までの時間は32秒になります。同様にQ4を入力すれば64秒になり、Q7の出力を使えばダウンカウント時間は1024秒、17分になるということですね。

関連記事:

電子機器組立2級 回路解説(アナログ) 2010-09-10

74HC74の応用(カウンタ) 2010-04-07

※コメント投稿者のブログIDはブログ作成者のみに通知されます