一週間のご無沙汰でした、的な。古すぎるか。^^;

メインの仕事であるクライアント企業の親方が無茶振りしてくれたので、頭がそっちでいっぱいになっている。とはいえ、ちょっと先のための勉強を放り出すほどアホではない。頑張って進めていくからね。

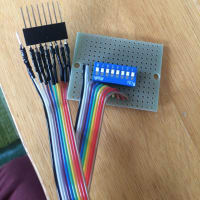

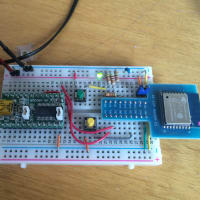

CQムックの付録基板FBボードに書き込むためのJBボードは、Ubuntuではjtagサーバが認識してくれない(2016/05/28現在)ので、悟空というAltera USB Blaser互換製品を導入したことは前回書いた。純正品の1/20ほどの価格にもかかわらず、しっかりと動いてくれてありがたい。自分で手ハンダしたJBボードが使えないのは残念だが、VMWare Fusion上のWindows10ではあまりにも遅すぎてストレスが溜まる。JBボードはFBボードに重ねるようにして使うのでFBボードのタクトスイッチが押しにくかったんだが、悟空だとフラットケーブルでつながるので楽になった。怪我の功名みたいなもんか。^^;

さて取りあえずの開発環境が整ったので、いろいろ実験してみたい。まずは「タクトスイッチを押すたびにデータスタックポインタがひとつ上がる」という、スタックマシンとしては基本中の基本をやってみようと思った。コードは書けたんだが、どうも動作が不安定だ。タクトスイッチを一度押しただけなのにスタックポインタが2つも3つも上がる。しかも不安定だ。

あぁこりゃ、チャタリングだよねとすぐにわかった。最近はあまりチャタリングが問題になるような回路を組んでいなかったので、面白いネタができたのが嬉しい。

チャタリングの性質とその対策については、「回路図で学べるFPGA入門」が役に立った。サブタイトルが「回路図は読める人のためのHDLガイド」となっていて若干敷居が高そうだし価格も価格。少し躊躇したが思い切って買っておいてよかった。この本はテーマごとに回路図(必要ならタイミングチャートなどの図)、VHDL記述、Verilog HDL記述が解説されていて、とてもていねいに書かれている。これでじっくり腰を据えて勉強して、チャタリングの性質を大まかに理解することができた。

Verilog HDLで非常に簡単な実装をやってみたのだが、思いのほかきれいに効いてくれた。やはり理屈を理解して書くコードはちゃんと動く(当たり前だ)。

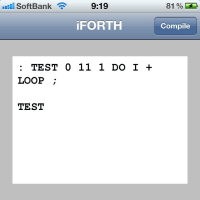

チャタリング問題が解決し、スタックマシンもこちらが考えたとおりに動いていることがわかった。もっともスタックマシンと言ったってメモリ上の配列とインデスクでできているのだから、ちゃんと動いて当たり前だが。そこでFORTHの仮想コードを書いて、スタックマシンが想定どおりに動いていることを確認してみた。

3 DUP +

これまた至極当然だが、我が超マシンはスタックに6という値を積んだ。背筋がぞくっとした。これぞ長年の夢、汎用CPUのソフトでシミュレートするのではなく、ハードウェアで実現したスタックマシンだ。それがいま動いたんだよおっかさん。

もちろんまだ実験段階だ。ちゃんとした実装にはなっていない。これからちょっとずつ、実装を進めていくつもりだ。

また来週。(^^)