Altera DE0のJTAG通信?の続きになります。

AlteraのQuartusは9.1から一番小さなNIOS/eが無料で使えるようになりました(marseeさん情報ありがとうございます)。9.0まではどうだったかというと、FPGAボードにsofファイルをダウンロードすると、Quartusからダイアログボックスが出て、ボタンを押すまでは使えるという変則時限使用が可能でした。

やたら手順は長いですが、覚書きがわりに手順を追っかけてみます。

おおざっぱな流れは、

(1) Quartusで新規プロジェクトを作る

(2) デバイスの設定をする

(3) SOPC Builderを起動してCPU(NIOS II)やメモリ、ペリフェラルの設定をしてシステムをGenerateする

(4) Quratusに戻って、トップモジュールやペリフェラルのRTLを作ってFPGAボードにダウンロードする

(5) NIOS II eds(エンベデッド・デザイン・スイート)を起動してCのプログラムを作って、FPGAボードにダウンロード&実行する

くらいになります。FPGAの部屋さんのまとめサイトを参考にしました。

(0) インストール

Quartus II web editionとNiosNios II エンベデッド・デザイン・スイートをAlteraのダウンロードページからダウンロードしてインストールします。昔と違ってライセンスを取得する必要はなくなりました。

(1) Quartus IIの新規プロジェクトを作る

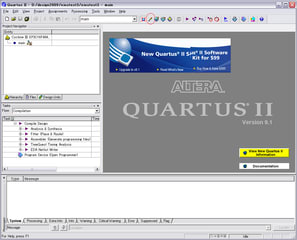

Create a New Projectを押します。

次の画面はNextを押します。

プロジェクトのディレクトリ(d:¥design2009¥niostest3)、プロジェクト名(niostest3)、トップモジュール名(main)を入力してNextを押します。

次の画面はNextを押します。

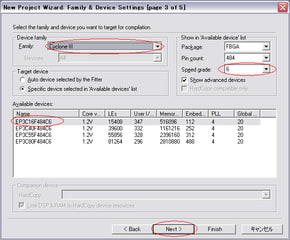

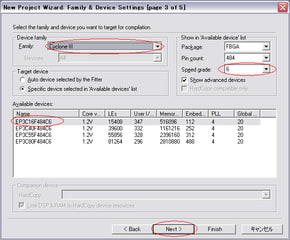

デバイスを選択します。DE0ボードは、FamilyがCyclone III、Speed gradeが6、デバイス名はEP3C16F484C6です。Nextを押します。

次の画面はNext、その次の画面はFinishを押します。

これでprojectができました。

(2) デバイスの設定

後でやってもいいのですが、忘れないように、まずはsettingで、デバイス関連の設定をしておきます。

settingボタンを押します。もしくはメニューのAssignments→Settingを選びます。もしくはctrl+shift+Eを押します。

左側のCategoryというツリービューのDeviceをクリックします。

次にDevice and Pin Options...というボタンを押します。

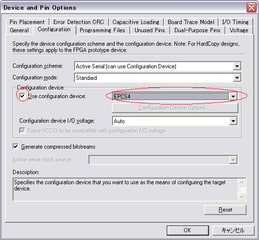

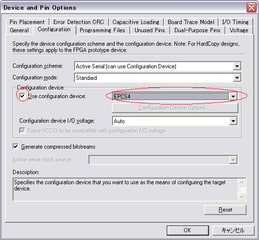

Configurationというタブを選んでUse configuration deviceというチェックボックスをチェックしてから右のドロップメニューからEPCS4を選びます。こうすることでeeprom用の書き込みファイル(.pof)を生成してくれるようになります。

他にUnused Pinsというタブで未使用ピンのデフォルトの入出力を決めてやります。

またVoltageというタブでデフォルトのI/Oを選びます(3.3V LVTTL)。

OKを押してDevice and Pin Optionsのダイアログを閉じます。

OKを押してSettingsのダイアログを閉じます。

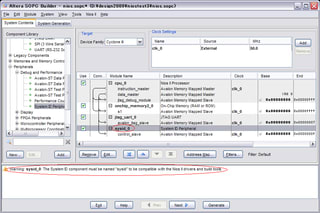

(3) SOPC BuilderでNIOSを設定する

右上のSOPC Builderのボタンを押して、SOPC Builderを起動します。もしくはToolsメニューのSOPC Builderメニューで起動します。

一番最初のダイアログでシステム名(nios)の入力、HDLの選択(Verilog)をしてからOKを押します。

今回は、システムを動かす最低限の設定だけをすることにします。

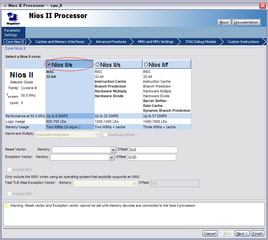

まずは左側のLibraryというツリービューのProssorsを開いてNios II ProcessorをダブルクリックしてシステムにNiosを追加します。もしくはAddボタンを押します。

ここのところは9.0と違っています。9.0ではNiosはLibraryの中にはありませんでした。

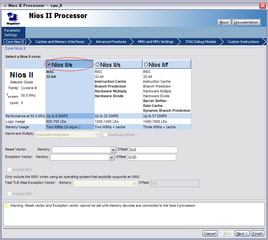

Nios II/eを選んでFinishを押します。

この画面には後で戻ってきてMemoryのプルダウンメニューを選びます。今はまだメモリーがないのでFinishにしておきます。Nextを進んでいくとデバッグのレベルを選べます。

LibraryツリービューのMemories and Memory Controllers → On-Chip → On-Chip MemoryをダブルクリックしてFPGA上のメモリを追加します。もしくはAddボタンを押します。

メモリーサイズを入力します。とりあえず32768バイトにしてみました。たぶん、もっと増やせます。Finishボタンを押します。

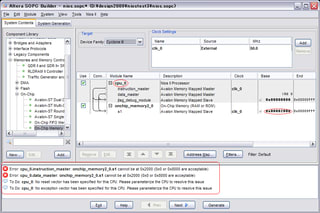

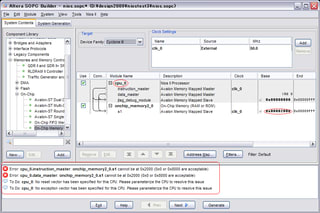

ここでエラーが出ます。32kバイトにしたときはメモリの開始番地を0x0または0x8000にしろというエラーです。現在の値は0x2000になっています。それとしなければいけないこと(To Do)としてcpu_0のリセットベクトルと例外ベクトルを指定しろと出てきます。

まずはonchip_memory2_0の右側の0x00002000をダブルクリックして編集します。0x00008000に変更すると、エラーが消えます。

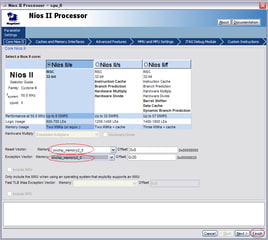

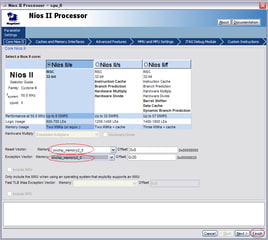

次にcpu_0をダブルクリックしてNiosの設定に戻ります

Reset VectorのところとException Vectorのところのプルダウンメニューからonchip_memory2_0を選びます。Finishボタンを押して戻ります。

To Doも消えています。

方針としてエラーとかTo doが出たら、とりあえず消すようにするのがいいみたいです。

次にJTAG UARTを追加します。JTAG UARTは左側のLibraryツリービューのInterface Protocols → Serial → JTAG UARTにあります。ダブクリまたはAddボタンでJTAG UARTのダイアログを出してからFinishを押して、システムに追加します。

最後はSystem IDを追加します。System IDは左側のLibraryツリービューのPeripherals → Debug and Performance → System ID Peripheralsにあります。これもダブクリまたはAddボタンでSystem ID Peripheralのダイアログを出してからFinishを押してシステムに追加します。

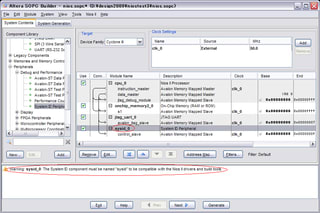

ここでwarningが出ます。

System IDは追加するだけでは駄目でモジュール名をsysid_0からsysidに変更する必要があります。

sysid_0のところをクリックしてから、右クリックメニューでRenameを選ぶか、ctrl+Rを押すことで名前を変更できます。sysidに変更するとwarningが消えます。

今回はしませんが、この段階で考慮しておくべきこととして、クロックやモジュールの名前を分かりやすいものに変更しておくことがあります。また、複数のクロックがある場合には各モジュールに供給するクロックを選択する必要があります。

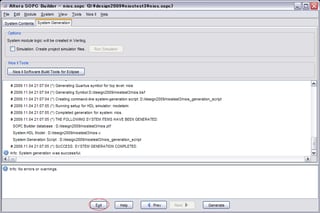

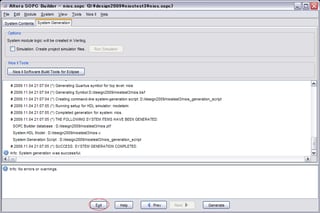

ここまでくると、後はシステムを生成(Generate)します。Saveするか聞いてくるのでSaveボタンを押します。しばらく時間はかかりますが、正常に生成し終わると次のような画面が出てきます。

一番下にはSUCCESS: SYSTEM GENERATION COMPLETEDというメッセージが出ています。

EXITボタンを押してSOPC Builderを終了します。

(4) Quartusで論理合成

とりあえず、ここまでで、5段階のうち3段階が終わりました。

(2)は、先にやっておかなくても、(4)のときに一緒にしてもいいです。

どどっと疲れてきたので、(4)は手抜きします。

まずは、main.vを作ります。mainという名前は(1)のときにトップモジュールとしてmainにしたからです。今回は何もペリフェラルの追加を行っていないので、mainはniosを呼び出すだけのモジュールになります。ここのniosというのは、(3)でシステム名をniosにしたからです。他の名前にしたときは、その名前になります。niosの呼び出し方はSOPC Generatorがnios_inst.vというファイルを作ってくれるので、これをコピペします。

nios_inst.vの中身です。

リセットとクロックしかいません。

コピペして作ったmain.vです。

クロックをclk、リセットをrst_xという名前にしています。

main.vを追加するには、Quartusの外でテキストエディタを使ってmain.vを作ってからシステムに追加(Projectメニュー → Add/Remove files in Project)したり、Fileメニュー → New → Verilog HDL Fileを選んでから、中身を作ってFileメニュー → Save Asでmain.vと名前をつけてセーブする方法があります。

Pin Plannerを使って、ピン配置を決めます。clkはPIN_G21、rst_xはPIN_F1(ボタン2)にしました。

タイミング制約をつけてやります。50MHzです。

ようやっと論理合成できます。

warningが55個も出ています。

ロジックエレメント(LE)は1379 / 15408 (9%)でした。

Timing Analyzerを見てもfailしているパスはなく全てmetしています。

118MHzで動作する回路ができたようです。

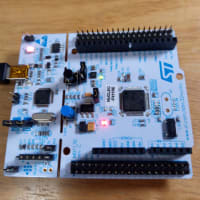

Programmerを起動して、回路を書き込みます。

LEDがうっすらとついています。未使用ピンをハイインピーダンスにしたせいです。

というわけで、疲れてきたので続きます。

AlteraのQuartusは9.1から一番小さなNIOS/eが無料で使えるようになりました(marseeさん情報ありがとうございます)。9.0まではどうだったかというと、FPGAボードにsofファイルをダウンロードすると、Quartusからダイアログボックスが出て、ボタンを押すまでは使えるという変則時限使用が可能でした。

やたら手順は長いですが、覚書きがわりに手順を追っかけてみます。

おおざっぱな流れは、

(1) Quartusで新規プロジェクトを作る

(2) デバイスの設定をする

(3) SOPC Builderを起動してCPU(NIOS II)やメモリ、ペリフェラルの設定をしてシステムをGenerateする

(4) Quratusに戻って、トップモジュールやペリフェラルのRTLを作ってFPGAボードにダウンロードする

(5) NIOS II eds(エンベデッド・デザイン・スイート)を起動してCのプログラムを作って、FPGAボードにダウンロード&実行する

くらいになります。FPGAの部屋さんのまとめサイトを参考にしました。

(0) インストール

Quartus II web editionとNiosNios II エンベデッド・デザイン・スイートをAlteraのダウンロードページからダウンロードしてインストールします。昔と違ってライセンスを取得する必要はなくなりました。

(1) Quartus IIの新規プロジェクトを作る

Create a New Projectを押します。

次の画面はNextを押します。

プロジェクトのディレクトリ(d:¥design2009¥niostest3)、プロジェクト名(niostest3)、トップモジュール名(main)を入力してNextを押します。

次の画面はNextを押します。

デバイスを選択します。DE0ボードは、FamilyがCyclone III、Speed gradeが6、デバイス名はEP3C16F484C6です。Nextを押します。

次の画面はNext、その次の画面はFinishを押します。

これでprojectができました。

(2) デバイスの設定

後でやってもいいのですが、忘れないように、まずはsettingで、デバイス関連の設定をしておきます。

settingボタンを押します。もしくはメニューのAssignments→Settingを選びます。もしくはctrl+shift+Eを押します。

左側のCategoryというツリービューのDeviceをクリックします。

次にDevice and Pin Options...というボタンを押します。

Configurationというタブを選んでUse configuration deviceというチェックボックスをチェックしてから右のドロップメニューからEPCS4を選びます。こうすることでeeprom用の書き込みファイル(.pof)を生成してくれるようになります。

他にUnused Pinsというタブで未使用ピンのデフォルトの入出力を決めてやります。

またVoltageというタブでデフォルトのI/Oを選びます(3.3V LVTTL)。

OKを押してDevice and Pin Optionsのダイアログを閉じます。

OKを押してSettingsのダイアログを閉じます。

(3) SOPC BuilderでNIOSを設定する

右上のSOPC Builderのボタンを押して、SOPC Builderを起動します。もしくはToolsメニューのSOPC Builderメニューで起動します。

一番最初のダイアログでシステム名(nios)の入力、HDLの選択(Verilog)をしてからOKを押します。

今回は、システムを動かす最低限の設定だけをすることにします。

まずは左側のLibraryというツリービューのProssorsを開いてNios II ProcessorをダブルクリックしてシステムにNiosを追加します。もしくはAddボタンを押します。

ここのところは9.0と違っています。9.0ではNiosはLibraryの中にはありませんでした。

Nios II/eを選んでFinishを押します。

この画面には後で戻ってきてMemoryのプルダウンメニューを選びます。今はまだメモリーがないのでFinishにしておきます。Nextを進んでいくとデバッグのレベルを選べます。

LibraryツリービューのMemories and Memory Controllers → On-Chip → On-Chip MemoryをダブルクリックしてFPGA上のメモリを追加します。もしくはAddボタンを押します。

メモリーサイズを入力します。とりあえず32768バイトにしてみました。たぶん、もっと増やせます。Finishボタンを押します。

ここでエラーが出ます。32kバイトにしたときはメモリの開始番地を0x0または0x8000にしろというエラーです。現在の値は0x2000になっています。それとしなければいけないこと(To Do)としてcpu_0のリセットベクトルと例外ベクトルを指定しろと出てきます。

まずはonchip_memory2_0の右側の0x00002000をダブルクリックして編集します。0x00008000に変更すると、エラーが消えます。

次にcpu_0をダブルクリックしてNiosの設定に戻ります

Reset VectorのところとException Vectorのところのプルダウンメニューからonchip_memory2_0を選びます。Finishボタンを押して戻ります。

To Doも消えています。

方針としてエラーとかTo doが出たら、とりあえず消すようにするのがいいみたいです。

次にJTAG UARTを追加します。JTAG UARTは左側のLibraryツリービューのInterface Protocols → Serial → JTAG UARTにあります。ダブクリまたはAddボタンでJTAG UARTのダイアログを出してからFinishを押して、システムに追加します。

最後はSystem IDを追加します。System IDは左側のLibraryツリービューのPeripherals → Debug and Performance → System ID Peripheralsにあります。これもダブクリまたはAddボタンでSystem ID Peripheralのダイアログを出してからFinishを押してシステムに追加します。

ここでwarningが出ます。

System IDは追加するだけでは駄目でモジュール名をsysid_0からsysidに変更する必要があります。

sysid_0のところをクリックしてから、右クリックメニューでRenameを選ぶか、ctrl+Rを押すことで名前を変更できます。sysidに変更するとwarningが消えます。

今回はしませんが、この段階で考慮しておくべきこととして、クロックやモジュールの名前を分かりやすいものに変更しておくことがあります。また、複数のクロックがある場合には各モジュールに供給するクロックを選択する必要があります。

ここまでくると、後はシステムを生成(Generate)します。Saveするか聞いてくるのでSaveボタンを押します。しばらく時間はかかりますが、正常に生成し終わると次のような画面が出てきます。

一番下にはSUCCESS: SYSTEM GENERATION COMPLETEDというメッセージが出ています。

EXITボタンを押してSOPC Builderを終了します。

(4) Quartusで論理合成

とりあえず、ここまでで、5段階のうち3段階が終わりました。

(2)は、先にやっておかなくても、(4)のときに一緒にしてもいいです。

どどっと疲れてきたので、(4)は手抜きします。

まずは、main.vを作ります。mainという名前は(1)のときにトップモジュールとしてmainにしたからです。今回は何もペリフェラルの追加を行っていないので、mainはniosを呼び出すだけのモジュールになります。ここのniosというのは、(3)でシステム名をniosにしたからです。他の名前にしたときは、その名前になります。niosの呼び出し方はSOPC Generatorがnios_inst.vというファイルを作ってくれるので、これをコピペします。

nios_inst.vの中身です。

//Example instantiation for system 'nios'

nios nios_inst

(

.clk_0 (clk_0),

.reset_n (reset_n)

);

リセットとクロックしかいません。

コピペして作ったmain.vです。

`default_nettype none

module main(

input rst_x,

input clk);

//Example instantiation for system 'nios'

nios nios_inst (

.clk_0 (clk),

.reset_n (rst_x)

);

endmodule

クロックをclk、リセットをrst_xという名前にしています。

main.vを追加するには、Quartusの外でテキストエディタを使ってmain.vを作ってからシステムに追加(Projectメニュー → Add/Remove files in Project)したり、Fileメニュー → New → Verilog HDL Fileを選んでから、中身を作ってFileメニュー → Save Asでmain.vと名前をつけてセーブする方法があります。

Pin Plannerを使って、ピン配置を決めます。clkはPIN_G21、rst_xはPIN_F1(ボタン2)にしました。

タイミング制約をつけてやります。50MHzです。

ようやっと論理合成できます。

warningが55個も出ています。

ロジックエレメント(LE)は1379 / 15408 (9%)でした。

Timing Analyzerを見てもfailしているパスはなく全てmetしています。

118MHzで動作する回路ができたようです。

Programmerを起動して、回路を書き込みます。

LEDがうっすらとついています。未使用ピンをハイインピーダンスにしたせいです。

というわけで、疲れてきたので続きます。

私もNios2/eがフリーになるのはtwitter で教えてもらいました。

質問なのですが、今、Quartus2 Ver.9.0をインストールしてあるのですが、Quartus2 Ver.9.1をインストールしても2つとも使えますか?ご存じでしたら、よろしくお願いします。

私は、Ver. 9.0sp1とVer. 9.1をインストールしていますが、今のところ2つとも使えました。

idlef54さん、フォローありがとうございます。marseeさん、デフォルトだとバージョン毎に別のフォルダーにインストールしているので、なんとなく使えそうな雰囲気です。私も今のところ問題なく使えています。

安心してQuartus2 9.1がインストールできます。

Simさん、チュートリアルをがんばってください。期待しています。

9.1のNios II edsは微妙に使い方が変わっていました。一応できたことにして公開しておきました。

marseeさんのチュートリアルがなければ全く手も足もでなかったので、たいへん感謝しておりますm(_ _)m

それに付いていたQuartus7を入れました。

30日間のライセンスだったので

ウェブでライセンスファイルを取得して

150日にしましたが…150日後には…

>昔と違ってライセンスを取得する必要はなくなりました。

8.1からライセンスは不要とか

でもレガシーは使えないよと書いてある。

レガシーって何?

レガシーと150日間のはざまでさ迷う私

レガシーって何?

ちっちゃなデバイス(MAXとかCyclone)を使うときはwebpack版で十分です。

レガシーは、よく分からないですが、現在のQuartusでサポートしているデバイスを見るとACEXとかFLEXの名前がありません。もしかすると、このあたりのデバイスのことかもしれません。

参考 http://www.altera.co.jp/literature/po/ss_quartussevswe.pdf