NIOSを使ってみました(1)の続きになります。

NIOS IIのトリビアルな実装をしています。

(5) NIOS II eds(エンベデッド・デザイン・スイート)を起動してCのプログラムを作って、FPGAボードにダウンロード&実行する

いよいよ最後のステップです。

NIOS II edsを立ち上げると最初にworkspaceをどこにするかを聞いてきます。

Quartusのプロジェクトフォルダと一緒にするのがてっとりばやいです。一段階Softwareというフォルダを掘ってくれるので、ファイルが混ざったりすることもありません。

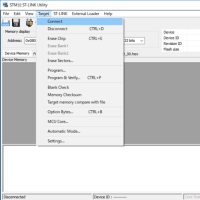

Fileメニュー → New → NIOS II Aplication and BSP from Templateを選びます。

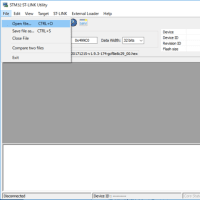

SOPC Information File Nameの欄にはQuartusのプロジェクトのフォルダにあるnios.sopcinfoを選びます。niosの部分はSOPC Builderの一番最初で決めたシステム名になります。

Project名を決めてやります。niostest3にしました。

左下のテンプレートはHello World Smallを選びました。このテンプレートは使用メモリが少ないのでブロックRAM上でも動作します。

Finishボタンを押します。

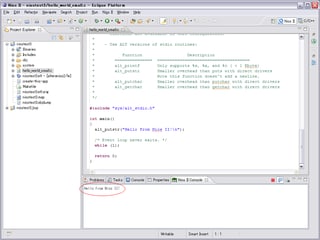

左のProject Explorerツリービューのプロジェクト名(今回はniostest3)をクリックして灰色に変えてから、Projectメニュー → Build Projectでプロジェクトをビルドします。

Runメニュー → Runを選びます。

Run Asというダイアログが出るのでNIOS II Hardwareを選んで(クリックして灰色に変えて)、OKを押します。

下のNios II Consoleに実行結果が出ます。今回は"Hello from Nios II!"というメッセージを表示します。中のプログラムは以下のようなものです。

ペリフェラルはsystem.hにメモリの番地が書いてあったりしますが、今回は何もないのでincludeしなくても平気です。

リセット(ボタン2)を押すともう一度"Hello from Nios II!"を表示してくれます。

このプログラムは無限ループなのでNios II Consoleの右上にある赤い四角を押してプログラムを終了してやります。

さて、以上で駆け足でしたがQuartusのプロジェクト作成から始まってNIOS II eds上での実行まで眺めてきました。結構、長いですね。

FPGAの部屋さんのまとめサイトを見ながら、独自ペリフェラル(Avalon-MMのスレーブ)を作ってみたりしました。

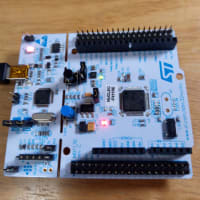

これからやりたいのは、DE0に搭載されているSDRAMをNiosから使うことです。

分かっていないのは、Nios II上で開発したソフトをROM化する方法です。PCと通信しなくても電源オンですぐ動き出すようにしたいです。ブロックRAMと同じ名前の.hexファイルがあって、これがブロックRAMの初期値になるんじゃないかと思います。.elfファイルを.hexに変換するツールとかがあるのかもしれません。

それにしても、1週間たらずのうちに2度もQuartusをインストールすることになるとは思ってませんでした。

おまけです。

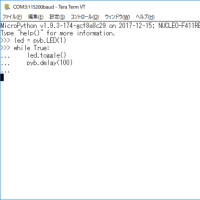

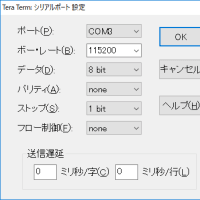

NIOS II edsをインストールしたフォルダの下のbinというフォルダにnios2-terminal.exeというプログラムがあります。このプログラムを使うとNIOS II edsを使わなくてもDE0ボードと通信できます。TeraTermのJTAG UART版みたいなプログラムです。

NIOS IIのトリビアルな実装をしています。

(5) NIOS II eds(エンベデッド・デザイン・スイート)を起動してCのプログラムを作って、FPGAボードにダウンロード&実行する

いよいよ最後のステップです。

NIOS II edsを立ち上げると最初にworkspaceをどこにするかを聞いてきます。

Quartusのプロジェクトフォルダと一緒にするのがてっとりばやいです。一段階Softwareというフォルダを掘ってくれるので、ファイルが混ざったりすることもありません。

Fileメニュー → New → NIOS II Aplication and BSP from Templateを選びます。

SOPC Information File Nameの欄にはQuartusのプロジェクトのフォルダにあるnios.sopcinfoを選びます。niosの部分はSOPC Builderの一番最初で決めたシステム名になります。

Project名を決めてやります。niostest3にしました。

左下のテンプレートはHello World Smallを選びました。このテンプレートは使用メモリが少ないのでブロックRAM上でも動作します。

Finishボタンを押します。

左のProject Explorerツリービューのプロジェクト名(今回はniostest3)をクリックして灰色に変えてから、Projectメニュー → Build Projectでプロジェクトをビルドします。

Runメニュー → Runを選びます。

Run Asというダイアログが出るのでNIOS II Hardwareを選んで(クリックして灰色に変えて)、OKを押します。

下のNios II Consoleに実行結果が出ます。今回は"Hello from Nios II!"というメッセージを表示します。中のプログラムは以下のようなものです。

#include "sys/alt_stdio.h"

int main()

{

alt_putstr("Hello from Nios II!¥n");

while(1) ;

}

ペリフェラルはsystem.hにメモリの番地が書いてあったりしますが、今回は何もないのでincludeしなくても平気です。

リセット(ボタン2)を押すともう一度"Hello from Nios II!"を表示してくれます。

このプログラムは無限ループなのでNios II Consoleの右上にある赤い四角を押してプログラムを終了してやります。

さて、以上で駆け足でしたがQuartusのプロジェクト作成から始まってNIOS II eds上での実行まで眺めてきました。結構、長いですね。

FPGAの部屋さんのまとめサイトを見ながら、独自ペリフェラル(Avalon-MMのスレーブ)を作ってみたりしました。

これからやりたいのは、DE0に搭載されているSDRAMをNiosから使うことです。

分かっていないのは、Nios II上で開発したソフトをROM化する方法です。PCと通信しなくても電源オンですぐ動き出すようにしたいです。ブロックRAMと同じ名前の.hexファイルがあって、これがブロックRAMの初期値になるんじゃないかと思います。.elfファイルを.hexに変換するツールとかがあるのかもしれません。

それにしても、1週間たらずのうちに2度もQuartusをインストールすることになるとは思ってませんでした。

おまけです。

NIOS II edsをインストールしたフォルダの下のbinというフォルダにnios2-terminal.exeというプログラムがあります。このプログラムを使うとNIOS II edsを使わなくてもDE0ボードと通信できます。TeraTermのJTAG UART版みたいなプログラムです。

短期間でお疲れでしょうから、積極的な質問ではありませんが。幾つか疑問があります。

お時間の合った時でももしわかれば教えて下さい。自分でも何かの機会に調査してみます。

1.自作アプリとも通信できる?(Nios II Consoleではなくて)

2.PCとのスループットは?

3.>Nios II上で開発したソフトをROM化する

できたとしてライセンス発生するのかしら

SDRAMは簡単に追加できたと思います。ただ私の場合、ポートの属性を間違ってえらい手間がかかりました。

ROM化はブートにFPGA内蔵のRAMかROMを使うとすると、そこに初期値として入れればよいと思いますが、大きなプログラムだとブートローダーを作ってシリアルとか、LANからロードする必要があるんでしょうね?

自分のまとめサイトを見たんですが、分かりにくいです。やはり時系列に並べなおしたまとめも作りたいと思いました。

とりあえず、やたら便利なのは確かです。質問の答えは探してみたけど、よく分からない状況です。

アプリとの通信は状況として以前と変わらないです。Terasicのデモも今回のJTAG-UARTを使ってるっぽいのでPC側のdllが必要です。ちょっと変わったのはTerasicでなく、Altera純正のdllが何かあるはずというくらいです。スループットはそんなに速くなさそうです。ROM化はelf2hexというバイナリファイルがNios II edsにありました。どうやって使うのかまでは不明です。もしかするとobjdumpみたいなものを使うのかもしれません。

ファイルはいっぱいあるし、ドキュメントもいっぱいあって迷子状態です。

SDRAMも無事動きました。オンチップメモリだと動かない大きなサンプルも動かすことができました。

DE0に搭載されているSDRAMとCDに入っていたデータシートは異なっていました。166MHz動作のものみたいです。

SDRAMって、50MHzで166MHzより遅く動かしても動くんですね。全然知りませんでした。遅く動作させているせいか、タイミングの所は何も入力しないでデフォルトのままで動きました。PLLの位相は-60度にしました。SDRAMってクロックに同期して動くものだと思っていたので、クロックの位相をずらすのは不思議でした。これは何のためにしているんでしょうか?

AN548というアプリケーションノートにフラッシュからブートするシステムの例が載っているようでした。

>アプリとの通信は状況として以前と変わらない

アプリ環境の解析は可能だと思いますがNios IIでも公開されていないということであればそういうものなのだと思います。これはデバッグ環境でありその中で使用して下さいみたいな。Nios II環境、これはトレーニング用で利用する良い物だと思います。

FT245はUSB1.1みたいですね。USB1パケット64バイトで、MAX2でシリアルのJTAGに載せかえるわけだから速度的には期待できるものではないですね。

私は、USB経由でFPGAコンフィグ、アプリ通信ができるものを作りました。

サイプレスFX2、Virtex、CoolRunner、FlashROMの構成です。別な方法があるかなとか思っていたので今回のスレッドは興味があった次第でした。

おめでとうございます。

>SDRAMって、50MHzで166MHzより遅く動かしても動くんですね。

SDRAMはDLLが付いていないし、最低動作周波数はないみたいです。

>PLLの位相は-60度にしました。SDRAMってクロックに同期して動くものだと思っていたので、クロックの位相をずらすのは不思議でした。これは何のためにしているんでしょうか?

Alteraのことはよくわからないし、回路タイミングも不明なので良くわからないのですが、PLLの位相が-で進む方向なので、ホールドタイムのマージンを取っているんでしょうか?

http://www.altera.co.jp/literature/hb/qts/qts_qii54006_j.pdf

を見ても-63度ですが、調整する必要があると書いてあります。

なるほど自作されたんですね。コンフィグとアプリ通信の切り替えはどのようにされていますか?

AlteraのJTAG-UARTはJTAGのユーザー定義拡張みたいなコマンドを使って実現しているようです。JTAGはPC側からコマンドを送って結果を返してもらうのが基本なので、FPGAボードからの送信はPC側から送ってと頼まれるとFPGAが送信データを送るという流れになるはずで、このあたりは定期的にコマンドを投げてサンプリングしてやらないといけないはずです。基本がJTAGなので、スピードが出ないという話だと思ってます。ユーザから制御しようと思うとJTAGを全部しゃべれるプログラムを書くというのも手として考えられますが、それはそれでたいへんです。

教えていただいたpdfを勉強してみました。コンフィグROMにプログラムを置くなんてできるんですね。

ROM化の方はNIOS II command shellでelf2hexを使ってhexファイルを作ってやることで、一応できました。オンチップRAMの初期値をいれてやったことになります。まだオンチップRAMしかない単純な構成でしか試していません。

どうせならオンチップRAM+SDRAMの構成でできるとうれしいのですが、まだ試していません。

IDをUSB先頭パケットに付けて動作を区別しています。コンフィグID、xxIDというぐあいです。

コンフィグIDのセカンドIDに、FLASH更新、FLASHベリファイ、コンフィグ起動、FPGAリセットなどあります。これらを組み合わせると実現できます。

コンフィグの実現の詳細は複雑で書ききれないので詳細はやめときますが、簡単にいうと、

マスタ SelectMAP(8bit)方式です。高速にシンプルにコンフィグするにはこれが良いと思いましたのでこの方式です。

データは、FlashROMに格納し、CoolRunnerがシーケンスを管理しています。

トレーニングボードのUSBの件はおかげで理解できました。この話題はcloseします。有難う御座いました。

有益ネタですが製品に使えるネタとは判断できませんでした。

なるほど、それは速そうですね。AlteraのはJTAGに乗っけているので、遅いかわりにコンフィグとかに特別なことをしなくてもいい利点があります。

色々お付き合いいただきありがとうございました。