ISE8.1のcore generatorを使えば、block ramを使用したROM/RAMを簡単に作れます。付録DVDに入っていたISE9.1でも同様にできると思います(無責任モード)。

まず、ROMの内容を書いたテキストファイル(coeファイル)を作ります。拡張子は.coeにします。ほとんどべたファイルなのですが、少しだけお約束があります。

(1) 1行目はMEMORY_INITIALIZATION_RADIX=16;にします。これは16進を使うことを指定しています。

(2) 2行目はMEMORY_INITIALIZATION_VECTOR=にします。

(3) 3行目以降はコンマ(,)で区切って16進2桁ずつROMの内容を書きます。1行に何個データを書くとかのルールはないようです。

(4) データの最後はセミコロン(;)にします。

こんな感じになります(mona9.coe)。

MEMORY_INITIALIZATION_RADIX=16;

MEMORY_INITIALIZATION_VECTOR=

ff,ff,ff,ff,ff,ff,ff,ff,ff,ff,ff,ff,

80,00,00,00,00,00,00,00,00,00,00,00,

(中略)

ff,ff,ff,ff,ff,ff,ff,ff,ff,ff,ff,ff;

さて、iseの使い方です。まずメニューのProject → New Sourceを選ぶとNew Source Wizardが起動します。

この画面では、左側の一覧からIP (Coregen & Architecture Wizard)をシングルクリックして選択して、File Nameに作りたいコアの名前を入れます。今回はromにします。この2つを入力するとNextボタンが灰色じゃなくなって選択できるようになります。

他にすることもないのでNextボタンを押して次の画面に進みます。

この画面では作成するIPを選択します。ツリービューになつているので+を押して展開していきます。Memories & storage Elements → RAMs & ROMsを開いてSingle Port Block Memoryをシングルクリックして選択します。

Nextボタンを押すと確認の画面になるのでFinishを押すとcore generatorが起動します。

最初の画面では以下を行います。

(1) Read Onlyのラジオボタンを押してROMにします

(2) Width(データのbit幅)を8bitにします

(3) Depth(データの個数)を9216(= 9x1024)にします

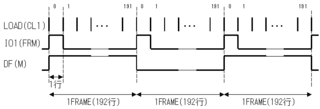

最後の9216というのは鈴商液晶が384x192dotなので9216バイト(= 384x192/8)であることを指定しています。

Nextボタンを3回押して4page目に移動します。

この画面では、先ほど作ったcoeファイルを指定します。Load Init FileのチェックボタンをチェックするとLoad Fileボタンが有効になります。Load Fileボタンを押すとファイル選択のダイアログで出てくるので選択してやります。

これで設定はできたので左下のGenerateボタンを押してしばらく待つとROMの出来上がりです。隣のDismissボタンを押すと全部キャンセルされてしまうので間違って押さないようにします。

今回作ったROMはblock ramから作られているので、アドレスを指定した次のクロックでデータが出力されます。

block ramは1個あたり2kバイトです。今回は9k byteのROMを作ったので5個のblock ramを使用します。DWM付録基板のxc3s250eは全部で12個のblock ramが搭載されています。24kバイトのROMまたはRAMが使えることになります。

(正確には16kbitではなくパリティもあるので18kbitですが、8bit幅にすると2kバイトまでしか使用できません)

論理合成するとISEの右側の画面にDesign Summaryが表示されますが、この中にblock ramの使用状況も表示されます(今回のは5個)。

core generatorを使えばデュアルポートRAMも簡単に作れます。

ROMを作る他の方法としては以下があります。

(1) alwaysとcaseで作る。ISEはblock ramを推論してくれます。

(2) initial中で初期化する。ただし全データを設定してやる必要があります。ISEはblock ramを推論してくれます。テストベンチだけでなく、論理合成のときにinitialが使えるのはたぶんise特有だと思います。

(3) アトリビュートのINIT_xxに書いてやる。block ramを1つずつインスタンス化しないといけないません。インスタンス化のときに#( )の中に書く方法と// synthesis attributeで書く方法があります。language templateは#( )の方法になっています。

(4) ucfファイルの中で指定(?)。これはやってみたことがないのでよく分かりません。もしかしたらxcfファイルかもしれません。

(5) data2memユーティリティを使って直接bitファイルを書き換える。これには.bmmファイルと.memファイルを作ってやる必要があります。EDKはこの方法でblock ramを書き換えています。data2memの使い方は

FPGAの部屋さんで何回か取り上げられています。

他にもあると思いますが知っているのはこのくらいです。