ナノテクノロジーの大きな目標の一つは、ナノサイズのエレクトロニクス素子を集めて集積回路(コンピューターチップ)を作ることにある(ボトムアップ方式、8/18参照)。現在コンピュータチップの生成に使われているトップダウン方式が限界に近づきつつあるが、ボトムアップ方式が機能し始めるまでにはまだまだ時間がかかりそうだ。

当面を切り抜けるいくつかの方法が試みられている。IBMは3次元エレクトロニクスを打ち上げている(http://www.smartertechnology.com/c/a/Optimized-Systems/IBM-and-3M-Herald-New-Era-of-3D-Electronics/)。これは、現在用いられているコンピュータチップを重ね合わせてその占有する場所を小さくしようとするものである。

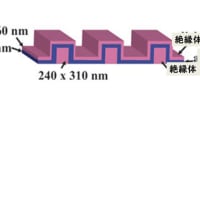

3次元エレクトロニクスの問題の一つは、チップ間の接続方法である。有望視されているのは、TSV(through-silicon via)と呼ばれる方法である。viaは貫通孔を意味し、TSVとは基盤のシリコンに孔を開け導体を通して接続しようとするものである。導体にはこれまで銅線が多く使われて来たが、最近スウェーデンの研究者たちは、貫通孔の中にカーボンナノチューブの森(10/25参照)を成長させ他のシリコンチップと接続することに成功した*。カーボンナノチューブで接続すると、電気伝導度が高いこと、発生する熱量が少ないこと、柔軟性に富むこと、熱膨張が少ないことなど多くの利点がある。

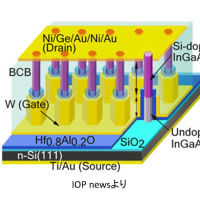

ニューヨークタイムスの記事(12/5付)によると、インテル(INTEL)も独自の方法で3次元エレクトロニクスを開発している。詳細はよく分からないが、シリコンの基盤の上に多数のカーボンナノチューブトランジスタ(10/31参照)を垂直に立てたものもののようである。この計画にはカリフォルニア大学のグループが協力している。このほか、酸化チタンやガリウムヒ素をシリコンに置き換えようとする試みもある。いずれにしても、現在のシリコン平面型コンピューターチップを用いる限り、コンピューターの計算スピードの上昇を試みると、コンピューターが大型になり多大の電力を消費し熱を発生する。2019年までに計算速度を1000倍にしようとする計画もある中で、3次元エレクトロニクスの益々の進歩が期待出来る。

*http://www.nanowerk.com/news/newsid=23716.php?utm_source=feedburner&utm_medium=email&utm_campaign=Feed%3A+nanowerk%2FagWB+%28Nanowerk+Nanotechnology+News%29

最新の画像[もっと見る]

-

海水の淡水化 I

10年前

海水の淡水化 I

10年前

-

持続可能な開発と ナノテクノロジー

10年前

持続可能な開発と ナノテクノロジー

10年前

-

再び"透明マント"

12年前

再び"透明マント"

12年前

-

原子炉専門家よ 反省・奮起を: 日本の原子力産業が衰退する

12年前

原子炉専門家よ 反省・奮起を: 日本の原子力産業が衰退する

12年前

-

Janusナノ粒子の効用:光触媒作用の効率化

12年前

Janusナノ粒子の効用:光触媒作用の効率化

12年前

-

太陽光発電その後

12年前

太陽光発電その後

12年前

-

新しいタイプのナノモーター

12年前

新しいタイプのナノモーター

12年前

-

北大グループが次世代トランジスタへの第一歩を

12年前

北大グループが次世代トランジスタへの第一歩を

12年前

-

電流測定の画期的進歩: 電子1個ずつの測定が可能に

12年前

電流測定の画期的進歩: 電子1個ずつの測定が可能に

12年前

-

大容量電気エネルギーストレージへの新しい道

12年前

大容量電気エネルギーストレージへの新しい道

12年前

※コメント投稿者のブログIDはブログ作成者のみに通知されます