ispLEVERのHELPを見ていて使い方が分かりました。OSCEという内蔵クロック発生モジュールをインスタンス化します。クロック周波数はdefparamで設定します。指定できる周波数は2.5, 3.1, 4.3, 5.4, 6.9, 8.1, 9.2, 10.0, 13.0, 15.0, 20.0, 26.0, 32.0, 40.0, 54.0, 80.0, 163.0 (全部MHz)です。最高で163MHzってすごいですね。精度はどうなんでしょう。

以下のように書きます。

OSCE clkgen(clk);

defparam clkgen.NOM_FREQ = "2.5";

clkgenはインスタンス名なので、好きな名前にできます。defparamの名前と一致させる必要があります。

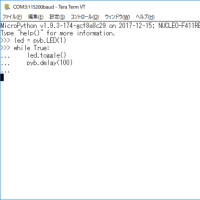

前回のLEDチカチカの内蔵クロック版です。

internal oscillatorで検索すると「How to Use the Internal Oscillator」というトピックが見つかりました。LatticeXP2に搭載されているのはOSCEなので、OSCEで検索して、試した結果が今回の話になります。

以下のように書きます。

OSCE clkgen(clk);

defparam clkgen.NOM_FREQ = "2.5";

clkgenはインスタンス名なので、好きな名前にできます。defparamの名前と一致させる必要があります。

前回のLEDチカチカの内蔵クロック版です。

`default_nettype none

module main(LED);

output reg [1:0] LED = 2'b00;

wire clk;

OSCE clkgen(clk);

defparam clkgen.NOM_FREQ = "40.0";

reg [22:0] ctr;

wire ctr_en = ctr == 0;

always @(posedge clk)

ctr <= ctr + 1;

always @(posedge clk)

if(ctr_en) LED <= LED + 1;

endmodule

internal oscillatorで検索すると「How to Use the Internal Oscillator」というトピックが見つかりました。LatticeXP2に搭載されているのはOSCEなので、OSCEで検索して、試した結果が今回の話になります。

内蔵クロックは便利そうですね。私はx社fpgaですが、内蔵クロックのあるのは知らないですね。CLK系列に24Mはないですが私はUSBで使うので需要は高いと思うのだけど。更にPLLを経由して24M作れるのかもしれませんが。このCLK系列は疑問ですね。

メモリIFは、DDR2-400Mまでサポートしているらしいことがデータシートにありましたが(-7グレード)、だとすると質的にも良いみたいですね。価格的にはX社よりやすいかもしれません。

後から樹脂をとろうと引っ張ったら、

金属が薄いので破れて外れました。

しかもGND側だったので幾ら鏝を当てても抜けずに

結局ドリルで揉みました。

表から着けるとチップが付けられない。

parallaxのような埋め込み型ソケットはどこかで見ませんでしたか?

紙面の方を見て感じたのは、枚数を増やすためか

とっても判りにくく、2点ほど判らないままです。

そこで、手ほどきをお願いしたいのですが、

まずクロックは回路図では33MHzに成っていますが

それ以外の可能性もあるのでしょうか?

(後のFMデジタルチューナでは、73.728MHzに成っています)

それと3.3Vのレギュレータは317Tをお勧めのようですが、

手持ちはAZ1117-ADJなので差し込むと反対側のタブが浮いてしまい、

放熱不足のようです、実際にはどれくらいの電流なのか?

或いは抵抗類を取ってしまって、AZ1086-3.3Vを付けるかなんですが、

AZ1086-Dと有るのが3.3Vなのか確認できません。

このシリーズはADJの方が精度安定度が良いようです。

内蔵クロックでも、こんなにでるものなんですね。たいしたものです。

ええ、私も基本はザイリンクスで、いつものごとく色々浮気してます。

ザイリンクスのDCMみたいな機能もあったりするのかな。後で余裕ができたら調べてみます。DD誌自体には、あまり精度がよくないみたいなことも書いてあるので、正確なクロックが必要なときは、やはり外部クロックなのだと思います。

正確な周波数カウンタがあれば調べられるのでしょうが、ないのでどうしようか思案中です。

例のコネクタというとP-329ですね。下にもささるし、上からも線を挿せるしという使い方ですね。よさげな感じですね。

Parallaxというと、BASIC StampとかPropellerの、あのParallaxですよね?どんなソケットなんでしょう。

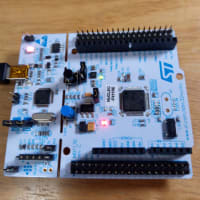

一つ目です。FPGAはクロックはかなり自由です。回路遅延が間に合えば何MHzでも平気です。私はつけはずしできるようにソケットをつけましたが、実際にはCN1のB25ピンから入力できるので、基板表面にはつけない方がいいかもしれません。また内蔵クロックもあるので、クロックをつけなくても遊ぶことはできます。

二つ目です。LEDチカチカを動かす程度で70mA近く流れています。もっと回路規模が大きくなると100mAとかを超えることが考えられます。私は基板上で3.3Vを作らず外部から直接3.3Vを流し込んでいます。

クロックは後から、REGも後から、にします。

信号ヘッダピンをどうしようか考えています。

1,何も無し

2,ピンを上向きに付ける(基板固定が無いので?固定が難しい)

3,ピンをした向きに付ける(背が高くなる、マザーが要る)

4,ソケットを上向きに付ける(単一ピンが刺しにくい)

5,ソケットを下向きに付ける(マザーが要る、使わないともったいない)

長いヘッダピンは何かの時、もう外せなくなるので、

2pinごとに切り離して、ソケットに差して、かためて

半田付けしています、これなら途中抜きも簡単です。

どこかで買った基板部分が少し細くなったヘッダが抜けたりせず、

使いやすいです。(もっと買っておけば良かった)

http://den-nekonoko.blog.so-net.ne.jp/