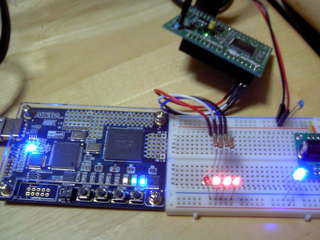

トラ技12月号はAlteraのMAX II マイクロキット上でPICを実装しています。DesignWave 2007年7月号付録のSpartan-3E基板で動かしてみます。

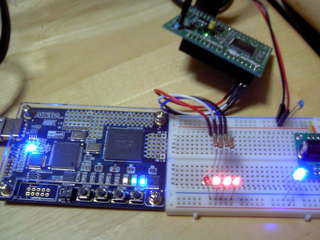

プログラミングケーブルは、Spartan-3 starter kitについてきたものを変換基板を自作してつないでいます(奥に見える黒いのがケーブル)。

自作の変換基板とdigilentのパラレルケーブル

以前、ケーブルも作ったんですが、どこにしまったのか見当たりません><

名前がマイクロキットなだけあって、mmkは小さいです。秋月のブレッドボードとそんなに変わらない大きさです。

ISEは10.1.03です。アップデートにやたら時間がかかりました。

ソースはTR0812T/第3部/MAXII/MaskROMの中にあるものを使いました。

主な変更点はM508Emu.vの(1)入力に外部リセットをつけたことと(2)mResetモジュールを呼ばないようにしたことと、外側にmain.vを作ったことです。

サイズは297 / 2448 slice (12%)で、最大動作周波数は59.291MHzです。オプションはいじっていません。

論理合成のオプションをAREA HIGHにすると、228 / 2448 slice (9%)、39.131MHzになります。DWM付録基板には33MHzのクロックをつけているので、これでもよさそうです。

main.vはリセットとLEDを反転しているだけです。LEDをwireにすると4 slice減ります。

ちなみに、AlteraのQuartus II 8.1で合成したときの結果は728 / 2210 Logic Elementで52.19MHzです。XilinxのsliceとAlteraのLEで数え方がずいぶん違います。

ブロックRAMを使えるように改造できないかといじっていましたが、なかなかうまくいきません。

プログラミングケーブルは、Spartan-3 starter kitについてきたものを変換基板を自作してつないでいます(奥に見える黒いのがケーブル)。

自作の変換基板とdigilentのパラレルケーブル

以前、ケーブルも作ったんですが、どこにしまったのか見当たりません><

名前がマイクロキットなだけあって、mmkは小さいです。秋月のブレッドボードとそんなに変わらない大きさです。

ISEは10.1.03です。アップデートにやたら時間がかかりました。

ソースはTR0812T/第3部/MAXII/MaskROMの中にあるものを使いました。

主な変更点はM508Emu.vの(1)入力に外部リセットをつけたことと(2)mResetモジュールを呼ばないようにしたことと、外側にmain.vを作ったことです。

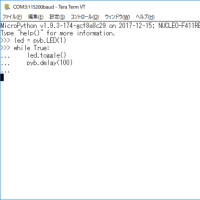

module M508Emu(

input EXTCLK,

input EXTRST, // 追加

・・・

assign reset = EXTRST; // 追加

//Power On Reset ==============================================

// mReset Rst(reset); // コメントアウト

・・・

endmodule

module main(

output reg [3:0] led,

input rst_x, clk);

wire [7:0] led8;

M508Emu cpu(

.EXTCLK(clk),

.EXTRST(~rst_x),

.GPIO(), // inout[7:0]

.LED(led8), // output [7:0]

.KEY(4'hf)); // input [3:0]

always @(posedge clk)

led <= ~led8[3:0];

endmodule

サイズは297 / 2448 slice (12%)で、最大動作周波数は59.291MHzです。オプションはいじっていません。

論理合成のオプションをAREA HIGHにすると、228 / 2448 slice (9%)、39.131MHzになります。DWM付録基板には33MHzのクロックをつけているので、これでもよさそうです。

main.vはリセットとLEDを反転しているだけです。LEDをwireにすると4 slice減ります。

ちなみに、AlteraのQuartus II 8.1で合成したときの結果は728 / 2210 Logic Elementで52.19MHzです。XilinxのsliceとAlteraのLEで数え方がずいぶん違います。

ブロックRAMを使えるように改造できないかといじっていましたが、なかなかうまくいきません。

アドレスによって、直接データを出しているので難しいかと思います。直すのだったら全体的に書き換えないとだめそうです。

CLKでくくらないとBRAMに推論されそうになさそうですね。

はい、御存知のようにBRAMは1クロック遅れで出力が出てくるので、そのままはいけません。もう一つ上のmProgMemも書き換えようとしていました。mFlashMemは組み合わせ回路なんですが、その出力をmProgMem内でラッチしていたので、ラッチを1レベル下に移してやろうと考えていました。ところが、mProgMemはcmdClrが1のときに強制的に0(NOP)を返すという仕様になっていて、BRAMと整合性がとれません。BRAMの出力を組み合わせ回路でcmdClrが1のときだけ0にしようとすると、組み合わせ回路ループができてしまい、うまく動きませんでした。cmdClrの正体を調べるために、さらに上のモジュールまで戻らないといけないっぽいです。

とりあえず次善の策として次のようなことを考えています。Qという名前のイネーブラを使えばメモリアクセスが1クロック遅れでも平気になりそうです。ただし、1クロック1命令でなく2クロック1命令で動かすことになります。

もうちょっといじくりまわしてみようと思います。

そもそも自信がありません。

自サイトでも書きましたが、

どうもピン割り付けがうまくないのかなとも。

ぼのぐらしさんのところにコメントしておきました。UCFは以下のように書きました。ご参考まで。

NET "clk" LOC = "P88" | IOSTANDARD = LVCMOS33;

NET "rst_x" LOC = "P89" | IOSTANDARD = LVCMOS33;

#NET "led" LOC = "P98" | IOSTANDARD = LVCMOS33;

NET "led[3]" LOC = "P41" | IOSTANDARD = LVCMOS33; # B15

NET "led[2]" LOC = "P47" | IOSTANDARD = LVCMOS33; # A16

NET "led[1]" LOC = "P48" | IOSTANDARD = LVCMOS33; # B16

NET "led[0]" LOC = "P49" | IOSTANDARD = LVCMOS33; # A17