Latticeのダウンロードケーブル作成?の続きになります。

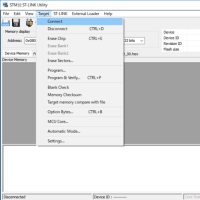

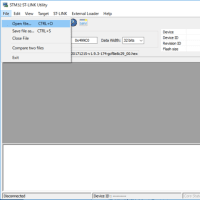

Latticeの書き込みツールispVM Systemでも動作することを確認しました。最初、ドライバがはいっていなかったらしく、変なエラーが出ていましたが、メニューのispTools → Install/Uninstall LSC USB/Parallel Port Driverを選んでインストールしなおしたところ、うまく動くようになりました。

これで、ispLEVERを使って*.jedファイルを作って、ispVMでFPGAに書き込むことができるようになりました。

昨日作った回路の回路図です(クリックすると拡大します)。

部品は、100Ω抵抗×8、10kΩ×3、0.1uF積層セラミックコンデンサ、74LCX244です。後は変換基板やコネクタ類です。

74LCX244の入力側を、一応プルアップしたつもりですが、3.3Vでいいんでしょうか?5Vが電源に流れ込んじゃう?このあたりがよく分かってないところが一番の弱点です。

ちなみに、ほとんど同じ回路でザイリンクスのダウンロードケーブルも作れちゃいます。スイッチで切りかえれるようにするのもありです。

ザイリンクスのケーブルのときの接続

・パラレルポートの13ピン <---> 74LCX244の9ピン(2Y1)

・パラレルポートの8ピン-11ピン-12ピンを接続

Latticeのケーブルのときの接続

・パラレルポートの10ピン <---> 74LCX244の9ピン(2Y1)

・パラレルポートの8ピン-12ピン-13ピンを接続

ブレッドボードでスカスカに作って動くくらいなので、かなり動作は安定していると思います。

電源はケーブル側から供給していますが、FPGAボード側からもらってもいいです。

DD誌の回路図との違いです。

・ispEN、RESET、JTAGという3本の線を省略しています。

・DD誌の回路図では、74LCX244でなく74VHC244になっています。

・DD誌の回路図では、入力側のダンピング抵抗がありません。

・DD誌の回路図では、出力側はローパスフィルターになっています。

・DD誌の回路図では、パラレルポートの15ピンにVccをつなげています。

・DD誌の回路図では、TDOもプルアップしています。

DD誌の回路図は雰囲気的にSPI接続のフラッシュROMにも書き込める回路になっているように思えます。

74LCX244は8個もバッファがついているのに4個しか使っていません。74LCX125とかでもよさそうです。

Latticeの書き込みツールispVM Systemでも動作することを確認しました。最初、ドライバがはいっていなかったらしく、変なエラーが出ていましたが、メニューのispTools → Install/Uninstall LSC USB/Parallel Port Driverを選んでインストールしなおしたところ、うまく動くようになりました。

これで、ispLEVERを使って*.jedファイルを作って、ispVMでFPGAに書き込むことができるようになりました。

昨日作った回路の回路図です(クリックすると拡大します)。

部品は、100Ω抵抗×8、10kΩ×3、0.1uF積層セラミックコンデンサ、74LCX244です。後は変換基板やコネクタ類です。

74LCX244の入力側を、一応プルアップしたつもりですが、3.3Vでいいんでしょうか?5Vが電源に流れ込んじゃう?このあたりがよく分かってないところが一番の弱点です。

ちなみに、ほとんど同じ回路でザイリンクスのダウンロードケーブルも作れちゃいます。スイッチで切りかえれるようにするのもありです。

ザイリンクスのケーブルのときの接続

・パラレルポートの13ピン <---> 74LCX244の9ピン(2Y1)

・パラレルポートの8ピン-11ピン-12ピンを接続

Latticeのケーブルのときの接続

・パラレルポートの10ピン <---> 74LCX244の9ピン(2Y1)

・パラレルポートの8ピン-12ピン-13ピンを接続

ブレッドボードでスカスカに作って動くくらいなので、かなり動作は安定していると思います。

電源はケーブル側から供給していますが、FPGAボード側からもらってもいいです。

DD誌の回路図との違いです。

・ispEN、RESET、JTAGという3本の線を省略しています。

・DD誌の回路図では、74LCX244でなく74VHC244になっています。

・DD誌の回路図では、入力側のダンピング抵抗がありません。

・DD誌の回路図では、出力側はローパスフィルターになっています。

・DD誌の回路図では、パラレルポートの15ピンにVccをつなげています。

・DD誌の回路図では、TDOもプルアップしています。

DD誌の回路図は雰囲気的にSPI接続のフラッシュROMにも書き込める回路になっているように思えます。

74LCX244は8個もバッファがついているのに4個しか使っていません。74LCX125とかでもよさそうです。

一番危ないのは5Vインターフェースに直接つながるLCX244の2Y1出力かな?

私もPCの5V出力系、3.3V出力系両対応にするため自作したケーブルはLCX244に交換しています。それに伴いステータスを決める論理回路部もトレラントC-MOSにしてます。

最初に3.3V出力系のPCに接続していた時のことですが、実はベースボードを自作した関係で誤ってCN2-B09をグランドに落としてしまい(付録基板のシルク印刷に注意必要です。惑わされました。)、VHC244を絶対定格出力電流オーバーで破損させました。LCX244なら万一ピン接続を間違えて例えばTCKをグランドに接続してしまっても絶対定格が高めなのでダンピング抵抗が保護抵抗になって壊れません。これもトレラント同様にメリットに感じます。

これらは3.3Vで動作させているので、両対応にあたり私もPC側のプルアップをどうするか悩みました。結局パソコンの出力に合わせ5Vと3.3Vをジャンパーで変更できるようにしましたが、5V系PC接続で3.3V固定でもいまのところ問題になっていません。また、プルアップをディスエーブルにしても、プルダウンにしてもどちらでも問題になっていません。

困っていたのが15ピンのVccセンスですが、Simさんのを拝見しますとつなげなくても動くのですね!

自分は直結するのがPC側を壊さないか怖かったので、ザイリンクスのダウンロードケーブル回路を参考にダイオードを入れました。それで良かったのかどうかVccセンスの意味がわからないので不明です。

パワーは元ICが供給して、信号を制限するタイプのようです。

http://www.semicon.toshiba.co.jp/product/logic/selection/topics/1182955_1100.html

私も5Vだと思っていたので、レベル変換の石をはさみました。ぐぐっても何Vなのかよく分かりませんでした。

はい、データシートにはLCX244は入力、出力どちらも5Vトレラントと書かれています。

とりあえず、電圧とか測ってみようと思います。

minminさんも自作されたんですね。

webで見つかるザイリンクスのケーブルとかでも、プルアップがあったりなかったりと、まちまちですが、latticeでも似たような状況なんですね。情報ありがとうございます。

15pinはソフトでチェックしてたら必要なので、ソフトが動かなかったら後で追加しようと思っていました。なくても動いているみたいです。トラ技2008年1月号の付録に載っている回路図を見るとダイオードと抵抗を介して3.3Vにつながっていますね。

私のは、かなり省略しちゃったので、たまたま動いているだけかもしれません。

ご紹介のページは2電源タイプのレベルシフタみたいですね。LCX244は1電源タイプですが、これも似たような構造になってるんでしょうか。

もう一つ並んでいたのは、15ピンのアンフェノールコネクタ。こいつは、PC-9801に使われていた勝手規格でしたよね。

DSUB-25Pになったのは、PC/AT時代からだから、もっと新しい資料を探さなくっちゃ。

(レベルは2つの電源でコントロールされる)

受け側から見るとオープンコレクタで

抵抗ターミネイト、

スイングは受け側のフルスイングになる、

必殺技です。

1個遊んだ回路でゲートバイアス、ディレクションコントロール、エネーブルをやっているようです。

入力レベルやプロテクションDiがVCCに繋がっているか等だけです。

ゲート接地風はそれ自体はドライブせず(FETSWはドレン、ソースが区別無く双方向です)

速度にも関係しませんが、元側の駆動能力に頼ります。

両右方が同時にドライブすると・・だからオープンドレン。

ドライブ電流が増えないのが少し不安ですが、そんなもんかも・・

此方は8ビット、ディレコントロールはありませんでした。

レベルシフタとは少し違うようです。