今月号の特集は「作りながら学ぶマイクロコンピュータ」ということで、ALTERAのCPLD上でPIC12F508を実現してしまうという企画です。xilinx派の私としては、ALTERAには手を出さんとか思っていたのですが、おもしろそうなので、ついついボードを買ってしまいました(共同購入の世話役をされたhamayanさん、ありがとうございます)。とか言いつつ、以前1chip MSXを買っていたので2台目です。

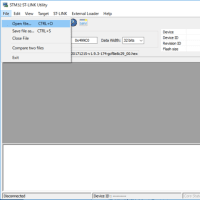

運の悪いことに、ちょうどALTERAが論理合成ツールQuartusのバージョンをあげたばかりなので、誌面で説明しているのと多少食い違いができています。新しい8.1では、8.0以前に必要だったライセンスファイルが不要になっています。

RTLはトラ技のページからダウンロードできます。プロジェクトごと入っているので、適当なフォルダーにコピーするだけで合成したり、ダウンロードしたりできます。まだ全部試したわけじゃないですが、モノによって7.0のプロジェクトだったり、8.0のプロジェクトだったりとバージョンの違うプロジェクトが混ざっています。7.0のものは互換性がないらしく、変換するというダイアログがでます。

Releaseというフォルダーにはいっているプロジェクトは7.0のものです。508Emu.map.summaryというファイルを覗いてみるとLEの数は1023になっています。8.1で論理合成しなおすと1070と47LEだけ増えています。

いつものVeritakでシミュレーションしてみました。ModelSimというフォルダーにはいっているのが、シミュレーション用で、MAXII固有の機能を使っていません。テストベンチもはいっています(tb_M508Emu.v)。

一箇所だけエラーが出ました。508Emu.vの47行の

mTimer0 tmr0(reset,fosc,Q,opt[3:0],wr_tmr,db_out,tim_out);

です。ポート数が一致しませんというエラーです。一つ足りないみたいなので、最後に「,」をつけてエラーを取りました。

mTimer0 tmr0(reset,fosc,Q,opt[3:0],wr_tmr,db_out,tim_out,);

修正後はtim_outの後に「,」がついています。出力ポートに何も書かないと単に出力先がなくなるだけです。ModelSimではエラーにならないのでしょうか?

きれいに1クロック1命令になっていて清清しいです。

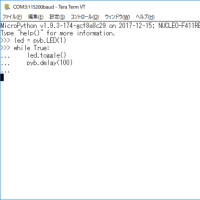

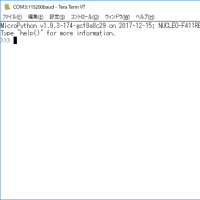

とりあえず書いてみたLEDチカチカです(<が全角になってます)。

Quartusって、`defaultnettypeが書けないのでしょうか。エラーが出ます。

11/28追記 エラーが出て当たり前です。正しくは`default_nettypeです。間に「_」が入ります。

やってみたいのは、Xilinx系への移植です。といってもVeritakでシミュレーションできたから、余裕でできそうです。

やっぱり、Verilog好きです。

来月号の特集は「ディジ/アナ混載IC活用研究」というタイトルで、PSoCの特集です。

500kHzサンプリングUSBオシロスコープの製作というのもおもしろそうです。最大8個のAVRを2μsずつずらして動作させる、と書いてあります。

って、CPLDの記事以外、全然見てません。

- PSpice活用ワンランク・アップ!が最終回です。

- 後閑さんのMP3プレーヤ作成記事が出てます。VS1011eを使っています。

昨日、トラ技を買ってきたのに、遊ぶのに手一杯で、書くのは今日になってしまいまた。

運の悪いことに、ちょうどALTERAが論理合成ツールQuartusのバージョンをあげたばかりなので、誌面で説明しているのと多少食い違いができています。新しい8.1では、8.0以前に必要だったライセンスファイルが不要になっています。

RTLはトラ技のページからダウンロードできます。プロジェクトごと入っているので、適当なフォルダーにコピーするだけで合成したり、ダウンロードしたりできます。まだ全部試したわけじゃないですが、モノによって7.0のプロジェクトだったり、8.0のプロジェクトだったりとバージョンの違うプロジェクトが混ざっています。7.0のものは互換性がないらしく、変換するというダイアログがでます。

Releaseというフォルダーにはいっているプロジェクトは7.0のものです。508Emu.map.summaryというファイルを覗いてみるとLEの数は1023になっています。8.1で論理合成しなおすと1070と47LEだけ増えています。

いつものVeritakでシミュレーションしてみました。ModelSimというフォルダーにはいっているのが、シミュレーション用で、MAXII固有の機能を使っていません。テストベンチもはいっています(tb_M508Emu.v)。

一箇所だけエラーが出ました。508Emu.vの47行の

mTimer0 tmr0(reset,fosc,Q,opt[3:0],wr_tmr,db_out,tim_out);

です。ポート数が一致しませんというエラーです。一つ足りないみたいなので、最後に「,」をつけてエラーを取りました。

mTimer0 tmr0(reset,fosc,Q,opt[3:0],wr_tmr,db_out,tim_out,);

修正後はtim_outの後に「,」がついています。出力ポートに何も書かないと単に出力先がなくなるだけです。ModelSimではエラーにならないのでしょうか?

きれいに1クロック1命令になっていて清清しいです。

とりあえず書いてみたLEDチカチカです(<が全角になってます)。

//`defaultnettype none

module main(

output reg [7:0] led = 8'h00,

input clk);

reg [20:0] ctr = 0;

wire ctr_en = ctr == 0;

always @(posedge clk)

ctr <= ctr + 21'h1;

always @(posedge clk)

if(ctr_en) led <= led + 8'h1;

endmodule

Quartusって、`defaultnettypeが書けないのでしょうか。エラーが出ます。

11/28追記 エラーが出て当たり前です。正しくは`default_nettypeです。間に「_」が入ります。

やってみたいのは、Xilinx系への移植です。といってもVeritakでシミュレーションできたから、余裕でできそうです。

やっぱり、Verilog好きです。

来月号の特集は「ディジ/アナ混載IC活用研究」というタイトルで、PSoCの特集です。

500kHzサンプリングUSBオシロスコープの製作というのもおもしろそうです。最大8個のAVRを2μsずつずらして動作させる、と書いてあります。

って、CPLDの記事以外、全然見てません。

- PSpice活用ワンランク・アップ!が最終回です。

- 後閑さんのMP3プレーヤ作成記事が出てます。VS1011eを使っています。

昨日、トラ技を買ってきたのに、遊ぶのに手一杯で、書くのは今日になってしまいまた。

私の知っている文法とずいぶん違っているようです。

定期購読のトラ技は、諸般の事情から封印したままなので、まずは読んでみなきゃ。

あれは、ALTERA+VHDLだったのですが、

えらく印象が違いますね。

というほど勉強してませんが。

自分のブログにも書きましたが、

トラ技をパラパラ見ただけで、めげてしまいました。

xilinx基板の後遺症もあるかも。

すいすいこなしてしまう人を見るとうらやましい。

もちろん、今までの蓄積があるのでしょうが。

Verilogを勉強しようか、VHDLにしようか、はてまた過去の遺物のAHDLにしようか悩んで触ってもいません。

見習わなければ。

しばらく読んでいると、目がとても疲れるのでどしてだろうと思ったら、フォントの色がグレーなんですね。

黒にしていただけると、とてもありがたいのですが....。

トラ技の方はverilogで書かれています。私のは、一部verilog 2001がまざってます。ANSI C風の宣言はverilog 2001から使えるようになりました。それ以前のだと

module main(led, clk);

output [7:0] led;

input clk;

reg [7:0] led;

wire clk;

みたいな書き方でした。

verilogは、一見Cに似ています。VHDLのソースは英字が多い感じですが、verilogのソースはスカスカです。

私は電子工作暦よりverilog暦の方が長いです。たぶん6~7年くらい前からです。電子工作はもうそろそろ2年になるくらいです。トラ技2007年1月号の付録基板用のボードをhamayanさんから購入したのが電子工作をはじめたきっかけでした。

長くやってれば私でも身についたので、辛抱ですね。

おかげさまで、楽しませていただいております。

これから状況は変わるかもしれませんが、VerilogはSystem Verilogという後継にも恵まれて先行き明るいという感じです。VHDLの方はSystem Verilogの機能を取り込んで新たなISOを作ろうとしているそうです。今の所、VHDLの革新が立ち遅れている感じです。

個人的にはverilogの方が好きです。VHDLは、いっぱいソースを書かないといけないという程度の理由です。generateとかVHDLにしかなかったものも、どんどんverilogに取り入れられはじめています。シミュレータや論理合成ツールも両方受け付けたり、一部verilog、一部VHDLなんてのもありみたいです。その意味では、どちらでも大差はなくて、やってみて気に入った方にしても、そんなに困りません。

verilogを使っているもう一つの理由は、veritak winという優れたシミュレータが安価で手に入るからです。

そうなんです。お恥ずかしい話なんですが、よく分からないので最初の設定のままなんです。もし、お分かりになるようならやり方を教えていただけませんか?

編集のメニューにはデザインメニューというのがあって、テンプレートの選択とテンプレートの編集というのが選べます。編集の方を選ぶと編集できませんというメッセージが出ます。選択の方はお正月テンプレートとか、そういうのが選べるみたいです。文字の色を変えたりするのはどうすればいいんでしょうね><

Sim さんの BLOG の場合には、ユーザ共通と思われる CSS ファイル http://blog.goo.ne.jp/tpl_master/css/cd0210a890c224f9f3048b89e6838d4b.css が使われています。

これは、すべてのユーザに共通なテンプレートなので、編集は出来ないと思われます。そのため、このテンプレートを自分用にコピーしてから書き換えるという手順になると思います。具体的には… goo を使ったことが無いので私にはわかりません。

書き換えるべき箇所は、すでに確認しましたので、まずは自分用のテンプレートを作る所からはじめましょう。

gooはカスタマイズできるテンプレートとそうでないのがあるみたいです。シンプルというのとカスタムというのがカスタマイズできるそうです。

CSSというのは、はじめて見ました。テンプレートによっては、右側が切れるのもあったりします。

カスタムに変更して、教えてもらったリンク先のをコピペしてみたんですが、ぐちゃぐちゃになりました。カスタムのうち、今までのに一番似ているのにしてみます。よろしければ変更箇所を教えていただけないでしょうか?