公式サイトにmbedの動作クロックが書いてないような気がするので調べてみました。

mbedはNXPのLPC1768というARM Cortex-M3をCPUとして使っています(NXPのユーザーズマニュアル pdf)。

mbedの回路図(pdf)を見ると12MHzがX1に入力されています。この12MHzをPLLで逓倍してメインクロックとして使っています。

ユーザーズマニュアル(以下umと略記)のp.37にPLLの出力周波数の式が書いてあります。

(1) Fcco = (2×M×Fin)/N

FccoはPLLの出力周波数

MはPLL0CFGのMSEL0フィールド+1

NはPLL0CFGのNSEL0フィールド+1

FinはPLLCLKINの周波数(um p.27によると12MHz)

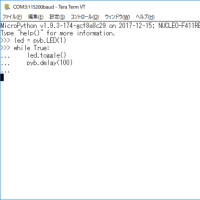

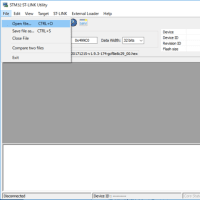

MとNを知るためにはPLL0CFGレジスタの内容を読まないといけません。umのp.32によると番地は0x400fc08cです。下位15ビットがMSEL0でビット23-16の8ビットがNSEL0です。以下のコードを使ってPLL0CFGを読み出しました。

読み出した結果は

0000000b

なのでMSEL0 = 0x000b、NSEL0 = 0x00です。つまりM=12、N=1です。上の式に代入してみると288MHz(= 2 * 12 * 12MHz / 1)がPLL0の出力周波数になります。

CPUの動作クロックはCCLKという名前です。um p.50の図10を見るとPLL0の周波数をCPU Clock Dividerで分周してcclkを作っています。分周のパラメータはCCLKCFGというレジスタで設定するようです。

um p.51にCCLKCFGの設定が載っています。アドレスは0x400fc104で下位8ビットのCCLKSELに1を足した値で分周するようです。つまり

(2) cclk = Fcco / (CCLKSEL + 1)

です。CCLKCFGを読み出してみると

00000002

でした。つまり3分周していることになります。上で求めたFccoの288MHzを(2)式に代入するとcclkは96MHz(= 288MHz / 3)ということになります。

一応、100MHzまで動作することのできるCPUですが、外部クロックが12MHzなので、可能な最高速である96MHzで動作しています。

外部クロックが12MHzなのはUSBの関係だと思います。

mbedはNXPのLPC1768というARM Cortex-M3をCPUとして使っています(NXPのユーザーズマニュアル pdf)。

mbedの回路図(pdf)を見ると12MHzがX1に入力されています。この12MHzをPLLで逓倍してメインクロックとして使っています。

ユーザーズマニュアル(以下umと略記)のp.37にPLLの出力周波数の式が書いてあります。

(1) Fcco = (2×M×Fin)/N

FccoはPLLの出力周波数

MはPLL0CFGのMSEL0フィールド+1

NはPLL0CFGのNSEL0フィールド+1

FinはPLLCLKINの周波数(um p.27によると12MHz)

MとNを知るためにはPLL0CFGレジスタの内容を読まないといけません。umのp.32によると番地は0x400fc08cです。下位15ビットがMSEL0でビット23-16の8ビットがNSEL0です。以下のコードを使ってPLL0CFGを読み出しました。

int main(){

printf("%08x", *(unsigned *)0x400fc08c);

}

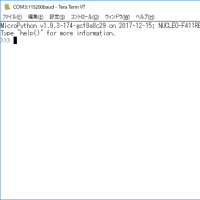

読み出した結果は

0000000b

なのでMSEL0 = 0x000b、NSEL0 = 0x00です。つまりM=12、N=1です。上の式に代入してみると288MHz(= 2 * 12 * 12MHz / 1)がPLL0の出力周波数になります。

CPUの動作クロックはCCLKという名前です。um p.50の図10を見るとPLL0の周波数をCPU Clock Dividerで分周してcclkを作っています。分周のパラメータはCCLKCFGというレジスタで設定するようです。

um p.51にCCLKCFGの設定が載っています。アドレスは0x400fc104で下位8ビットのCCLKSELに1を足した値で分周するようです。つまり

(2) cclk = Fcco / (CCLKSEL + 1)

です。CCLKCFGを読み出してみると

00000002

でした。つまり3分周していることになります。上で求めたFccoの288MHzを(2)式に代入するとcclkは96MHz(= 288MHz / 3)ということになります。

一応、100MHzまで動作することのできるCPUですが、外部クロックが12MHzなので、可能な最高速である96MHzで動作しています。

外部クロックが12MHzなのはUSBの関係だと思います。

※コメント投稿者のブログIDはブログ作成者のみに通知されます