メリークリスマス!

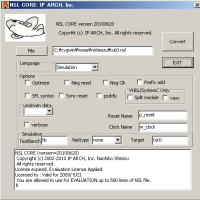

ということで、クリスマスバージョンのsfl2vlとともに、NSLによる除算回路のサンプルをお届けします。

Nは割られる数のビット数、Mは割る数のビット数を定義し、出力は、N-Mビットになります。

見れば見るほど平方根回路にそっくり、というか、平方根回路を少し変更しただけで作成しました。。この回路は乗算のコストが安いFPGA向けです。ASICで使う場合には、通常の引き戻し法か引き離し法などを使ってください。

ということで、クリスマスバージョンのsfl2vlとともに、NSLによる除算回路のサンプルをお届けします。

Nは割られる数のビット数、Mは割る数のビット数を定義し、出力は、N-Mビットになります。

見れば見るほど平方根回路にそっくり、というか、平方根回路を少し変更しただけで作成しました。。この回路は乗算のコストが安いFPGA向けです。ASICで使う場合には、通常の引き戻し法か引き離し法などを使ってください。

#define N 8

#define M 4

declare div_%N%_%M% {

input A[N],B[M];

output F[N-M];

func_in div_do(A,B);

func_out div_done(F);

}

module div_%N%_%M% {

reg try[N-M];

wire mul_i1[N-M], mul_i2[M], mul_o[N];

func_self mul(mul_i1,mul_i2);

func mul {

mul_o = mul_i1*mul_i2;

}

func div_do seq {

reg bitpos[N-M];

for( {bitpos:=1 << ((N-M)-1); try:=0; } ; bitpos != 0 ; bitpos := bitpos >> 1) {

if(mul(try | bitpos,B).mul_o <= A) try := try | bitpos;

}

div_done(try);

}

}