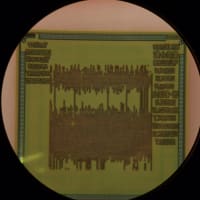

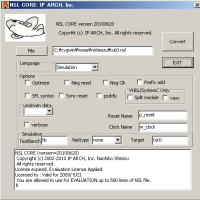

NSLで論理を作成し、AllianceVHDLでレイアウトをしたチップが上ってきた。

1.2um 2層メタルのミニチップだけれど、デザインフローの確認には充分。

ただ、2層メタルなので、クロックツリーの作成など、次のステップとなる部分は確認できず、以降の試作で確認予定。

80ピンQFPのパッケージ品で動作確認する必要があるので、確認回路の設計をしないといけないですね。

ベアチップに顕微鏡でピンを立てて、動作確認する方が、私好みなのだけれど、「できる気がしない」などと言う奴に、やる気を出させるアイデアはないですか?

1.2um 2層メタルのミニチップだけれど、デザインフローの確認には充分。

ただ、2層メタルなので、クロックツリーの作成など、次のステップとなる部分は確認できず、以降の試作で確認予定。

80ピンQFPのパッケージ品で動作確認する必要があるので、確認回路の設計をしないといけないですね。

ベアチップに顕微鏡でピンを立てて、動作確認する方が、私好みなのだけれど、「できる気がしない」などと言う奴に、やる気を出させるアイデアはないですか?

個人で半導体を作れるんですか

個人でもMOSISなどを通せば作れますが、金額的に結構厳しいと思います。