sfl2vlでのメモリ初期化の方法を検討中。

VerilogHDLでよくある例題だと、単純にメモリをモデル化して、

そのアドレスをデコードしてROM内容を出力するが、

メモリの内容を初期化したいのであって、ROMをモデル化したいのではない場合、

あまりよい例題が見つからない。

実際に合成系に通るかわからないけれど、やりたいことは。例えば

mem ram[16]<8> = { 0x01, 0x02, 0x03, 0x04};

を

always

begin

ram[0] <= 0x01;

ram[1] <= 0x02;

ram[2] <= 0x03;

ram[3] <= 0x04;

end

に変換するようなことである。

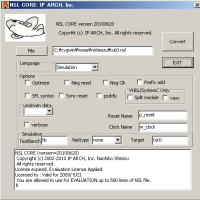

β版として、この変換をサポートするものを

http://www.ip-arch.jp/binaries/sfl2vlwin-20090525.zip

として、作ってみた。(サイトからリンクしていない)

使い勝手について、ご意見があれば、教えてほしい。(メールでもコメントでも)

VerilogHDLでよくある例題だと、単純にメモリをモデル化して、

そのアドレスをデコードしてROM内容を出力するが、

メモリの内容を初期化したいのであって、ROMをモデル化したいのではない場合、

あまりよい例題が見つからない。

実際に合成系に通るかわからないけれど、やりたいことは。例えば

mem ram[16]<8> = { 0x01, 0x02, 0x03, 0x04};

を

always

begin

ram[0] <= 0x01;

ram[1] <= 0x02;

ram[2] <= 0x03;

ram[3] <= 0x04;

end

に変換するようなことである。

β版として、この変換をサポートするものを

http://www.ip-arch.jp/binaries/sfl2vlwin-20090525.zip

として、作ってみた。(サイトからリンクしていない)

使い勝手について、ご意見があれば、教えてほしい。(メールでもコメントでも)