熱酸化プロセス

デバイスを作る際にはSiだけでなく多くの膜を使用する。その中でも重要なのが酸化することによって得られる絶縁膜である。酸化膜:SiO2はさまざまな手段によって作られるがもっとも簡単で良質な膜が得られるのは熱酸化膜であり、信頼性の要求されるゲート絶縁膜等に使用されている。

熱酸化に用いられる装置を下に示す。酸化の温度は一般的に900~1200℃でガス流速は1L/minである。

酸化のプロセスは

Si+O2→SiO2

Si+2H2→SiO2+2H2 と記述される。

Siの分子量28.09g/mol、密度2.33g/cm3

SiO2の分子量60.08g/mol、密度2.21g/cm3とすると

1モル分のSiおよびSiO2の体積は分子量/密度であり

1モルのSiが1モルのSiO2になるので

Siの厚さ/SiO2の厚さ=Si1モルの体積/SiO21モルの体積となって

Siの厚さ/SiO2の厚さ=0.44 つまり厚さxの酸化膜を作ると0.44xのSiが消費される。

Si/SiO2の界面は下図のようにSi中に移動する。これは表面の汚染がそのまま酸化膜表面に残って新しい界面が作られるということである。

熱酸化で作られたSiO2はアモルファス構造をしていて密度は2.21g/cm3である。

Siの熱酸化の機構は下図のような簡単なモデルで考えることが出来る。

時間tが小さな場合、酸化膜の厚さxは

x≒C0×κ/C1(t+τ)

時間tが大きな場合、酸化膜の厚さxは

x≒√[2×C0×D/C1(t+τ)]

Cは酸化膜中の単位体積あたりの酸化物質の分子数

Dは酸化物質の拡散係数

κは表面反応速度係数

τは初期状態を説明するための時間軸のずれである。

これから初期の酸化は表面反応が反応律速になって時間に対して直線的に変化するが酸化膜が厚くなると酸化物質は酸化膜を通して拡散するために拡散律速になり時間に対して1/2上に比例するようになる。

乾燥雰囲気中で成長された酸化膜は良性の特性を有しているが成長速度は非常に遅い。膜の特性よりも成長速度が優先される場合には水蒸気雰囲気での酸化が行われる。(成長速度は乾燥酸化の5から10倍ほどある) 下図は異なる面方位に対して酸化膜圧の反応時間、温度依存性を実験したものである。

正確に薄い酸化膜を制御して堆積させるためには工夫が必要で比較的低い800から900℃での成膜、他のガスを混ぜて酸素の分圧を下げる、O2以外の酸化剤を添加するCVD膜を組み合わせるなどの手法がある。

CVDによるSiO2膜の堆積

CVDで生成された膜は熱酸化膜に対して質は劣るものの配線の絶縁膜、STIにおける素子分離等に使用されている。PをドープしたSiO2膜は金属膜の絶縁、デバイスの保護膜に用いられる。PやAsをドープした膜は拡散源としても用いられる。

低温(300から500℃)においてはシランを用いるプロセスが一般的である。Pを含んだプロセスは

SiH4→SiO2+2H2

4PH3+5O2→2P2O5+6H2 共に450℃

配線上に絶縁膜を作るのに適したプロセスである。常圧もしくはLPCVDでの減圧プロセスである。

中程度の温度(500℃~800℃)ではLPCVD装置においてTEOSと呼ばれるテトラエチルオルソシリケイトSi(OC2H5)4を分解して行うことが出来る。

Si(OC2H5)4→SiO2+副生成物

有機物とSiの有機化合物が副生成物である。反応が高温なので金属膜状には使えないがPolySiゲート上でよく用いられる。温度が高いために段差被覆性が高いことが特徴である。

温度の関数としての堆積速度はe^(-Ea/kT)とあらわされる。Eaは活性化エネルギーでありTEOSの活性化エネルギーは非常に高い(シラン0.6eVに対しTEOS1.4eV)。

堆積速度のTEOSの膜厚依存性に関しては1-e^(-P/P0)に比例する。P0は30Pa PはTEOS分圧である。分圧が低い場合は表面反応速度によって律速し、高い場合には表面で飽和するので分圧に依存しなくなる。

高温900℃ではジクロロシランが用いられる

SiCl2H2+2N2O→SiO2+2N2+2HCl

高温で段差に対する被覆性がいい事からPoly-Si上の堆積に多く用いられる。

堆積法と膜の性質が下表にまとめてある。

酸化膜の導電機構と欠陥

酸化膜は基本的にはバンドギャップが大きいために絶縁体であるが高電界を印加することによって電気を流すことが出来る。 酸化膜の導電機構としてはFowler-Nordheimトンネル電流と直接トンネル電流に分けられる。

Fowler-Nordheimトンネル電流と酸化膜に大きな電界(5MV/cm以上)がかかった時にシリコンの伝導帯から酸化膜の伝導体に電子がトンネルする現象であり以下の式で表される。

J=(Eox^2q^2m)/(8πhΦm*)exp[(-8π(2m*)^1/2×(qΦ)^3/2)/3qhEox]

Eox:酸化膜中の電界

q:電荷

h:プランク定数

Φ:バリアハイト

m:真空中の電子有効質量

m*:酸化膜中の電子有効質量

酸化膜自体が薄い場合(数nm以下)はデバイス編 キャリアの輸送現象でも記した直接トンネル現象が起こる。

式の形からlog(J/Eox^2)は(1/Eox)に比例するので実測のプロットが直線に乗っていればFowler-Nordheimトンネル電流可動化の判断が出来る。

Fowler-Nordheimトンネル電流では電子だけでなく正孔も注入されるが電子に比べてバリアハイトが高いことから(電子3.06eV、正孔:4.06eV)電流の値は数桁小さくなり電子電流が支配的であると考えてよい。

Fowler-Nordheimトンネル電流はフラッシュメモリの書き込み、消去の際に持ちられている。

酸化膜中にトラップされた電荷は酸化膜のブレークダウンをもたらすので信頼性にとって重要である。

①Fixed Oxide Charge:固定電荷

Si/SiO2界面から2nmに存在する構造欠陥に起因する正電荷で、Si基板の面方位、酸化プロセスに敏感。Siとの電荷のやり取りはしない

②Mobile Ionic Charge

プロセス中に入り込んだナトリウム、アルカリイオン起因。高電圧化でのデバイス動作に影響

③Interface Trapped Charge:界面捕捉電荷

構造欠陥、照射、金属不純物により切断された結合による電荷。表面準位、界面準位とも言われる。正負両方ともありSi基板と電荷のやり取りを行う。

④Oxide Trapped Charge

酸化膜中の欠陥に起因したものでプロセスでのダメージで生じるアニールによって低減が可能。

酸化膜の評価

絶縁破壊電圧

酸化膜の評価の基本は絶縁破壊電圧でありMOSキャパシタを用いて行われる。

1MV/cm以下の破壊はピンホール等のAモード不良

1MV/cmから8MV/cmはウイークスポットによるBモード不良

8MV/cm以上はCモードという

Bモードは電圧印加で瞬時に破壊して再度の測定ではAモードになる。

Cモードは前述のFowler-Nordheimトンネル電流であり必ずしも破壊ではない。

経時絶縁破壊(Time-Dependent Dielectric Breakdown:TDDB)は電界または電流ストレスを印加後ある時間経過してから絶縁破壊する現象である。

電流を一定にするか電圧を一定にするかで定電流、もしくは定電圧ストレス印加法と呼ばれる。TDDBは高電界高温度により加速することが知られており

次式の関係が一般的に知られている。

Δt(P)=A・10^(-βΔE)exp[Ea/k(1/T)]

Δt(P)はストレス電界を印加する事によって不良率がPパーセントにいたる短縮時間、Aは定数、βは電界加速、ΔEはストレス電界と動作電界の差、Eaは活性化エネルギー、kはボルツマン定数、Δ(1/T)はストレス温度と動作温度の逆数との差である。破壊に至るまでの時間と電界をプロットしていくことにより電界加速項を求めることが出来、動作電解、動作速度下による長期寿命や故障率を予測できる。

窒化膜

Si3N4膜は水やNaの拡散を防ぐことが出来るのでデバイスの保護膜として用いられている。さらにはSiの選択酸化のマスクとしてやCMPの際の終端検知に用いられている。これは強固で引っ張り傷にも強いということがあげられる。

中程度の温度(750℃)でのLPCVDもしくは低温(300度)でのプラズマCVDによって生成される。密度はLPCVDで2.9~3.1g/cm3、P-CVDで2.4~2.8g/cm3である

LPCVDでは

3SiCl2H2+4NH3→Si3N4+6Hcl+6H2 750℃

膜質が均一で高いスループットが得られる成長の活性化エネルギーは1.8eV程度である。LPCVDによるSiNはアモルファスでありSiO2の10倍の引っかき応力を持つ。誘電率は6程度、絶縁強度は10MV/cmである。200nm以上の膜では内部応力でクラックの入る可能性がある。

プラズマCVDでは

SiH4+NH3→SiNH+3H2

2SiH4+N2→2SiNH+3H2

成長速度は温度、プラズマ生成電力、ガス圧に比例する。

PCVD膜には大量のHが含まれている。通常20から25原子%のHを含んでいる。

PCVD膜は引っ張り応力が弱く 絶縁強度は1から6MV/cm程度である。

ポリシリコン膜

MOSデバイスのゲート電極としてポリシリコンを用いるのが一般的である。それはAl電極に比べて信頼性が高いことが原因である。Alは酸化膜中に拡散してしまうために絶縁膜を破壊してしまう。

ポリシリコンは浅い接合を作るための拡散源としても用いられ結晶Siへのオーミック接触を実現する。

ポリシリコンの成長は600~650℃のLPCVD装置が使われ原料としてはシランが用いられる。

SiH4→Si+2H2 600度プロセス

上図は成長温度によるポリシリコンの成長速度を示したものである。

この領域では成長速度はexp(-Ea/kT)に従う。活性化エネルギーは1.7eVである。

600~650℃でのポリシリコンは円柱状であり110面に配向している。

600度以下の場合はアモルファスで製膜されるが熱処理を行うと多結晶粒状、柱状の成長が見られる。

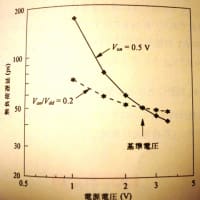

通常ポリシリコンはドーパントのガスを注入したり、イオン注入してn型、p型にドーピングして用いる。下図はPもしくはSbをイオン注入でドープしたSiのシート抵抗である。結晶粒界でのキャリアトラップのためSiの抵抗は低ドーズで非常に高くなるがキャリアトラップがドーパントで飽和すると単結晶の抵抗値に近づく。

デバイスを作る際にはSiだけでなく多くの膜を使用する。その中でも重要なのが酸化することによって得られる絶縁膜である。酸化膜:SiO2はさまざまな手段によって作られるがもっとも簡単で良質な膜が得られるのは熱酸化膜であり、信頼性の要求されるゲート絶縁膜等に使用されている。

熱酸化に用いられる装置を下に示す。酸化の温度は一般的に900~1200℃でガス流速は1L/minである。

酸化のプロセスは

Si+O2→SiO2

Si+2H2→SiO2+2H2 と記述される。

Siの分子量28.09g/mol、密度2.33g/cm3

SiO2の分子量60.08g/mol、密度2.21g/cm3とすると

1モル分のSiおよびSiO2の体積は分子量/密度であり

1モルのSiが1モルのSiO2になるので

Siの厚さ/SiO2の厚さ=Si1モルの体積/SiO21モルの体積となって

Siの厚さ/SiO2の厚さ=0.44 つまり厚さxの酸化膜を作ると0.44xのSiが消費される。

Si/SiO2の界面は下図のようにSi中に移動する。これは表面の汚染がそのまま酸化膜表面に残って新しい界面が作られるということである。

熱酸化で作られたSiO2はアモルファス構造をしていて密度は2.21g/cm3である。

Siの熱酸化の機構は下図のような簡単なモデルで考えることが出来る。

時間tが小さな場合、酸化膜の厚さxは

x≒C0×κ/C1(t+τ)

時間tが大きな場合、酸化膜の厚さxは

x≒√[2×C0×D/C1(t+τ)]

Cは酸化膜中の単位体積あたりの酸化物質の分子数

Dは酸化物質の拡散係数

κは表面反応速度係数

τは初期状態を説明するための時間軸のずれである。

これから初期の酸化は表面反応が反応律速になって時間に対して直線的に変化するが酸化膜が厚くなると酸化物質は酸化膜を通して拡散するために拡散律速になり時間に対して1/2上に比例するようになる。

乾燥雰囲気中で成長された酸化膜は良性の特性を有しているが成長速度は非常に遅い。膜の特性よりも成長速度が優先される場合には水蒸気雰囲気での酸化が行われる。(成長速度は乾燥酸化の5から10倍ほどある) 下図は異なる面方位に対して酸化膜圧の反応時間、温度依存性を実験したものである。

正確に薄い酸化膜を制御して堆積させるためには工夫が必要で比較的低い800から900℃での成膜、他のガスを混ぜて酸素の分圧を下げる、O2以外の酸化剤を添加するCVD膜を組み合わせるなどの手法がある。

CVDによるSiO2膜の堆積

CVDで生成された膜は熱酸化膜に対して質は劣るものの配線の絶縁膜、STIにおける素子分離等に使用されている。PをドープしたSiO2膜は金属膜の絶縁、デバイスの保護膜に用いられる。PやAsをドープした膜は拡散源としても用いられる。

低温(300から500℃)においてはシランを用いるプロセスが一般的である。Pを含んだプロセスは

SiH4→SiO2+2H2

4PH3+5O2→2P2O5+6H2 共に450℃

配線上に絶縁膜を作るのに適したプロセスである。常圧もしくはLPCVDでの減圧プロセスである。

中程度の温度(500℃~800℃)ではLPCVD装置においてTEOSと呼ばれるテトラエチルオルソシリケイトSi(OC2H5)4を分解して行うことが出来る。

Si(OC2H5)4→SiO2+副生成物

有機物とSiの有機化合物が副生成物である。反応が高温なので金属膜状には使えないがPolySiゲート上でよく用いられる。温度が高いために段差被覆性が高いことが特徴である。

温度の関数としての堆積速度はe^(-Ea/kT)とあらわされる。Eaは活性化エネルギーでありTEOSの活性化エネルギーは非常に高い(シラン0.6eVに対しTEOS1.4eV)。

堆積速度のTEOSの膜厚依存性に関しては1-e^(-P/P0)に比例する。P0は30Pa PはTEOS分圧である。分圧が低い場合は表面反応速度によって律速し、高い場合には表面で飽和するので分圧に依存しなくなる。

高温900℃ではジクロロシランが用いられる

SiCl2H2+2N2O→SiO2+2N2+2HCl

高温で段差に対する被覆性がいい事からPoly-Si上の堆積に多く用いられる。

堆積法と膜の性質が下表にまとめてある。

酸化膜の導電機構と欠陥

酸化膜は基本的にはバンドギャップが大きいために絶縁体であるが高電界を印加することによって電気を流すことが出来る。 酸化膜の導電機構としてはFowler-Nordheimトンネル電流と直接トンネル電流に分けられる。

Fowler-Nordheimトンネル電流と酸化膜に大きな電界(5MV/cm以上)がかかった時にシリコンの伝導帯から酸化膜の伝導体に電子がトンネルする現象であり以下の式で表される。

J=(Eox^2q^2m)/(8πhΦm*)exp[(-8π(2m*)^1/2×(qΦ)^3/2)/3qhEox]

Eox:酸化膜中の電界

q:電荷

h:プランク定数

Φ:バリアハイト

m:真空中の電子有効質量

m*:酸化膜中の電子有効質量

酸化膜自体が薄い場合(数nm以下)はデバイス編 キャリアの輸送現象でも記した直接トンネル現象が起こる。

式の形からlog(J/Eox^2)は(1/Eox)に比例するので実測のプロットが直線に乗っていればFowler-Nordheimトンネル電流可動化の判断が出来る。

Fowler-Nordheimトンネル電流では電子だけでなく正孔も注入されるが電子に比べてバリアハイトが高いことから(電子3.06eV、正孔:4.06eV)電流の値は数桁小さくなり電子電流が支配的であると考えてよい。

Fowler-Nordheimトンネル電流はフラッシュメモリの書き込み、消去の際に持ちられている。

酸化膜中にトラップされた電荷は酸化膜のブレークダウンをもたらすので信頼性にとって重要である。

①Fixed Oxide Charge:固定電荷

Si/SiO2界面から2nmに存在する構造欠陥に起因する正電荷で、Si基板の面方位、酸化プロセスに敏感。Siとの電荷のやり取りはしない

②Mobile Ionic Charge

プロセス中に入り込んだナトリウム、アルカリイオン起因。高電圧化でのデバイス動作に影響

③Interface Trapped Charge:界面捕捉電荷

構造欠陥、照射、金属不純物により切断された結合による電荷。表面準位、界面準位とも言われる。正負両方ともありSi基板と電荷のやり取りを行う。

④Oxide Trapped Charge

酸化膜中の欠陥に起因したものでプロセスでのダメージで生じるアニールによって低減が可能。

酸化膜の評価

絶縁破壊電圧

酸化膜の評価の基本は絶縁破壊電圧でありMOSキャパシタを用いて行われる。

1MV/cm以下の破壊はピンホール等のAモード不良

1MV/cmから8MV/cmはウイークスポットによるBモード不良

8MV/cm以上はCモードという

Bモードは電圧印加で瞬時に破壊して再度の測定ではAモードになる。

Cモードは前述のFowler-Nordheimトンネル電流であり必ずしも破壊ではない。

経時絶縁破壊(Time-Dependent Dielectric Breakdown:TDDB)は電界または電流ストレスを印加後ある時間経過してから絶縁破壊する現象である。

電流を一定にするか電圧を一定にするかで定電流、もしくは定電圧ストレス印加法と呼ばれる。TDDBは高電界高温度により加速することが知られており

次式の関係が一般的に知られている。

Δt(P)=A・10^(-βΔE)exp[Ea/k(1/T)]

Δt(P)はストレス電界を印加する事によって不良率がPパーセントにいたる短縮時間、Aは定数、βは電界加速、ΔEはストレス電界と動作電界の差、Eaは活性化エネルギー、kはボルツマン定数、Δ(1/T)はストレス温度と動作温度の逆数との差である。破壊に至るまでの時間と電界をプロットしていくことにより電界加速項を求めることが出来、動作電解、動作速度下による長期寿命や故障率を予測できる。

窒化膜

Si3N4膜は水やNaの拡散を防ぐことが出来るのでデバイスの保護膜として用いられている。さらにはSiの選択酸化のマスクとしてやCMPの際の終端検知に用いられている。これは強固で引っ張り傷にも強いということがあげられる。

中程度の温度(750℃)でのLPCVDもしくは低温(300度)でのプラズマCVDによって生成される。密度はLPCVDで2.9~3.1g/cm3、P-CVDで2.4~2.8g/cm3である

LPCVDでは

3SiCl2H2+4NH3→Si3N4+6Hcl+6H2 750℃

膜質が均一で高いスループットが得られる成長の活性化エネルギーは1.8eV程度である。LPCVDによるSiNはアモルファスでありSiO2の10倍の引っかき応力を持つ。誘電率は6程度、絶縁強度は10MV/cmである。200nm以上の膜では内部応力でクラックの入る可能性がある。

プラズマCVDでは

SiH4+NH3→SiNH+3H2

2SiH4+N2→2SiNH+3H2

成長速度は温度、プラズマ生成電力、ガス圧に比例する。

PCVD膜には大量のHが含まれている。通常20から25原子%のHを含んでいる。

PCVD膜は引っ張り応力が弱く 絶縁強度は1から6MV/cm程度である。

ポリシリコン膜

MOSデバイスのゲート電極としてポリシリコンを用いるのが一般的である。それはAl電極に比べて信頼性が高いことが原因である。Alは酸化膜中に拡散してしまうために絶縁膜を破壊してしまう。

ポリシリコンは浅い接合を作るための拡散源としても用いられ結晶Siへのオーミック接触を実現する。

ポリシリコンの成長は600~650℃のLPCVD装置が使われ原料としてはシランが用いられる。

SiH4→Si+2H2 600度プロセス

上図は成長温度によるポリシリコンの成長速度を示したものである。

この領域では成長速度はexp(-Ea/kT)に従う。活性化エネルギーは1.7eVである。

600~650℃でのポリシリコンは円柱状であり110面に配向している。

600度以下の場合はアモルファスで製膜されるが熱処理を行うと多結晶粒状、柱状の成長が見られる。

通常ポリシリコンはドーパントのガスを注入したり、イオン注入してn型、p型にドーピングして用いる。下図はPもしくはSbをイオン注入でドープしたSiのシート抵抗である。結晶粒界でのキャリアトラップのためSiの抵抗は低ドーズで非常に高くなるがキャリアトラップがドーパントで飽和すると単結晶の抵抗値に近づく。