はじめに

SOI(Silicon-On-Insulator)を用いたデバイスは学会レベルでは80年代から登場している。はじめは主に軍事や宇宙向けの高信頼性デバイス向けが主流だったようだ。

大きな転機になったのは1998年のIBMのPowerPCだった。

最近でもWiiに搭載されているIBMのプロセッサやIBM・ソニー・東芝のCellプロセッサなどはSOIを用いている。

他にSOIデバイスを生産しているメーカーとしてはAMDやフリースケールなどが上げられる。Intelがまだ用いていないというのは対照的。

素子の特徴

*容量の低減

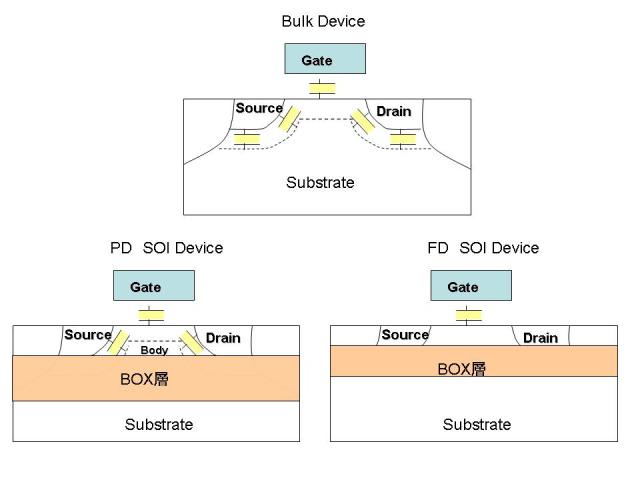

SOIデバイスの特徴は通常のBulk型のデバイスと比べて素子直下に埋め込み絶縁膜(BOX:BuriedOxide)が存在することである。このBOX層の存在によりS/D拡散層容量が低減される。またドレインに電圧が加えられた時のBulk層とのp-n接合リーク電流が減少する。 CMOS回路の遅延は

tpd=CV/I

消費電力は

P=CV^2f

Cは容量、Vは電圧、Iは電流、fは動作周波数

とあらわされるのでSOIデバイスは遅延低減と低消費電力という面でも重要である。

*基板バイアス無し

Bulkデバイスでは縦積みのNAND、OR回路において出力側の素子に基板バイアスがかかって閾値が変動し、駆動力が減少してしまうことがあるがSOIでは酸化膜で区切られているのでその心配が無い。

*ラッチアップ、素子分離

CMOS特有の問題としてラッチアップがあり同一基板上にP-well、N-wellを作るBulkデバイスではレイアウトに制限を受けやすいがSOIではその心配が無くレイアウトの自由度が増し、面積の縮小につながる。

*放射線耐性

放射線の入射で生じる正孔-電子対によるソフトエラーの影響を受けにくい。

*ノイズが少ない

携帯電話、画像処理などでアナログ回路+デジタル回路を同一基板に作る際にアナログ回路がデジタル回路から受けるノイズ(クロストークノイズ)の影響をBOX酸化膜により防げる。

またBOX層で区切った領域に高抵抗基板を用いることができるのでオンチップインダクタ(アナログ用の基板上のコイル)のQ値を改善できる。

SOIウエハ

SOIのウエハ作成方法に各種ある。

*種結晶からのエピ成長、堆積、アニ-ルによる作成

(成長速度が遅い)

*ウエハー張り合わせ+エッチバック

…2枚のウエハーを酸化膜を中心に張り合わせて基板にする方をエッチバック

(エッチングの面均が厳しい)

*SIMOX

…酸素イオンを加速器にて注入。その後にアニールによりBOX層を形成

(結晶欠陥の回復が困難)

*Layer Transfer

…Siウエハー全体を酸化、その後水素をイオン注入してそのウエハーをボンディング、注入水素を界面にして酸化側のウエハーを剥がす。

フランスのLETI社が開発、その後SOITECとして独立。日本では信越化学がライセンス生産している。

SOIデバイスの動作の特徴

SOIのデバイスは大きく部分空乏型(Partially-Depleted:PD)と完全空乏型(Fully-Depleted:FD)に分類される。

PDはSOI膜厚 Tsoi>Wd(空乏層)であり、BOX層の上のSiがデバイス動作時に部分的に空乏化している。そのために基板浮遊効果が存在し、サブスレショルド特性は変則的なものになる。

一方、FDはTsoi<Wd(空乏層)であり基板浮遊効果が無く、理想的なサブ特性を示す。

基板浮遊効果:

SOIデバイスにおいてゲートがONし電流が流れている際にインパクトイオン化により空乏領域にHoleが蓄積され、空乏領域の電位が上がることによってせいの基板バイアスが印加された状態になることである。=閾値が下がり、S-factorも悪化する。また閾値が下がることによってOff電流が増加したり、サブ特性がバラツクことが報告されている。

さらにはゲート電圧を一定にしてドレイン電圧を上げていった場合、インパクトイオン化が顕在してドレイン電流が急激に増えるKinkが発生することが報告されている。

基板浮遊効果を抑制するにはチャネル部にコンタクトを追加することが考えられる(BodyContact)。

ヒストリー効果:

回路のゲートの動作履歴によって遅延が変動する現象、ゲートが駆動されるまでどれほどの待機時間があったかでゲート遅延が変わる。原因としては基板浮遊効果と同様に空乏化部分での電荷の蓄積があげられる。

対策としてわざとドレイン-ボディ間に結晶欠陥を誘起させリークを増やすという手法もある。

多くのSOIデバイスはPD-SOIである。これはBOX層、SOI層ともにばらつきを抑えて薄く作ることが困難であるからである。

FD-SOIデバイス

PD-SOIに比べFD-SOIは良いところが多い。

SOI層が完全に空乏化しているためにチャネル下の容量は空乏層容量とBOX層の容量の和のみになる。このため低容量になり急峻なS-factorが得られる。またチャネル下の不純物バラツキの影響を受けにくい。=閾値のばらつきが少ない。

逆に問題となるのはSOI膜厚のばらつきでありSOI膜厚のばらつきが寄生抵抗や閾値のばらつきに影響する。

SOI膜厚:

薄くするとカットオフが効くので短チャネル効果の抑制になるが

ソース/ドレイン抵抗が高くなる

BOX膜厚:

薄くするとDIBL抑制されるがソース/ドレイン容量が増加、耐圧も劣化する。

セルフヒーティング:

下にBOX層があるために熱が放熱されず、電流が劣化する。

SOI膜厚を薄く作ることが非常に難しいことから実際のデバイスにはあまり用いられていないが沖電気の作った時計用の低消費電力デバイスが有名である。

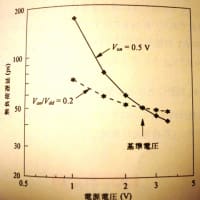

FD-SOIを利用することにより急峻なS-Factorを実現し、0.5Vという低電力で駆動できるデバイスを実現している。

こちら

このような問題からFD-SOIはまだ実際のデバイスに用いられている例は少ない。

SOI(Silicon-On-Insulator)を用いたデバイスは学会レベルでは80年代から登場している。はじめは主に軍事や宇宙向けの高信頼性デバイス向けが主流だったようだ。

大きな転機になったのは1998年のIBMのPowerPCだった。

最近でもWiiに搭載されているIBMのプロセッサやIBM・ソニー・東芝のCellプロセッサなどはSOIを用いている。

他にSOIデバイスを生産しているメーカーとしてはAMDやフリースケールなどが上げられる。Intelがまだ用いていないというのは対照的。

素子の特徴

*容量の低減

SOIデバイスの特徴は通常のBulk型のデバイスと比べて素子直下に埋め込み絶縁膜(BOX:BuriedOxide)が存在することである。このBOX層の存在によりS/D拡散層容量が低減される。またドレインに電圧が加えられた時のBulk層とのp-n接合リーク電流が減少する。 CMOS回路の遅延は

tpd=CV/I

消費電力は

P=CV^2f

Cは容量、Vは電圧、Iは電流、fは動作周波数

とあらわされるのでSOIデバイスは遅延低減と低消費電力という面でも重要である。

*基板バイアス無し

Bulkデバイスでは縦積みのNAND、OR回路において出力側の素子に基板バイアスがかかって閾値が変動し、駆動力が減少してしまうことがあるがSOIでは酸化膜で区切られているのでその心配が無い。

*ラッチアップ、素子分離

CMOS特有の問題としてラッチアップがあり同一基板上にP-well、N-wellを作るBulkデバイスではレイアウトに制限を受けやすいがSOIではその心配が無くレイアウトの自由度が増し、面積の縮小につながる。

*放射線耐性

放射線の入射で生じる正孔-電子対によるソフトエラーの影響を受けにくい。

*ノイズが少ない

携帯電話、画像処理などでアナログ回路+デジタル回路を同一基板に作る際にアナログ回路がデジタル回路から受けるノイズ(クロストークノイズ)の影響をBOX酸化膜により防げる。

またBOX層で区切った領域に高抵抗基板を用いることができるのでオンチップインダクタ(アナログ用の基板上のコイル)のQ値を改善できる。

SOIウエハ

SOIのウエハ作成方法に各種ある。

*種結晶からのエピ成長、堆積、アニ-ルによる作成

(成長速度が遅い)

*ウエハー張り合わせ+エッチバック

…2枚のウエハーを酸化膜を中心に張り合わせて基板にする方をエッチバック

(エッチングの面均が厳しい)

*SIMOX

…酸素イオンを加速器にて注入。その後にアニールによりBOX層を形成

(結晶欠陥の回復が困難)

*Layer Transfer

…Siウエハー全体を酸化、その後水素をイオン注入してそのウエハーをボンディング、注入水素を界面にして酸化側のウエハーを剥がす。

フランスのLETI社が開発、その後SOITECとして独立。日本では信越化学がライセンス生産している。

SOIデバイスの動作の特徴

SOIのデバイスは大きく部分空乏型(Partially-Depleted:PD)と完全空乏型(Fully-Depleted:FD)に分類される。

PDはSOI膜厚 Tsoi>Wd(空乏層)であり、BOX層の上のSiがデバイス動作時に部分的に空乏化している。そのために基板浮遊効果が存在し、サブスレショルド特性は変則的なものになる。

一方、FDはTsoi<Wd(空乏層)であり基板浮遊効果が無く、理想的なサブ特性を示す。

基板浮遊効果:

SOIデバイスにおいてゲートがONし電流が流れている際にインパクトイオン化により空乏領域にHoleが蓄積され、空乏領域の電位が上がることによってせいの基板バイアスが印加された状態になることである。=閾値が下がり、S-factorも悪化する。また閾値が下がることによってOff電流が増加したり、サブ特性がバラツクことが報告されている。

さらにはゲート電圧を一定にしてドレイン電圧を上げていった場合、インパクトイオン化が顕在してドレイン電流が急激に増えるKinkが発生することが報告されている。

基板浮遊効果を抑制するにはチャネル部にコンタクトを追加することが考えられる(BodyContact)。

ヒストリー効果:

回路のゲートの動作履歴によって遅延が変動する現象、ゲートが駆動されるまでどれほどの待機時間があったかでゲート遅延が変わる。原因としては基板浮遊効果と同様に空乏化部分での電荷の蓄積があげられる。

対策としてわざとドレイン-ボディ間に結晶欠陥を誘起させリークを増やすという手法もある。

多くのSOIデバイスはPD-SOIである。これはBOX層、SOI層ともにばらつきを抑えて薄く作ることが困難であるからである。

FD-SOIデバイス

PD-SOIに比べFD-SOIは良いところが多い。

SOI層が完全に空乏化しているためにチャネル下の容量は空乏層容量とBOX層の容量の和のみになる。このため低容量になり急峻なS-factorが得られる。またチャネル下の不純物バラツキの影響を受けにくい。=閾値のばらつきが少ない。

逆に問題となるのはSOI膜厚のばらつきでありSOI膜厚のばらつきが寄生抵抗や閾値のばらつきに影響する。

SOI膜厚:

薄くするとカットオフが効くので短チャネル効果の抑制になるが

ソース/ドレイン抵抗が高くなる

BOX膜厚:

薄くするとDIBL抑制されるがソース/ドレイン容量が増加、耐圧も劣化する。

セルフヒーティング:

下にBOX層があるために熱が放熱されず、電流が劣化する。

SOI膜厚を薄く作ることが非常に難しいことから実際のデバイスにはあまり用いられていないが沖電気の作った時計用の低消費電力デバイスが有名である。

FD-SOIを利用することにより急峻なS-Factorを実現し、0.5Vという低電力で駆動できるデバイスを実現している。

こちら

このような問題からFD-SOIはまだ実際のデバイスに用いられている例は少ない。