遅ればせながら、tinySA Ultraを入手。

オフィシャルページの案内に従って、Zeenko storeから購入。

1週間くらいで届きました。

https://tinysa.org/wiki/pmwiki.php?n=Main.Buying

ファームウェアは最新だったので、セルフチェックとキャリブレーションを実行。

もちろん、Ultra modeをenableする。

https://tinysa.org/wiki/pmwiki.php?n=Main.FirstUse

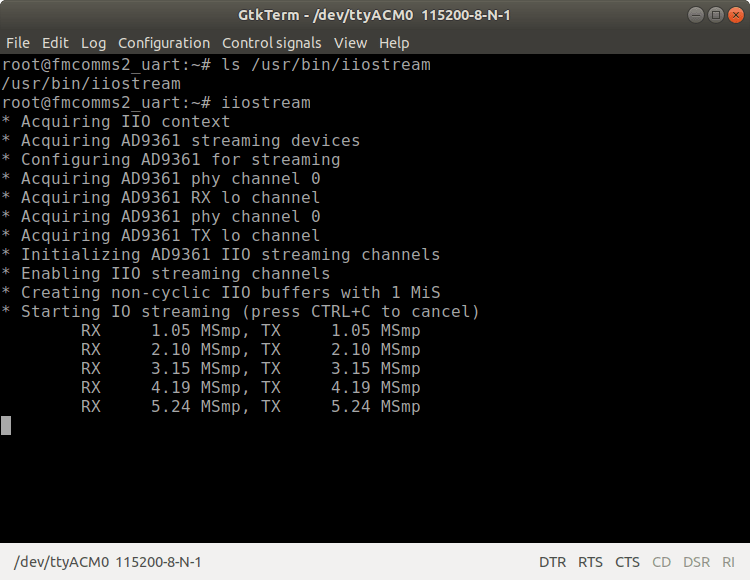

SDRの開発が捗る!

P.S. 収納用にエレコムのセミハードケースをチョイス。

https://www.elecom.co.jp/products/HDC-SH002BK.html

オフィシャルページの案内に従って、Zeenko storeから購入。

1週間くらいで届きました。

https://tinysa.org/wiki/pmwiki.php?n=Main.Buying

ファームウェアは最新だったので、セルフチェックとキャリブレーションを実行。

もちろん、Ultra modeをenableする。

https://tinysa.org/wiki/pmwiki.php?n=Main.FirstUse

SDRの開発が捗る!

P.S. 収納用にエレコムのセミハードケースをチョイス。

https://www.elecom.co.jp/products/HDC-SH002BK.html