MOSFETは日本語で言うと電界効果型トランジスタであり、n型MOSFETを例にとって言うとp型基板に二つのn+領域(ソース、ドレイン)、酸化膜を挟んでポリシリコン、金属ゲートが存在する4端子のデバイスである。デバイスの中央部分は前述したMOS構造になっており、この部分に電圧をかけて反転層を形成し、ソース→ドレインにキャリア(電子、正孔)を流すことによってスイッチングをおこなうデバイスである。(電流は逆)

MOSFETの基本的特性

ゲートに正の電圧Vgを印加して反転層が形成されている時、ソース・ドレイン間に電圧Vdを加えるとnチャネル中の電子がソースからドレインの向きに流れる.ソース端をx=0、ドレイン端をx=Lとし、x点におけるチャネルの表面電子の電荷密度Qn(x)及び電界の強さをEx=-dV(x)/dxとした時の電流Idは次式で与えられる.

Id=WQn(x)μn・dV(x)/dx (1)

反転層は半導体内部から絶縁された薄い導電膜とみなすことができる.この導電膜中の電荷Qn(x)は絶縁膜の容量(単位面積当たりのCox)を閾値電圧Vth以上の電圧で充電することによって現れると考えられるので

Qn(x)=-Cox(Vgs-Vth) (2)

で与えられる。下図のようにソースと半導体基板を接地し,ドレインにVdを印加することによってx地点における電圧がV(x)になっているものとする.したがってその周辺を反転させるのに必要な電位はVth+V(x)となる.よって(2)式はQn=-Cox(Vg-Vth-V(x))となる.この式を(1)式に代入して両辺をxについて積分すると(ソース-ドレイン間でチャネルが均一に形成されるとすると,V(x)=(Vd/L)x と表せる)ドレイン電流Idは

Id=W/L・μnCox[(Vg-Vth)Vd-1/2Vd^2](4)

となる.閾値電圧は前述したMOS構造での閾値であり

Vth=√[2εsqNa(2Φb)]/C0+2Φb

である。

a)Vd≪Vg-Vthの場合

Vdが十分に小さいとすると(4)式は

Id=W/L・μnCox[(Vg-Vth)Vd] (5)

となり,Vd-Idは直線で近似できる.この状態では図1(a)のように半転層はゲートの下に一様に形成される.

b)Vd=Vg-Vthの場合(3極管領域)

Vdが大きくなるとドレインのnとp型基板で形成されるpn接合が逆バイアス状態となり,ドレイン領域から空乏層が広がるためにドレイン側のチャネルが狭くなる.その結果,Vd=Vg-Vthの場合はx=Lにおいてチャネルが切れてしまう.この状態を図1(b)に示す. このときのVdのことをピンチオフ電圧Vpと呼ぶ.(4)式は

Id=1/2・W/L・μnCox(Vg-Vth)^2 (6)

この式よりわかるようにピンチオフが生じるとIdはVdに依存しなくなる.

c)Vd>Vg-Vthの場合(5極管領域)

さらにVdを高くした場合はドレインの周辺は空乏層に囲まれてピンチオフ領域が図1(c)のように広がる.ピンチオフ領域に引き込まれた電子は強い電界のためドレインにそのまま流れる.この状態ではチャネル両端にかかる電圧が変化しないために電流値は(6)式で飽和する.しかしながらVdが増加するに従い,ピンチオフ点はソース側に少しずつ移動していくためチャネル長が小さくなり,チャネルの抵抗も小さくなる.この効果により実際のデバイスでは飽和領域においてもVdの値は少しずつ増加している.

理想的なMOSFETのId-Vg特性は下図のようになる。

サブスレショルド領域

ゲート電圧が低くて半導体表面がわずかしか反転していない場合のドレイン電流はサブスレショルド電流と呼ばれる。サブ領域においてはドリフトよりも拡散によって電流が決定される。MOSFETをn-p-nのバイポーラトランジスタと考えソースにおける表面ポテンシャルをVg-Vthと近似するとドレイン電流Idは

Id≒exp[q(Vg-Vth)/kT]となり指数関数的に変化する。

代表的な測定結果は下図の様になる。

この領域で定義されるパラメータにサブシュレショルドスイングS(S-factor)がある。Sファクターの定義はドレイン電流を一桁上げるのに必要なゲート電圧であり

S=log・1/[(dln(Id))/dVg]である。Sは室温で70-100mV/decである。

上に述べてきたサブ領域と直線領域、飽和領域の関係は下のようになる。

閾値の制御

MOSFETにおいて重要なのは閾値の制御である。理想的な閾値は

Vth=√[2εsqNa(2Φb)]/C0+2Φbであるが

実際には酸化膜のトラップ電荷、仕事関数の違いをを考慮するとフラットバンド電圧はシフトする。また基板にバックバイアスVbsが印加されると空乏層が広くなり、反転を起こすのに必要な電圧は高くなる。

したがって閾値Vthは下記のようになる。

Vth=Vfb+2Φb+√[2εsqNa(2Φb+Vbs)]/C0

閾値の制御にはイオン注入が用いられる。n-MOSFETではp型基板にp型のBを注入するとチャネルのドーピング濃度が上がるためにΦbが上がり、閾値も増加する。

p型MOSFETの場合はn型基板(or Well)なので閾値は減少する。

基板バイアス特性

基板にバイアスを印加した場合のバンド図の変化を下に示す.Vthよりも高い電圧が印加されていてバイアスをかけても反転層が消滅しない状態を考える.バイアス印加後もゲート-反転層間の電位は一定であるから酸化膜の容量をCoxとすると蓄えられる電荷は変化せずに一定でCoxVgである.一方,反転層-基板間に逆バイアスが印加されると図に示すように空乏層が伸びてドレイン側のアクセプタつまり容量Qdが増加する.ここで反転層での電子の電荷をQiとすると電荷総量は釣り合って常にQd+Qi=-CoxVgであるのでQdが増加すればQiは減少する.すなわち伝導度が悪くなるので無バイアス時と同様の伝導度を得るためにはゲート電圧をさらに高くしてやればよい.以上のことからバイアスを印加した際には閾値電圧は高くなる.バイアス-Vb(Vb>0)の印加された際の閾値電圧は

Vth=Vfb+2Φb+√[2εsqNa(2Φb+Vbs)]/C0

で表せる.基板バイアスは閾値がギリギリの場合のデバイスにおいて閾値を上げるのに用いられる。

実測のバックバイアス特性は下図の様になる。

MOSFETの基本的特性

ゲートに正の電圧Vgを印加して反転層が形成されている時、ソース・ドレイン間に電圧Vdを加えるとnチャネル中の電子がソースからドレインの向きに流れる.ソース端をx=0、ドレイン端をx=Lとし、x点におけるチャネルの表面電子の電荷密度Qn(x)及び電界の強さをEx=-dV(x)/dxとした時の電流Idは次式で与えられる.

Id=WQn(x)μn・dV(x)/dx (1)

反転層は半導体内部から絶縁された薄い導電膜とみなすことができる.この導電膜中の電荷Qn(x)は絶縁膜の容量(単位面積当たりのCox)を閾値電圧Vth以上の電圧で充電することによって現れると考えられるので

Qn(x)=-Cox(Vgs-Vth) (2)

で与えられる。下図のようにソースと半導体基板を接地し,ドレインにVdを印加することによってx地点における電圧がV(x)になっているものとする.したがってその周辺を反転させるのに必要な電位はVth+V(x)となる.よって(2)式はQn=-Cox(Vg-Vth-V(x))となる.この式を(1)式に代入して両辺をxについて積分すると(ソース-ドレイン間でチャネルが均一に形成されるとすると,V(x)=(Vd/L)x と表せる)ドレイン電流Idは

Id=W/L・μnCox[(Vg-Vth)Vd-1/2Vd^2](4)

となる.閾値電圧は前述したMOS構造での閾値であり

Vth=√[2εsqNa(2Φb)]/C0+2Φb

である。

a)Vd≪Vg-Vthの場合

Vdが十分に小さいとすると(4)式は

Id=W/L・μnCox[(Vg-Vth)Vd] (5)

となり,Vd-Idは直線で近似できる.この状態では図1(a)のように半転層はゲートの下に一様に形成される.

b)Vd=Vg-Vthの場合(3極管領域)

Vdが大きくなるとドレインのnとp型基板で形成されるpn接合が逆バイアス状態となり,ドレイン領域から空乏層が広がるためにドレイン側のチャネルが狭くなる.その結果,Vd=Vg-Vthの場合はx=Lにおいてチャネルが切れてしまう.この状態を図1(b)に示す. このときのVdのことをピンチオフ電圧Vpと呼ぶ.(4)式は

Id=1/2・W/L・μnCox(Vg-Vth)^2 (6)

この式よりわかるようにピンチオフが生じるとIdはVdに依存しなくなる.

c)Vd>Vg-Vthの場合(5極管領域)

さらにVdを高くした場合はドレインの周辺は空乏層に囲まれてピンチオフ領域が図1(c)のように広がる.ピンチオフ領域に引き込まれた電子は強い電界のためドレインにそのまま流れる.この状態ではチャネル両端にかかる電圧が変化しないために電流値は(6)式で飽和する.しかしながらVdが増加するに従い,ピンチオフ点はソース側に少しずつ移動していくためチャネル長が小さくなり,チャネルの抵抗も小さくなる.この効果により実際のデバイスでは飽和領域においてもVdの値は少しずつ増加している.

理想的なMOSFETのId-Vg特性は下図のようになる。

サブスレショルド領域

ゲート電圧が低くて半導体表面がわずかしか反転していない場合のドレイン電流はサブスレショルド電流と呼ばれる。サブ領域においてはドリフトよりも拡散によって電流が決定される。MOSFETをn-p-nのバイポーラトランジスタと考えソースにおける表面ポテンシャルをVg-Vthと近似するとドレイン電流Idは

Id≒exp[q(Vg-Vth)/kT]となり指数関数的に変化する。

代表的な測定結果は下図の様になる。

この領域で定義されるパラメータにサブシュレショルドスイングS(S-factor)がある。Sファクターの定義はドレイン電流を一桁上げるのに必要なゲート電圧であり

S=log・1/[(dln(Id))/dVg]である。Sは室温で70-100mV/decである。

上に述べてきたサブ領域と直線領域、飽和領域の関係は下のようになる。

閾値の制御

MOSFETにおいて重要なのは閾値の制御である。理想的な閾値は

Vth=√[2εsqNa(2Φb)]/C0+2Φbであるが

実際には酸化膜のトラップ電荷、仕事関数の違いをを考慮するとフラットバンド電圧はシフトする。また基板にバックバイアスVbsが印加されると空乏層が広くなり、反転を起こすのに必要な電圧は高くなる。

したがって閾値Vthは下記のようになる。

Vth=Vfb+2Φb+√[2εsqNa(2Φb+Vbs)]/C0

閾値の制御にはイオン注入が用いられる。n-MOSFETではp型基板にp型のBを注入するとチャネルのドーピング濃度が上がるためにΦbが上がり、閾値も増加する。

p型MOSFETの場合はn型基板(or Well)なので閾値は減少する。

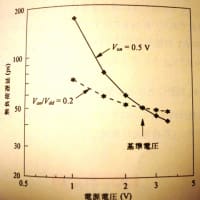

基板バイアス特性

基板にバイアスを印加した場合のバンド図の変化を下に示す.Vthよりも高い電圧が印加されていてバイアスをかけても反転層が消滅しない状態を考える.バイアス印加後もゲート-反転層間の電位は一定であるから酸化膜の容量をCoxとすると蓄えられる電荷は変化せずに一定でCoxVgである.一方,反転層-基板間に逆バイアスが印加されると図に示すように空乏層が伸びてドレイン側のアクセプタつまり容量Qdが増加する.ここで反転層での電子の電荷をQiとすると電荷総量は釣り合って常にQd+Qi=-CoxVgであるのでQdが増加すればQiは減少する.すなわち伝導度が悪くなるので無バイアス時と同様の伝導度を得るためにはゲート電圧をさらに高くしてやればよい.以上のことからバイアスを印加した際には閾値電圧は高くなる.バイアス-Vb(Vb>0)の印加された際の閾値電圧は

Vth=Vfb+2Φb+√[2εsqNa(2Φb+Vbs)]/C0

で表せる.基板バイアスは閾値がギリギリの場合のデバイスにおいて閾値を上げるのに用いられる。

実測のバックバイアス特性は下図の様になる。