現在、地球上で用いられているトランジスタのほとんどは電界効果型のトランジスタである。これらはMOSFET(Metal-Oxide-Semiconductor Field Effect Transister)とよばれMOSダイオードと隣接したp-n接合からなっている。p-n-pやn-p-nの接合を用いるバイポーラトランジスタと比べて電圧でチャネルをオンさせるために低消費電力である、省スペース、スケーリングが容易という特徴がある。

MOSというのが一般的であるが広義的に言えばMIS(Metal-Isulator-Semiconductor)

ここでは先ず始めに基本であるMOS構造についてまとめていく。

理想的MOS構造

MOSダイオードの概略図とエネルギーバンド図を示す。

仕事関数qΦs、qΦmはフェルミ準位と真空準位の差であり電気親和力qχは伝導帯Ecと真空準位の差である。理想的なMOS構造における外部電圧の加えられていない熱平衡状態においてはシリコンの仕事関数qΦs、金属の仕事関数qΦmは一致してフラットバンドの状態になる。

qΦm=qΦm-qΦs=qΦm-(qχ+Eg/2+qΨB)

qΨBはフェルミ準位と真性フェルミ準位との差

このようなダイオードのゲート側(メタル側)に電圧を印加した場合を考える。

①負のバイアスが印加された場合(蓄積状態)

過剰な正孔キャリアがSi-SiO2界面に誘起されバンドが上方に曲がる。

半導体のキャリア濃度はEi-Efに指数関数的に依存する。

正孔濃度Pp=ni・exp[(Ei-Ef)/kT]

バンドが上向きに曲がるとEi-Efは増大するため正孔の濃度は増加する。

この状態を蓄積という。

②小さな正の電圧が印加された場合(空乏状態)

エネルギーバンドは下に曲がり多数キャリアである正孔はSi-SiO2の界面から遠ざけられる。このような状態を空乏という。

③さらに大きな正電圧が印加された場合(反転状態)

さらにバンドは下向きに曲がり真性フェルミ準位Eiとフェルミ準位Efが交差するようになる。これは表面のみn型半導体になっている事と等価でありこのときの電子濃度は

np=niexp[(Ef-Ei)/kT]で与えられる。

始めは電子濃度も少なく弱反転であるが電圧を印加していくと反転層の電子濃度がSiO2-Si界面の基板のドーピングレベルに達してから強い反転がおこる。(強反転)

反転層の幅は1~10nm程度であり空乏層の幅よりもはるかに小さい。強反転が起こると空乏層幅は増加せず反転層の電荷Qnが増加する。

強反転の状態では表面の電荷Qsは反転層の電荷Qnと空乏層の空間電荷Qscの和になる。

Qs=Qn+Qsc=Qn-qNaWn

強反転の起こるのは反転層の電子濃度nsと基板の不純物濃度Naが等しくなる場所である。つまり

Ψs=2Ψb=2kT/q・ln(Na/ni)

であり基板が真性フェルミ準位になるためにΨb必要でありさらに強反転させるのにΨb必要であることを示している。

最大空乏層幅はこのときのΨsを代入して

W=2√[{εkT・ln(Na/ni)}/{q^2Na}]

と求められる。

MOSダイオードにおける全容量Cは酸化膜の容量C0と空乏層の容量Cjを直列につないだものである。

C=C0Cj/(C0+Cj)F/cm^2

これから

C/C0=1/√(1+(2εox^2・V)/(qNaεd^2))

となる。この式から半導体表面で空乏化している場合は容量がゲート電圧の増加に伴って減少することを示している。印加電圧が負の状態では空乏層はできないので酸化膜の容量に近くなる。

強い反転が起こる場合は空乏層幅は増えないので容量も最小で一定になる。

強い反転の起こる閾値電圧は

Vt=qNaWn/C0+Ψs(inv)でありCj=εs/Wnとなるので

容量の最小値はCmin=εox/(d+(εox/εs)Wn)

閾値電圧Vthは

Vth=qNaW/C0+Ψinv≒√[2εsqNa(2Φb)]/C0+2Φb

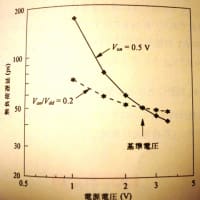

下図は理想的な場合の容量電圧特性である。

測定周波数が高い場合には反転キャリアがゲートの信号に追随できず左のような特性になるが周波数が低い場合には反転キャリアが追随できるようになるために強反転状態では酸化膜の容量に近くなる。周波数100Hz以下の領域では追随できるようになる。

高い周波数で同様の特性を得るためには意図的に光を当ててキャリアを発生させたり隣接した拡散層から電子を注入してやればよい。

フラットバンド電圧

実際のMOS構造では金属の仕事関数と半導体のフェルミ準位は一致していないので接触して電圧を印加していない熱平衡状態においてすでにバンドが曲がった構造をしている。理想的MOS構造におけるフラットバンド状態を実現するためには仕事関数差qΦmsに等しい正もしくは負の電圧を印加する必要がある。これをフラットバンド電圧(Vfb)という。

仕事関数はAlの場合4.1eV、n型多結晶シリコンの場合4.05eV、p型多結晶シリコンの場合は5.05eVである。基板の不純物濃度を変えると下記のように大きく仕事関数差が変化する。

界面とラップと酸化膜中の電荷

仕事関数差だけでなくMOSダイオードは酸化膜中の電荷、界面のトラップ電荷にも影響される。

表面準位によるトラップQit

界面の性質によってトラップされる。化学的組成に起因していて100界面では111界面に比べて約一桁トラップが少ない。この界面トラップは低温(450度)の水素アニールによって結合手を終端させることによって中和される。

酸化膜中の固定電荷Qf

界面から3nmに存在。酸化が終わった時にイオン化したSiが酸化膜中に残ったものとして考えることができる。

酸化膜トラップ電荷Qot

SiO2中の欠陥に起因する。

高エネルギー電子の照射、X線照射により発生する。アニールによって除去可能。

Na、アルカリイオンによる電荷Qm

高電界下で酸化膜中を移動する。このためC-Vカーブもシフトする。

仕事関数差が0でなく、界面補足電荷が無視できる場合、C-Vカーブは理想の場合から次の量ずれることになる。

Vfb=Φms-(Qf+Qm+Qot)/C0

下図のbはaの理想的な状態から平行移動した状態。

cは界面とラップの電荷によりゆがめられた場合のカーブである。

MOSというのが一般的であるが広義的に言えばMIS(Metal-Isulator-Semiconductor)

ここでは先ず始めに基本であるMOS構造についてまとめていく。

理想的MOS構造

MOSダイオードの概略図とエネルギーバンド図を示す。

仕事関数qΦs、qΦmはフェルミ準位と真空準位の差であり電気親和力qχは伝導帯Ecと真空準位の差である。理想的なMOS構造における外部電圧の加えられていない熱平衡状態においてはシリコンの仕事関数qΦs、金属の仕事関数qΦmは一致してフラットバンドの状態になる。

qΦm=qΦm-qΦs=qΦm-(qχ+Eg/2+qΨB)

qΨBはフェルミ準位と真性フェルミ準位との差

このようなダイオードのゲート側(メタル側)に電圧を印加した場合を考える。

①負のバイアスが印加された場合(蓄積状態)

過剰な正孔キャリアがSi-SiO2界面に誘起されバンドが上方に曲がる。

半導体のキャリア濃度はEi-Efに指数関数的に依存する。

正孔濃度Pp=ni・exp[(Ei-Ef)/kT]

バンドが上向きに曲がるとEi-Efは増大するため正孔の濃度は増加する。

この状態を蓄積という。

②小さな正の電圧が印加された場合(空乏状態)

エネルギーバンドは下に曲がり多数キャリアである正孔はSi-SiO2の界面から遠ざけられる。このような状態を空乏という。

③さらに大きな正電圧が印加された場合(反転状態)

さらにバンドは下向きに曲がり真性フェルミ準位Eiとフェルミ準位Efが交差するようになる。これは表面のみn型半導体になっている事と等価でありこのときの電子濃度は

np=niexp[(Ef-Ei)/kT]で与えられる。

始めは電子濃度も少なく弱反転であるが電圧を印加していくと反転層の電子濃度がSiO2-Si界面の基板のドーピングレベルに達してから強い反転がおこる。(強反転)

反転層の幅は1~10nm程度であり空乏層の幅よりもはるかに小さい。強反転が起こると空乏層幅は増加せず反転層の電荷Qnが増加する。

強反転の状態では表面の電荷Qsは反転層の電荷Qnと空乏層の空間電荷Qscの和になる。

Qs=Qn+Qsc=Qn-qNaWn

強反転の起こるのは反転層の電子濃度nsと基板の不純物濃度Naが等しくなる場所である。つまり

Ψs=2Ψb=2kT/q・ln(Na/ni)

であり基板が真性フェルミ準位になるためにΨb必要でありさらに強反転させるのにΨb必要であることを示している。

最大空乏層幅はこのときのΨsを代入して

W=2√[{εkT・ln(Na/ni)}/{q^2Na}]

と求められる。

MOSダイオードにおける全容量Cは酸化膜の容量C0と空乏層の容量Cjを直列につないだものである。

C=C0Cj/(C0+Cj)F/cm^2

これから

C/C0=1/√(1+(2εox^2・V)/(qNaεd^2))

となる。この式から半導体表面で空乏化している場合は容量がゲート電圧の増加に伴って減少することを示している。印加電圧が負の状態では空乏層はできないので酸化膜の容量に近くなる。

強い反転が起こる場合は空乏層幅は増えないので容量も最小で一定になる。

強い反転の起こる閾値電圧は

Vt=qNaWn/C0+Ψs(inv)でありCj=εs/Wnとなるので

容量の最小値はCmin=εox/(d+(εox/εs)Wn)

閾値電圧Vthは

Vth=qNaW/C0+Ψinv≒√[2εsqNa(2Φb)]/C0+2Φb

下図は理想的な場合の容量電圧特性である。

測定周波数が高い場合には反転キャリアがゲートの信号に追随できず左のような特性になるが周波数が低い場合には反転キャリアが追随できるようになるために強反転状態では酸化膜の容量に近くなる。周波数100Hz以下の領域では追随できるようになる。

高い周波数で同様の特性を得るためには意図的に光を当ててキャリアを発生させたり隣接した拡散層から電子を注入してやればよい。

フラットバンド電圧

実際のMOS構造では金属の仕事関数と半導体のフェルミ準位は一致していないので接触して電圧を印加していない熱平衡状態においてすでにバンドが曲がった構造をしている。理想的MOS構造におけるフラットバンド状態を実現するためには仕事関数差qΦmsに等しい正もしくは負の電圧を印加する必要がある。これをフラットバンド電圧(Vfb)という。

仕事関数はAlの場合4.1eV、n型多結晶シリコンの場合4.05eV、p型多結晶シリコンの場合は5.05eVである。基板の不純物濃度を変えると下記のように大きく仕事関数差が変化する。

界面とラップと酸化膜中の電荷

仕事関数差だけでなくMOSダイオードは酸化膜中の電荷、界面のトラップ電荷にも影響される。

表面準位によるトラップQit

界面の性質によってトラップされる。化学的組成に起因していて100界面では111界面に比べて約一桁トラップが少ない。この界面トラップは低温(450度)の水素アニールによって結合手を終端させることによって中和される。

酸化膜中の固定電荷Qf

界面から3nmに存在。酸化が終わった時にイオン化したSiが酸化膜中に残ったものとして考えることができる。

酸化膜トラップ電荷Qot

SiO2中の欠陥に起因する。

高エネルギー電子の照射、X線照射により発生する。アニールによって除去可能。

Na、アルカリイオンによる電荷Qm

高電界下で酸化膜中を移動する。このためC-Vカーブもシフトする。

仕事関数差が0でなく、界面補足電荷が無視できる場合、C-Vカーブは理想の場合から次の量ずれることになる。

Vfb=Φms-(Qf+Qm+Qot)/C0

下図のbはaの理想的な状態から平行移動した状態。

cは界面とラップの電荷によりゆがめられた場合のカーブである。