前回の記事(Intel 4004 (その5) Mask ROM 4001を読んでみる)では、4004と一緒に入っていたマスクROM(4001)の中身を読んでみました。2バイト目にリターン命令が入っていたので、複数ROMのプログラムの一部に使われていたものなのかなと思ってそれで終了だったのですが、実はそうではありませんでした。もしかしたらこのROM、4004よりレアなパーツかもしれません。

どうして気がついたのか、というあたりからとりあえず順を追って書いてみます。

Lチカ(Intel 4004 (その4) Lチカの巻)の次は簡単なモニタプログラムやインタプリタ言語が動くボードを作りたいなと思って、回路図を引いたりレイアウトを考えたりしていたのですが、部品を注文して届くまでにやることが無くなったので、アセンブラについて調べたり、ユーザーズマニュアルを調べていました。

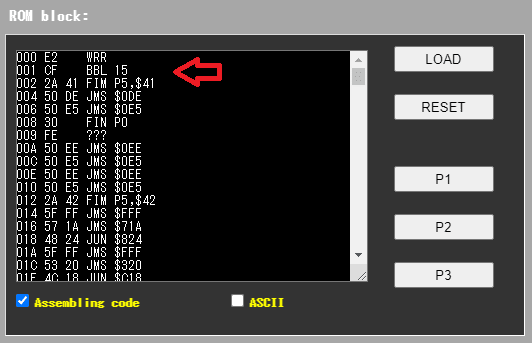

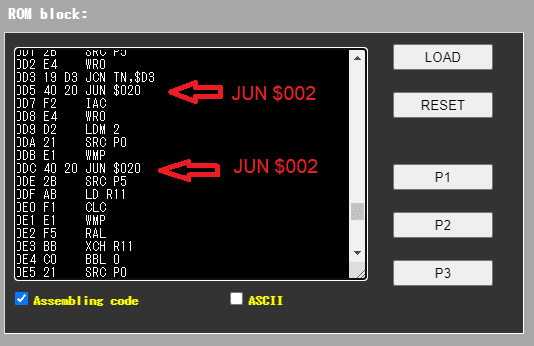

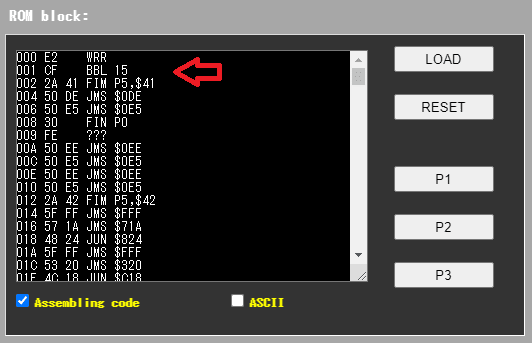

前回使ったディスアセンブラのところに、アセンブラとエミュレータ(INTEL 4004 SYSTEM EMULATOR)もあり、開発ツールに使えそうな感じ。エミュレータ用のサンプルプログラム(MCS-4 EVALUATION KIT USING THE 4001-0009)もあったので、ロードしてみると、2バイト目がリターン命令(BBL)です。

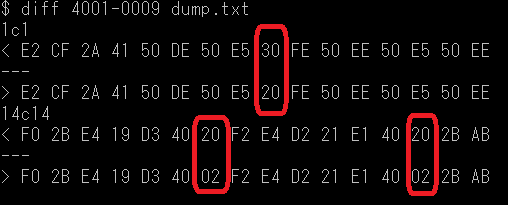

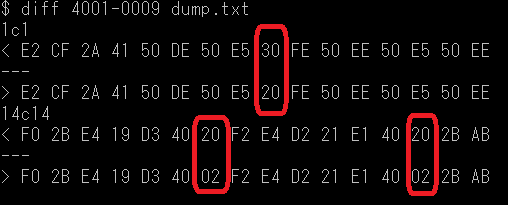

あれ?これはどこかで見たような・・・と思い、ROMのダンプリストとdiffをとってみたところ、なんと3バイト違うだけで残り253バイトは一致しています。

最初は、ROMリーダーが不完全でbit化けしてるんだろうなと思ったのですが、20が30はあるにしても、02が20、しかも2箇所はちょっと考えにくいです。

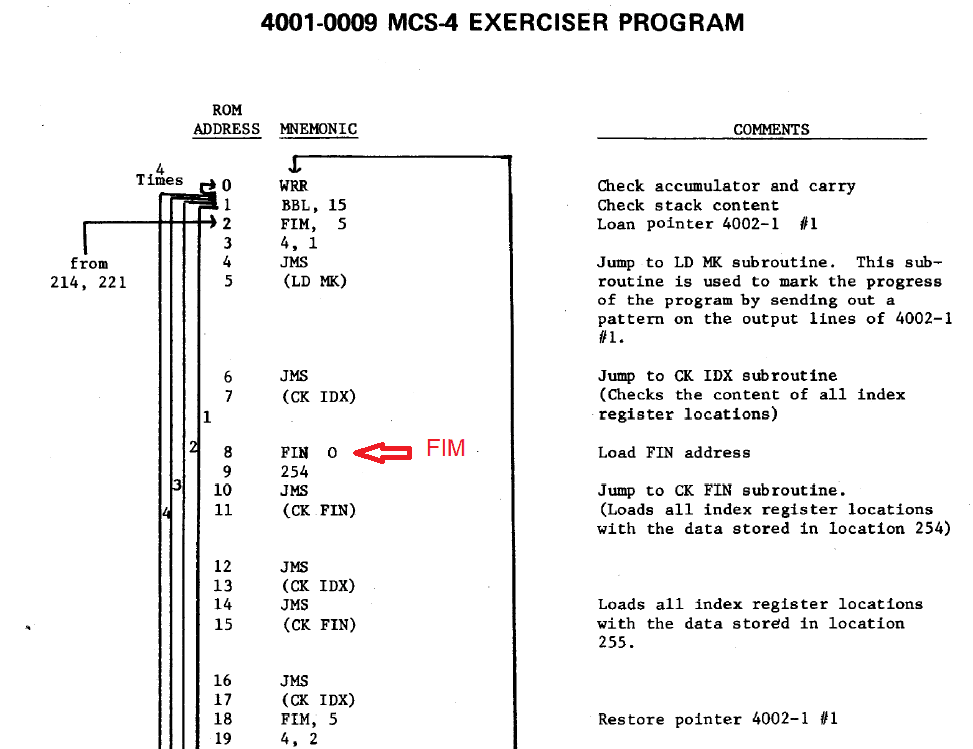

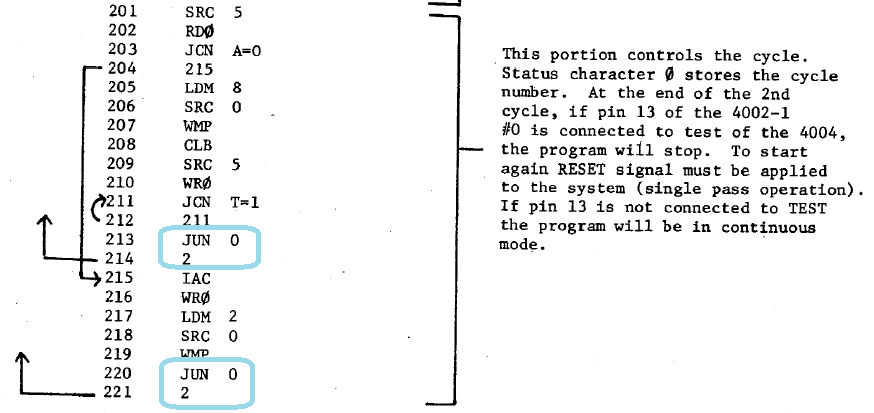

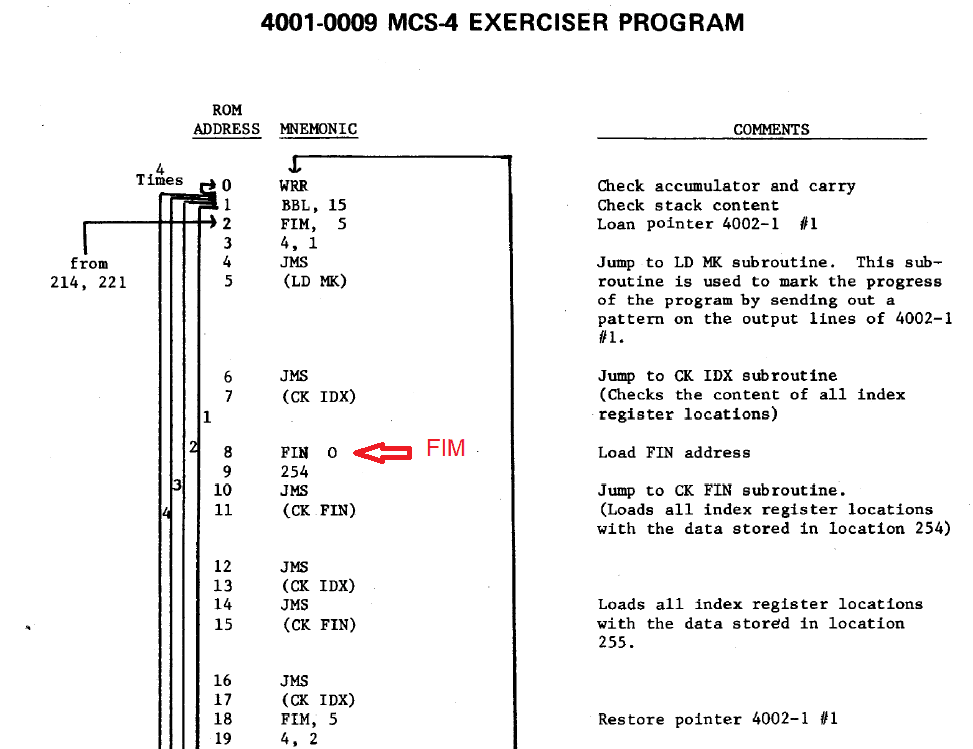

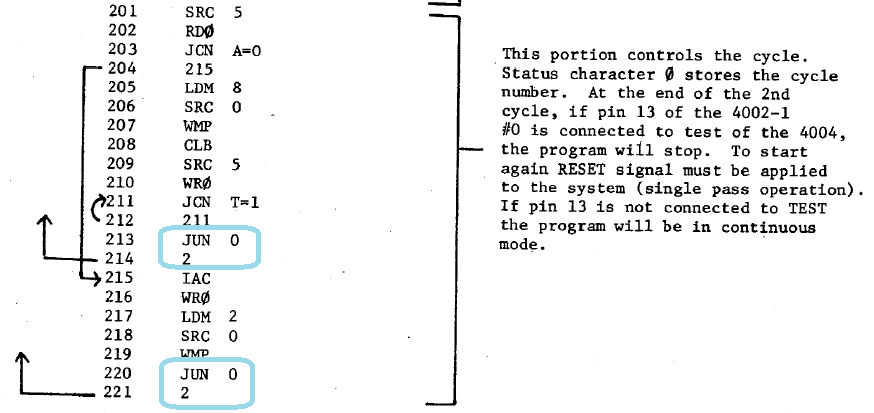

エミュレータのところにあった資料(MCS-4 Evaluation Kit using 4001-4009)にソースがあるので見てみると、

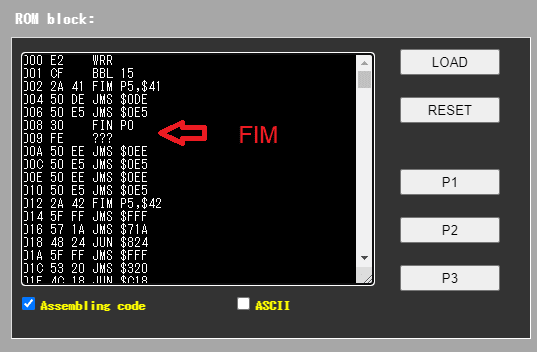

FINは1バイト命令なので次の254はおかしいです。エミュレータのアセンブルリストでもFE ???になっています。

プログラムの意味を考えても、これはROMのダンプのFIM(20)が正しいのでしょう。マニュアルの誤植だと思われます。

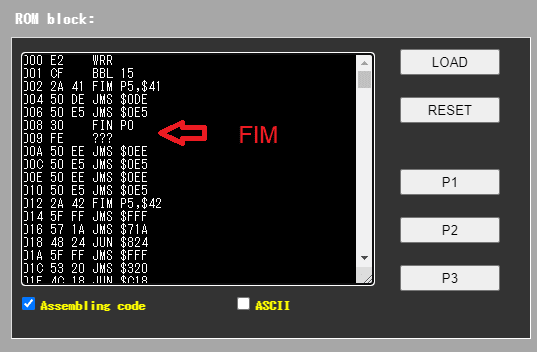

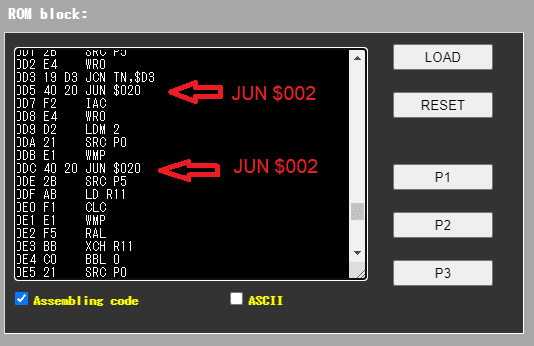

次に、20が02になっているところ。エミュレータでは20になっていますが、マニュアルでは2です。

これはエミュレータ側が間違っているようです。エミュレータの作者に連絡したいけど、連絡先が書いてないなあ。

ここまで調べてようやく、あれ?そういえば、このROMのパッケージに4001-0009って書いてあるよ!(最後の9がかすれてるけど)

ということに気がつきました。

ググってみてもマニュアル以外の情報にはヒットせず。これってもしかしてCPUの4004よりレアなパーツなのではないだろうか。

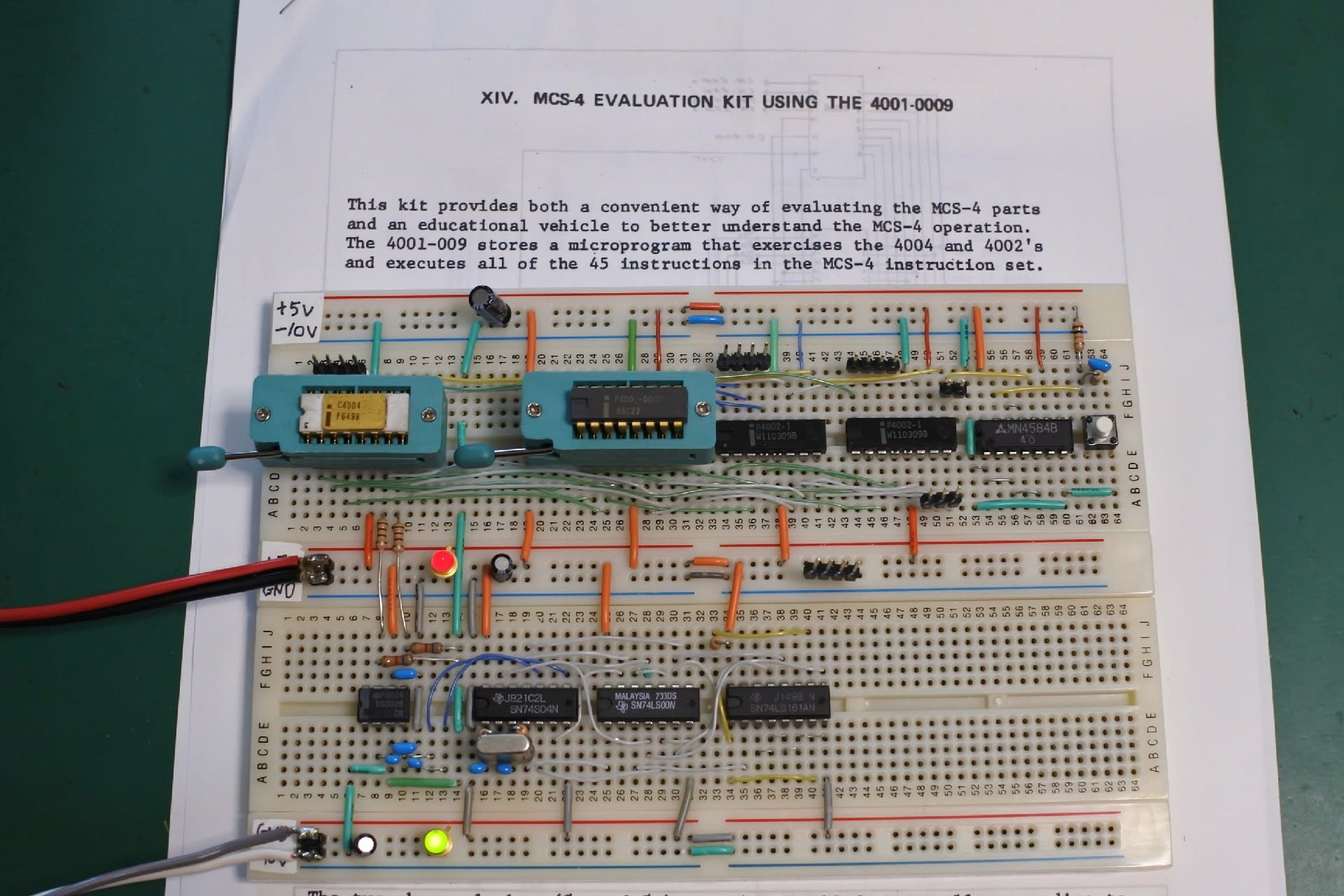

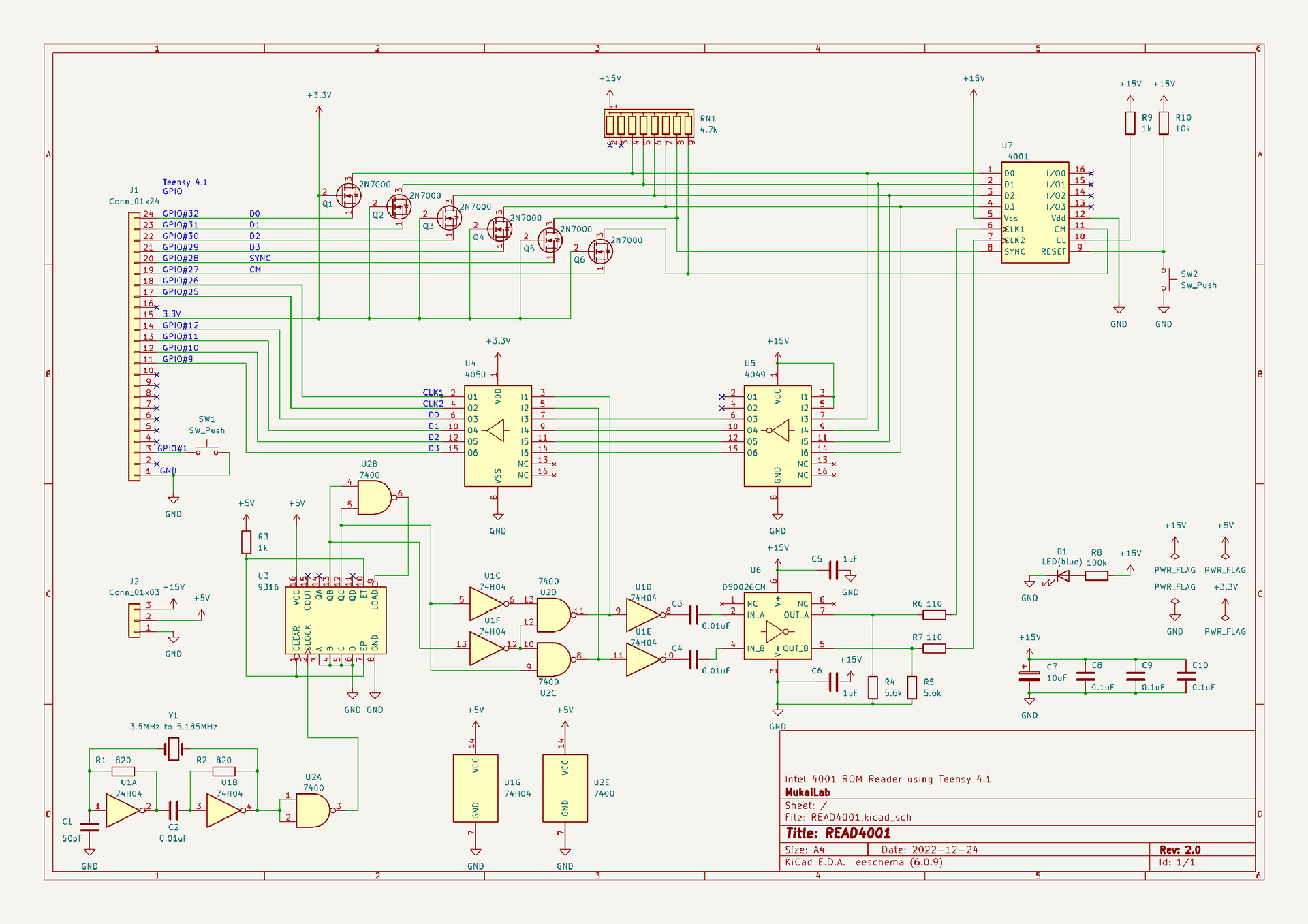

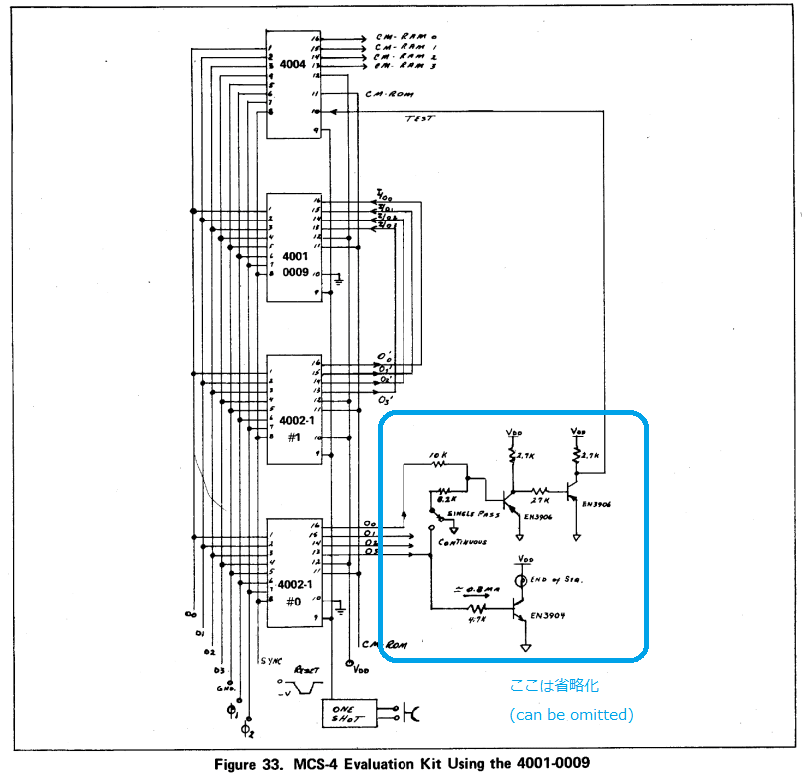

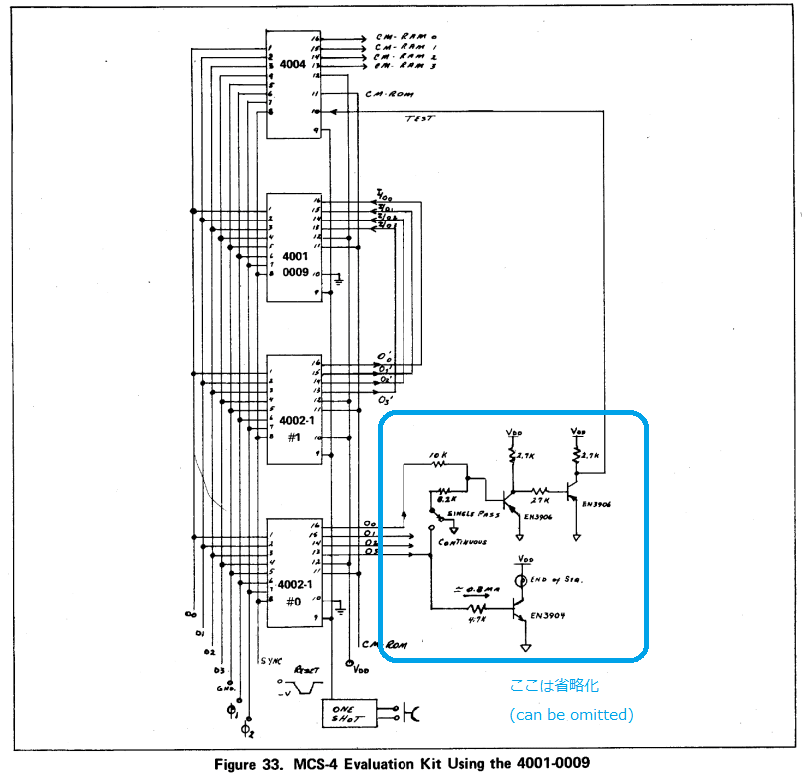

マニュアルの回路図を見ると非常にシンプル。しかも、トランジスタのフィードバック回路は省略可(The circuit for single pass/continuous can be omitted if only continuous operation is sought.)ということなので作ってみることにしました。(ちなみに私はアナログ回路はさっぱりわからないのでトランジスタの回路は敬遠しているのですが、たぶんこれってたぶん7404とか7407とかのバッファで代用できるよね。)

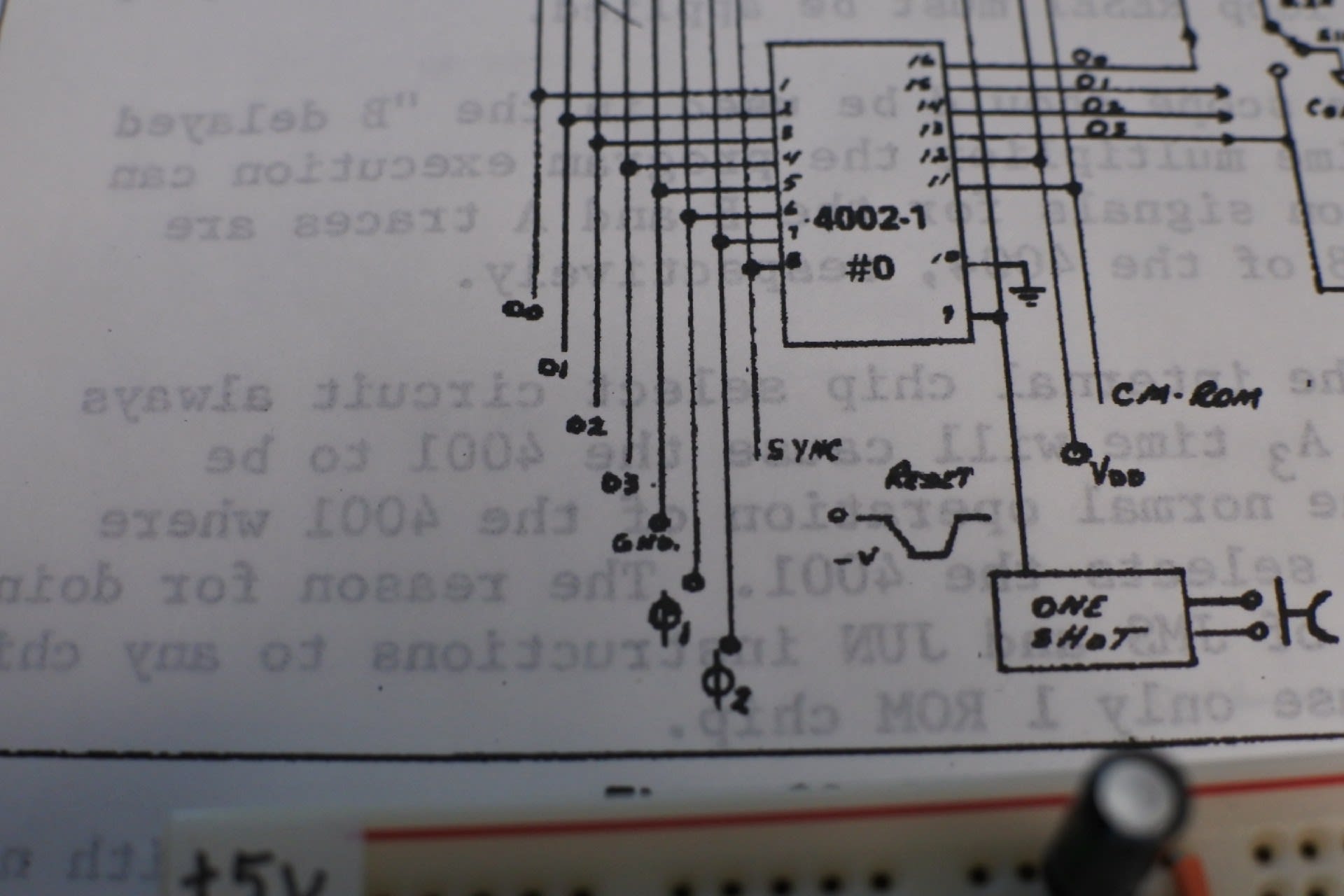

クロック回路が結構面倒なのでROMリーダーから流用しようかと思ったのですが、全部新しく作る方が見た目も良いので1日がかりでブレッドボードに組み立てました。で、電源を入れてみたのですが想定通りの波形は出ません。(そういう状態だと電源を入れていること自体がリスクなので写真を撮るのは省略しています。)

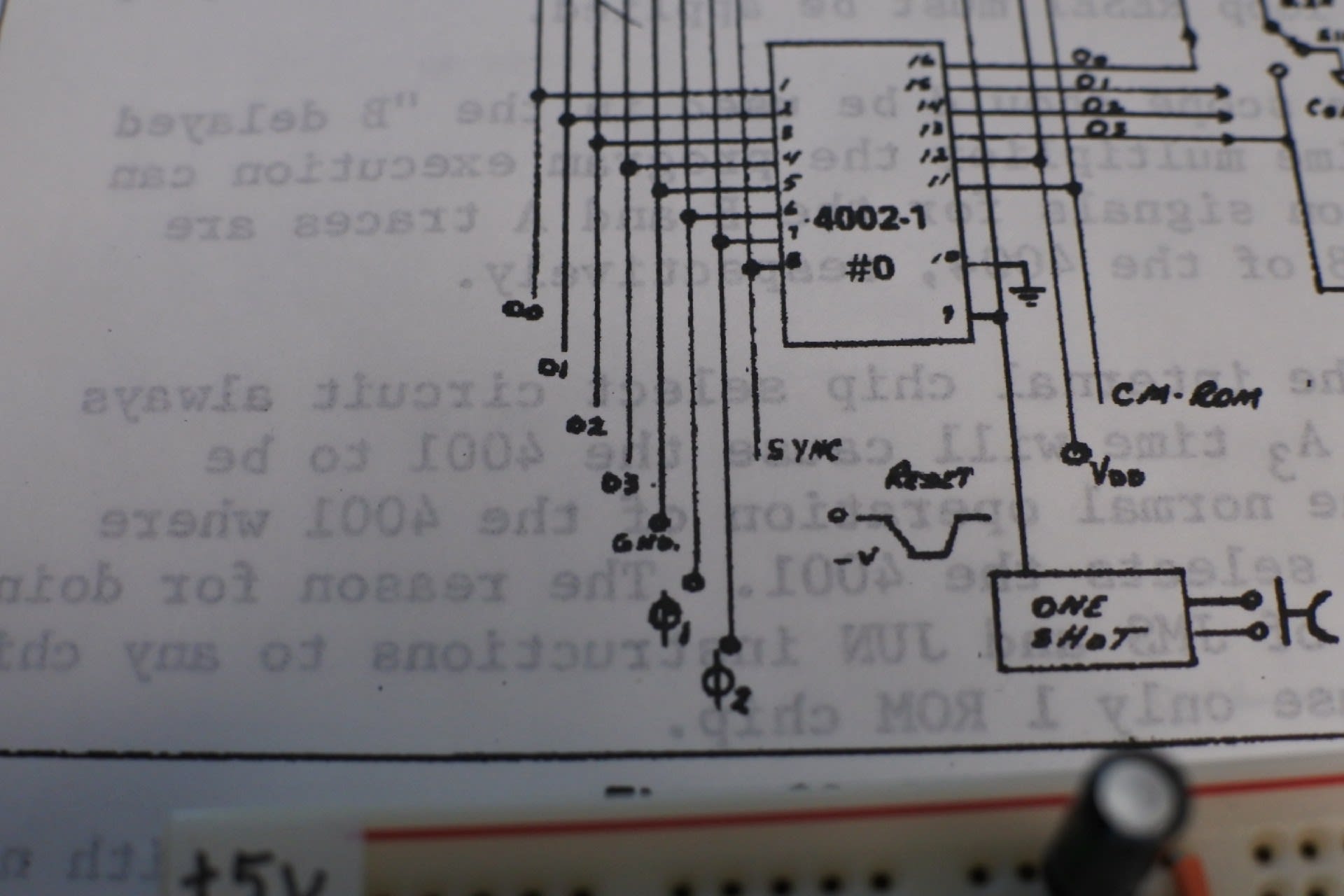

信号を見てみると、クロックはOK。しかし、4004が出力するはずのSYNC信号が出ていません。順に信号を確認したところ、RESET信号が出ていないことを発見。リセット信号を作る部分の配線ミスでした。

これでOKかと思って再度トライ。しかしまだSYNCが出ません。

うーん、4004と4001は動作確認済みだから、まだ動作確認してない4002が壊れていてSYNC端子に変な信号を出している可能性があるな!

と思って、Lチカボードで全チップの動作を確認したのですが全部正常。おかしいなあ。と思って回路図を確認したところ・・・

あれ?SYNC, CLK1, CLK2じゃなくて、CLK1, CLK2, SYNCなの?!

CLKの接続が間違っていて、CLK2(クロックドライバの出力, ドライブ力強い)をSYNC(4004の出力)に突っ込んでいました・・・

壊れなくて良かったあ。

教訓: 組んだ回路がおかしいときは部品よりも自分の配線を疑うべし。

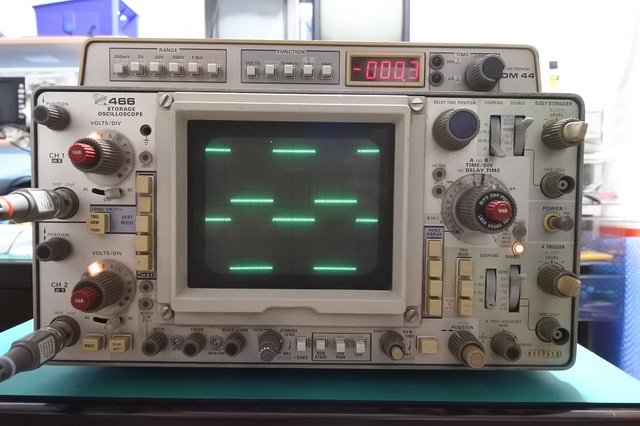

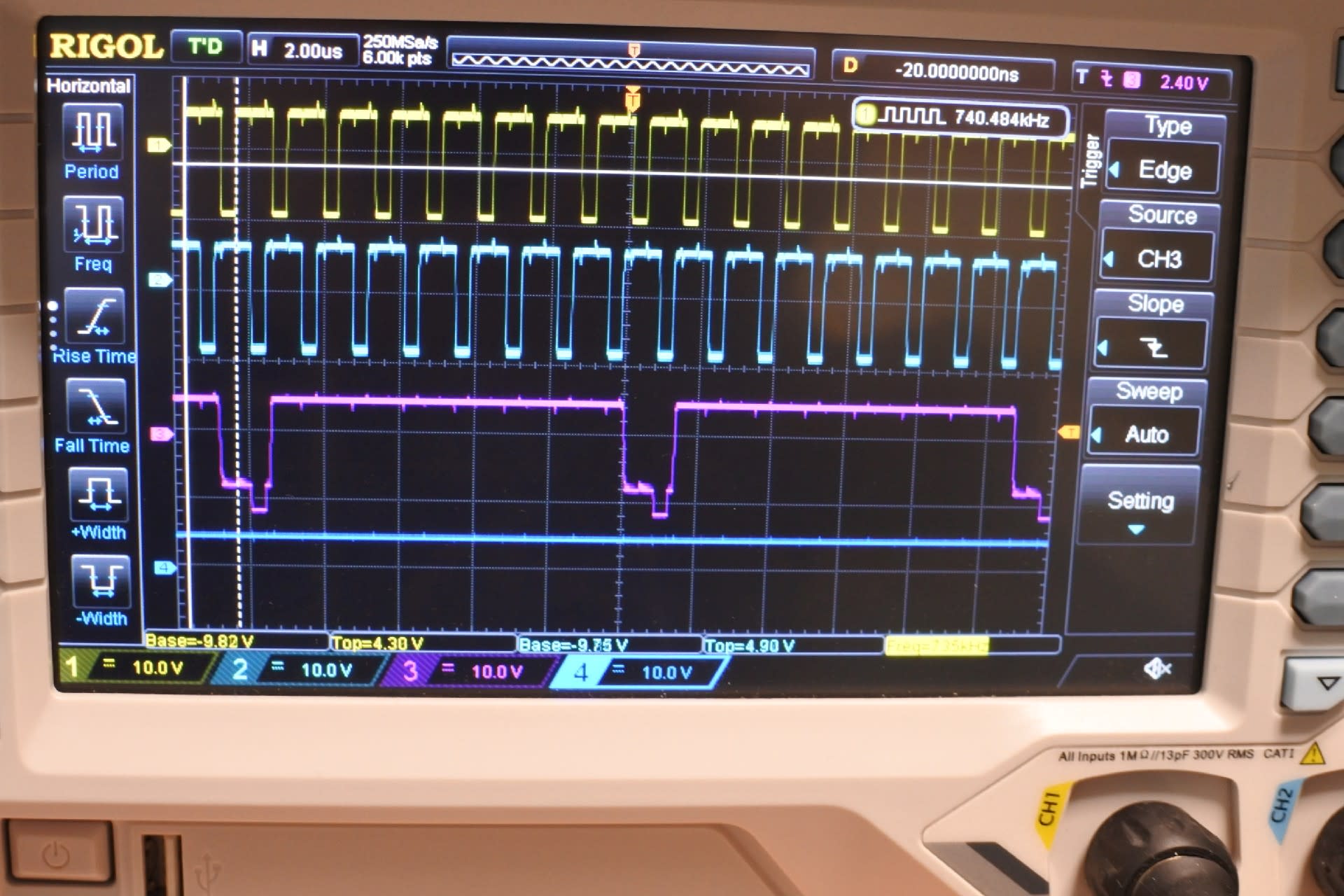

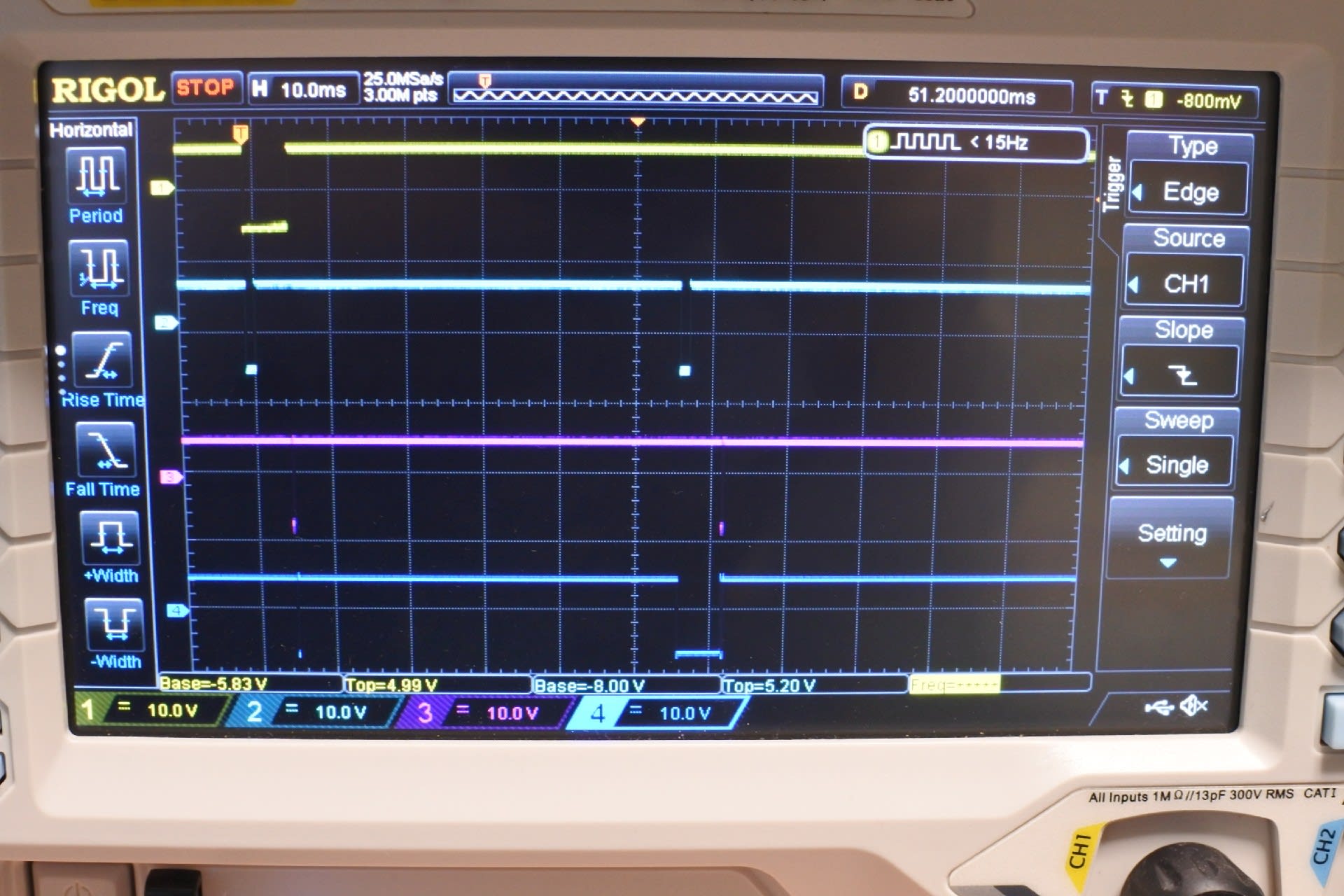

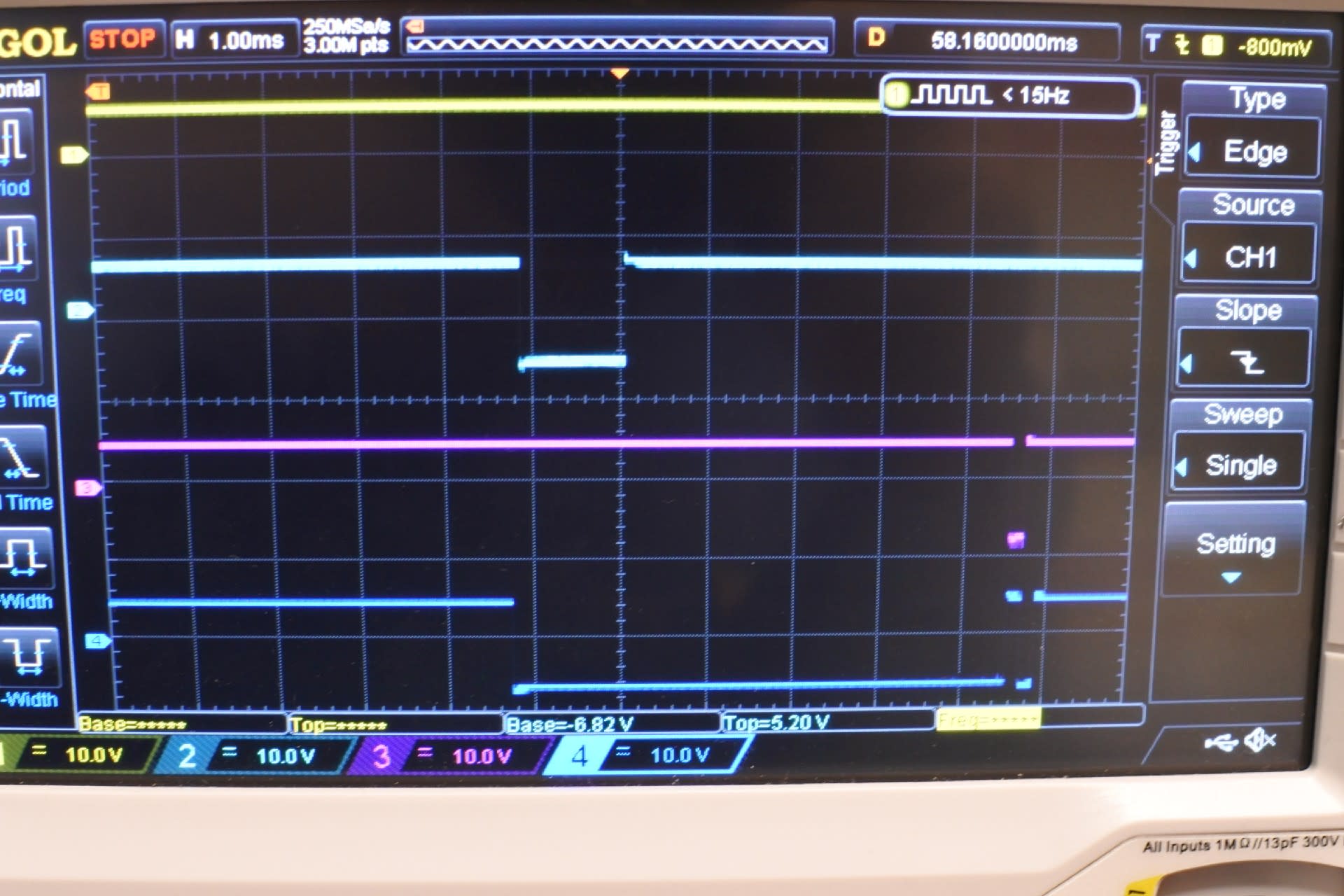

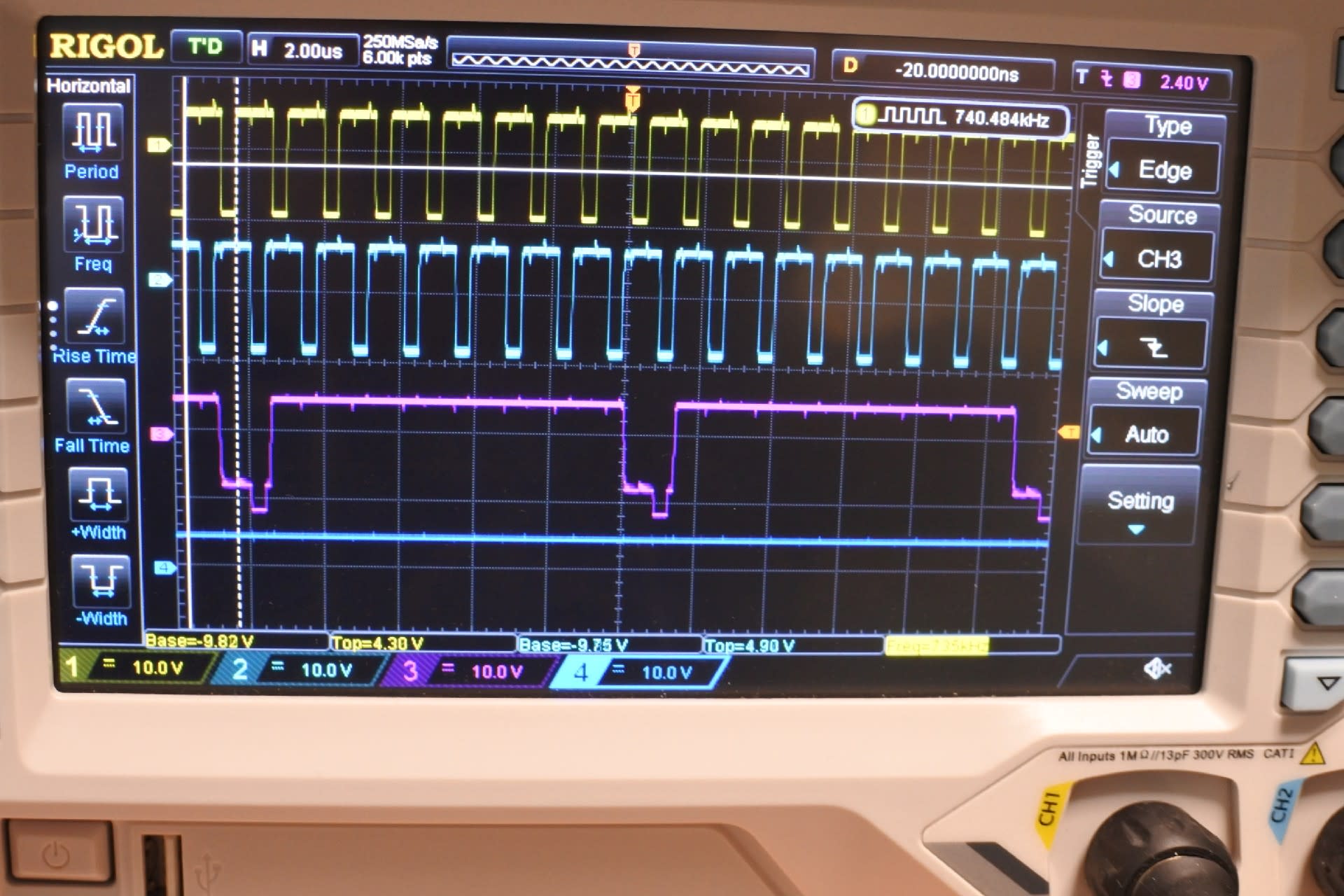

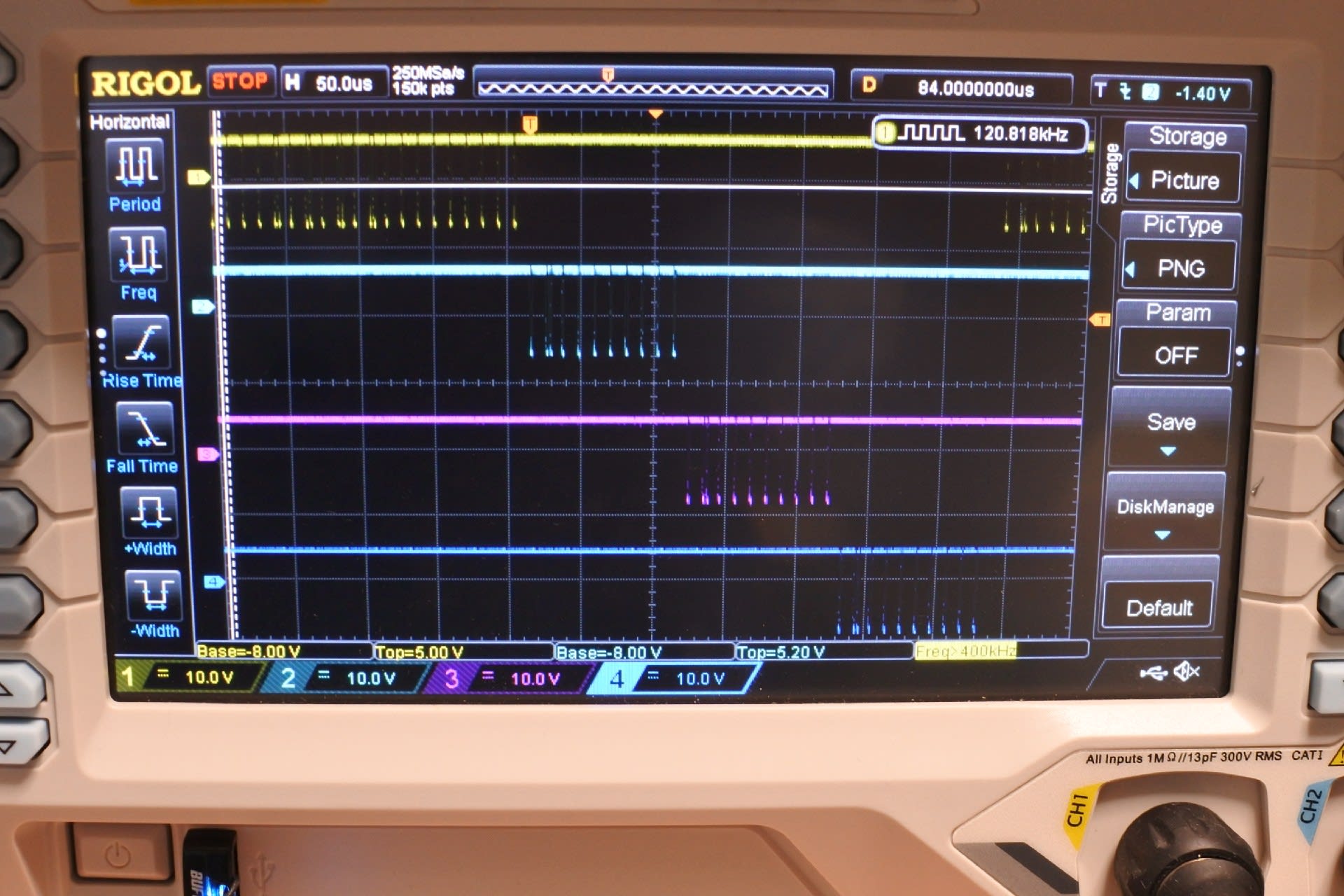

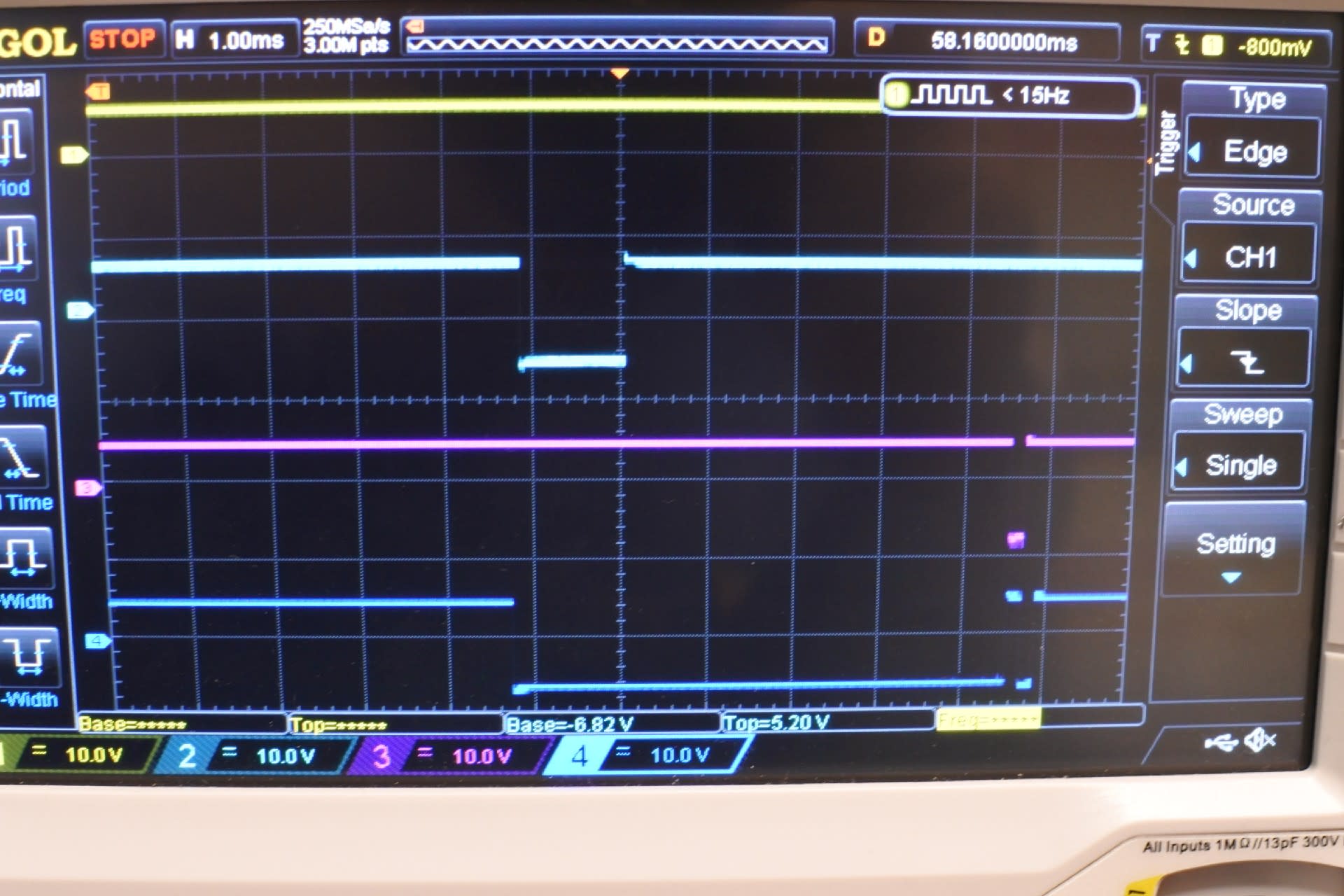

クロック周りを直したところ、ちゃんとSYNC信号が出ました!(上から、CLK1, CLK2, SYNC)

ちなみにこの評価ボード、LEDが点いたり、画面にメッセージが出たりはしません。

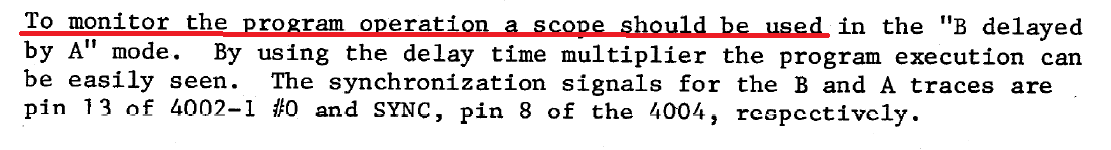

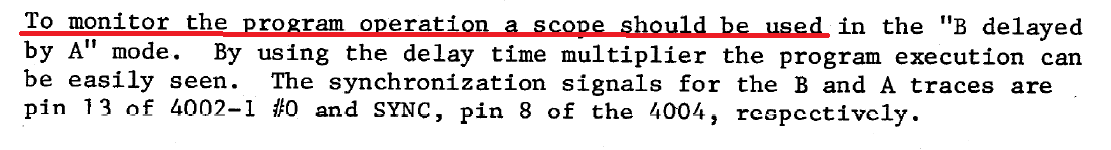

「プログラムの動作を見るにはオシロスコープを使え」と書いてあります。

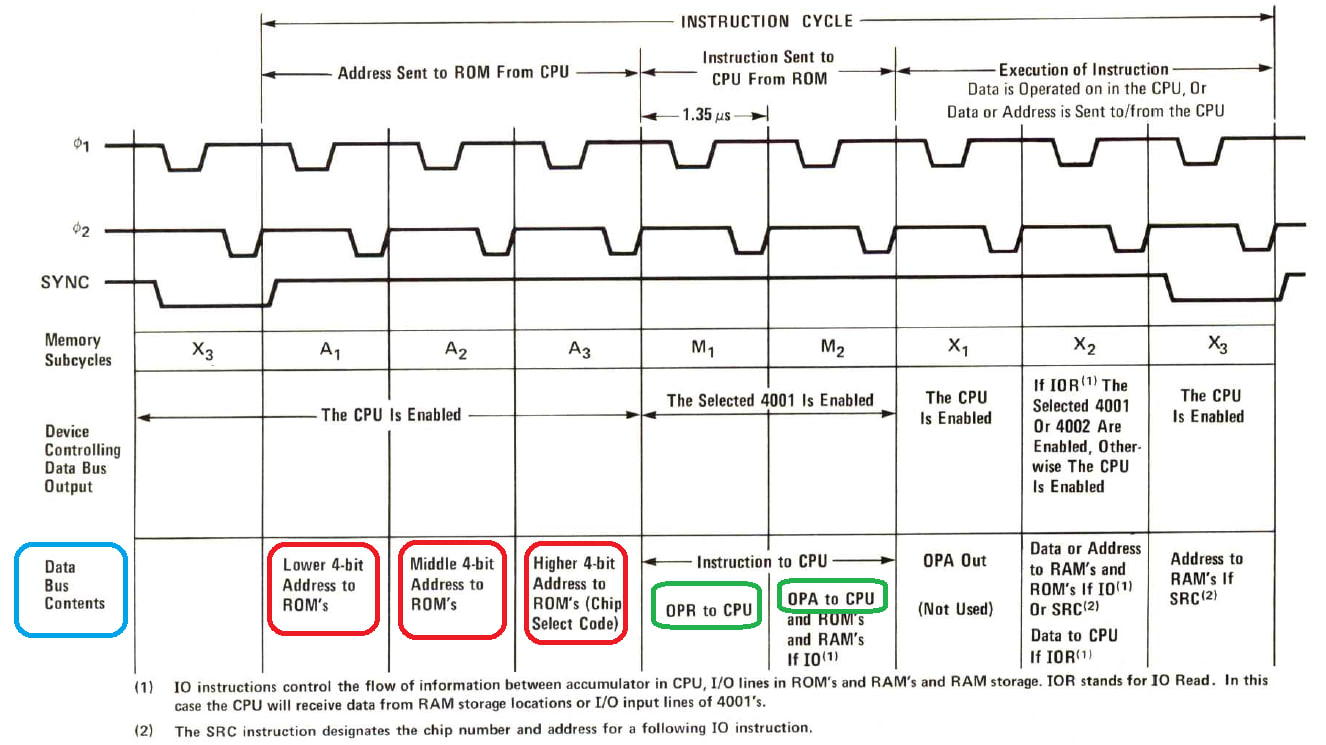

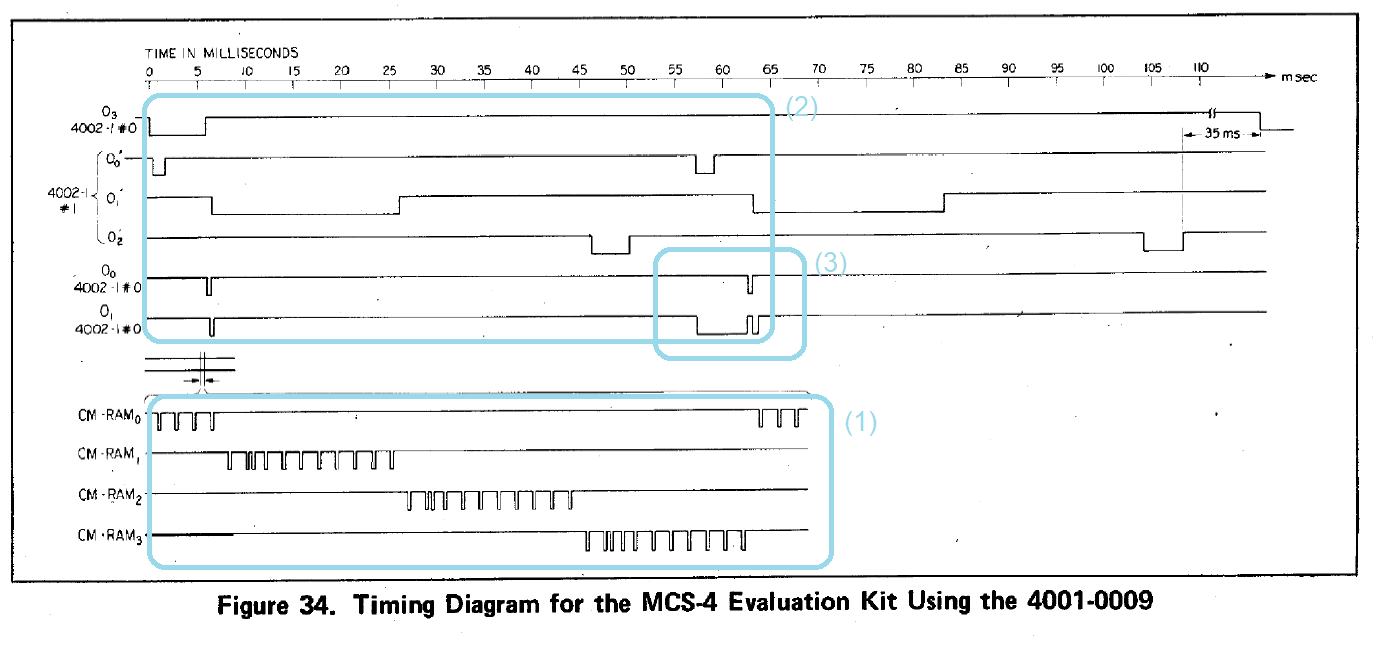

というわけで、信号を観測してみます。想定される信号は下記の通り。

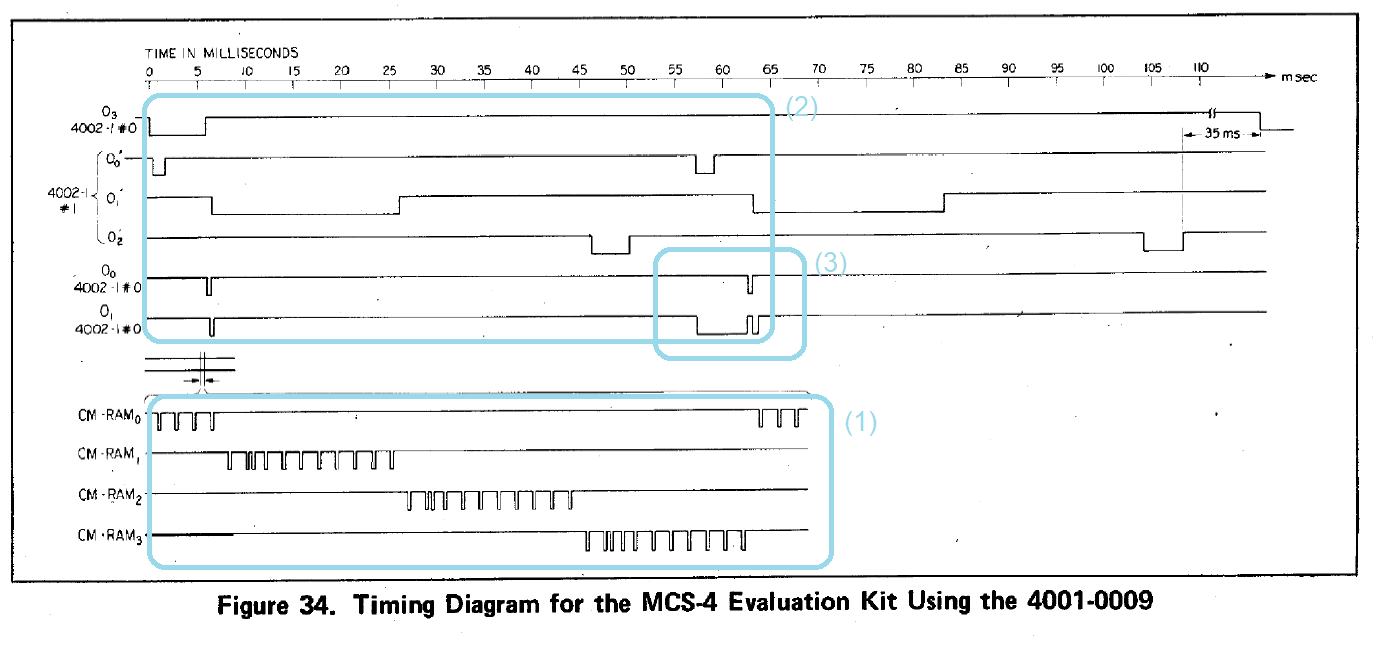

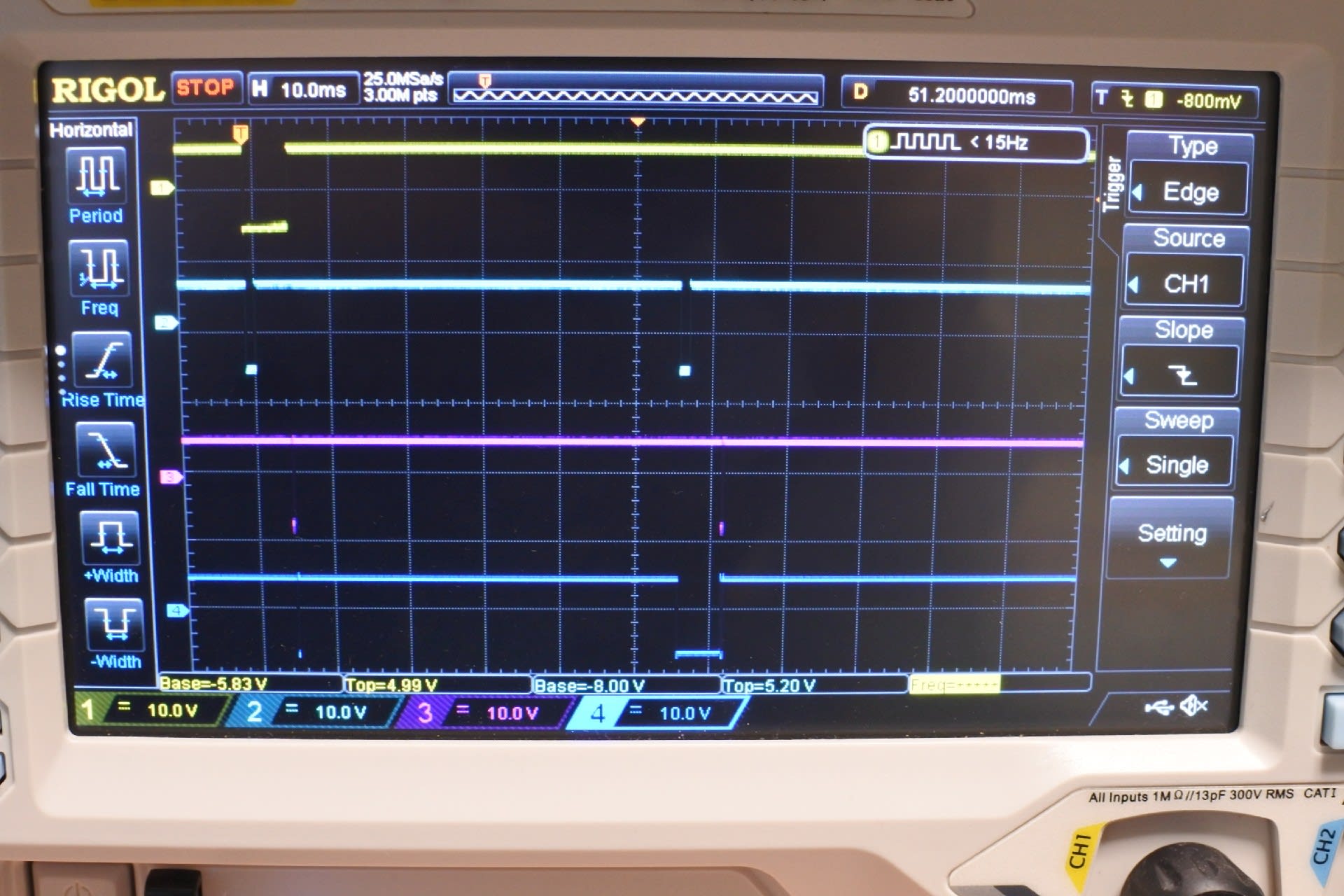

(1), (2), (3)がちゃんと見えました。

(1)

(2)

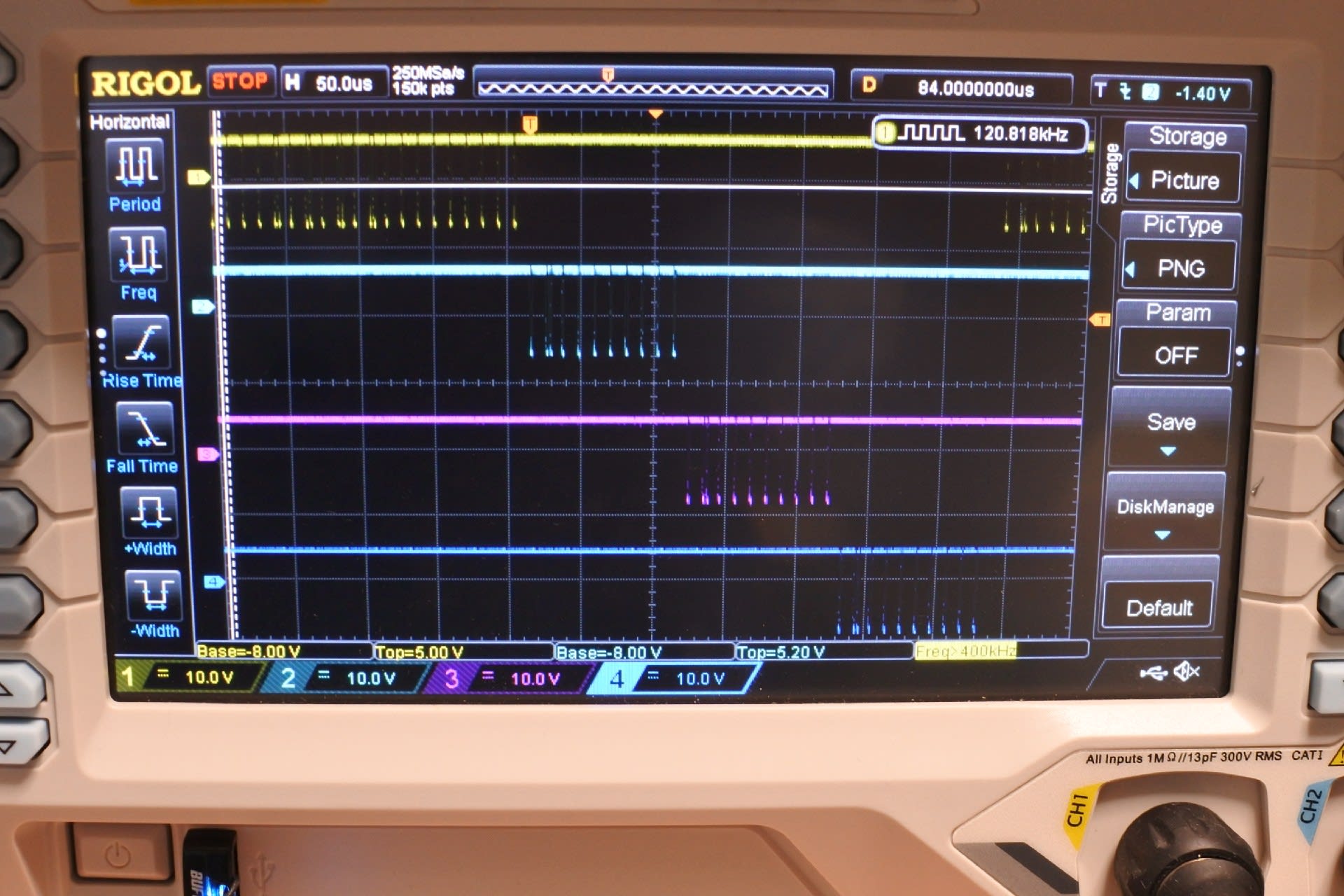

(3)

(3)

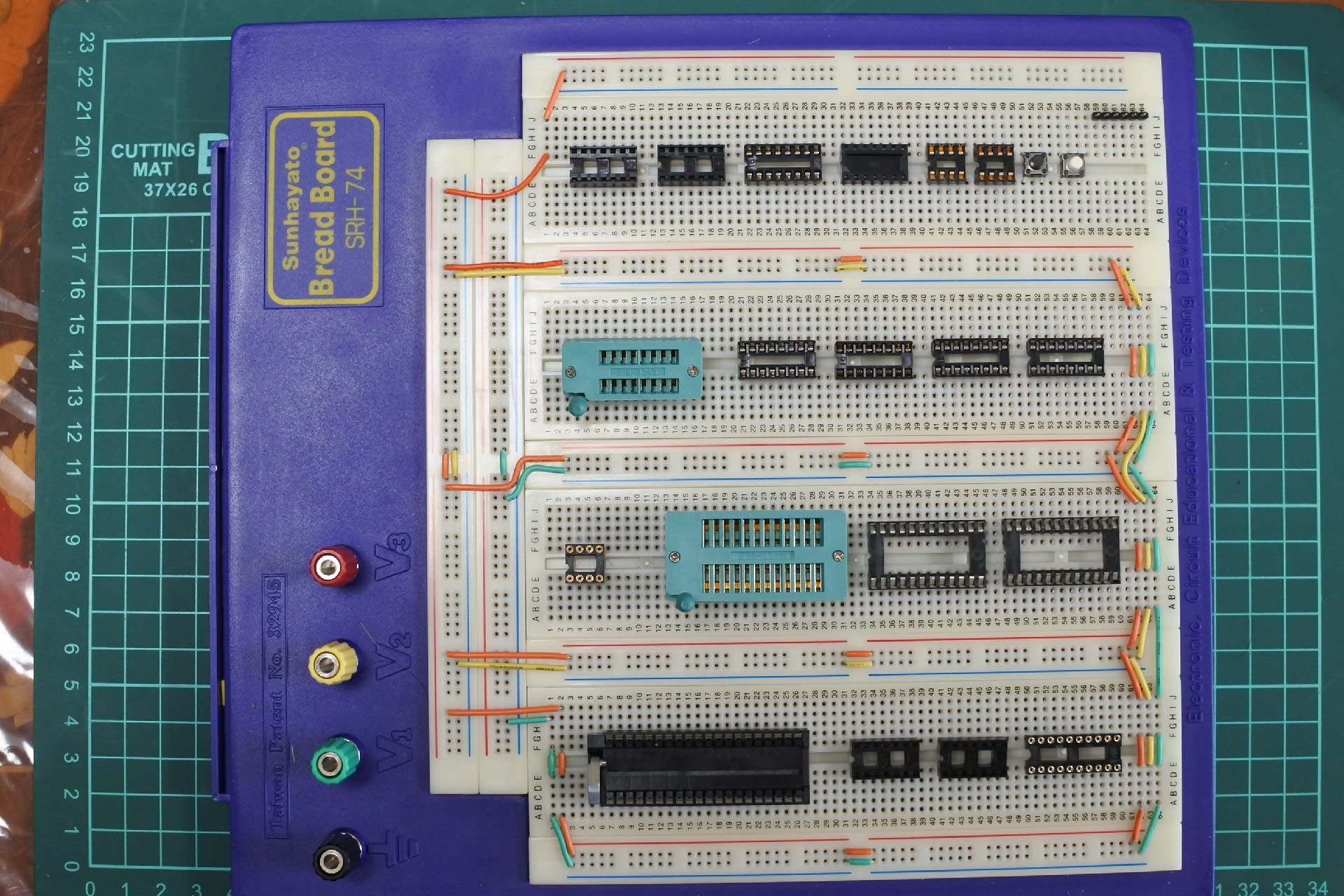

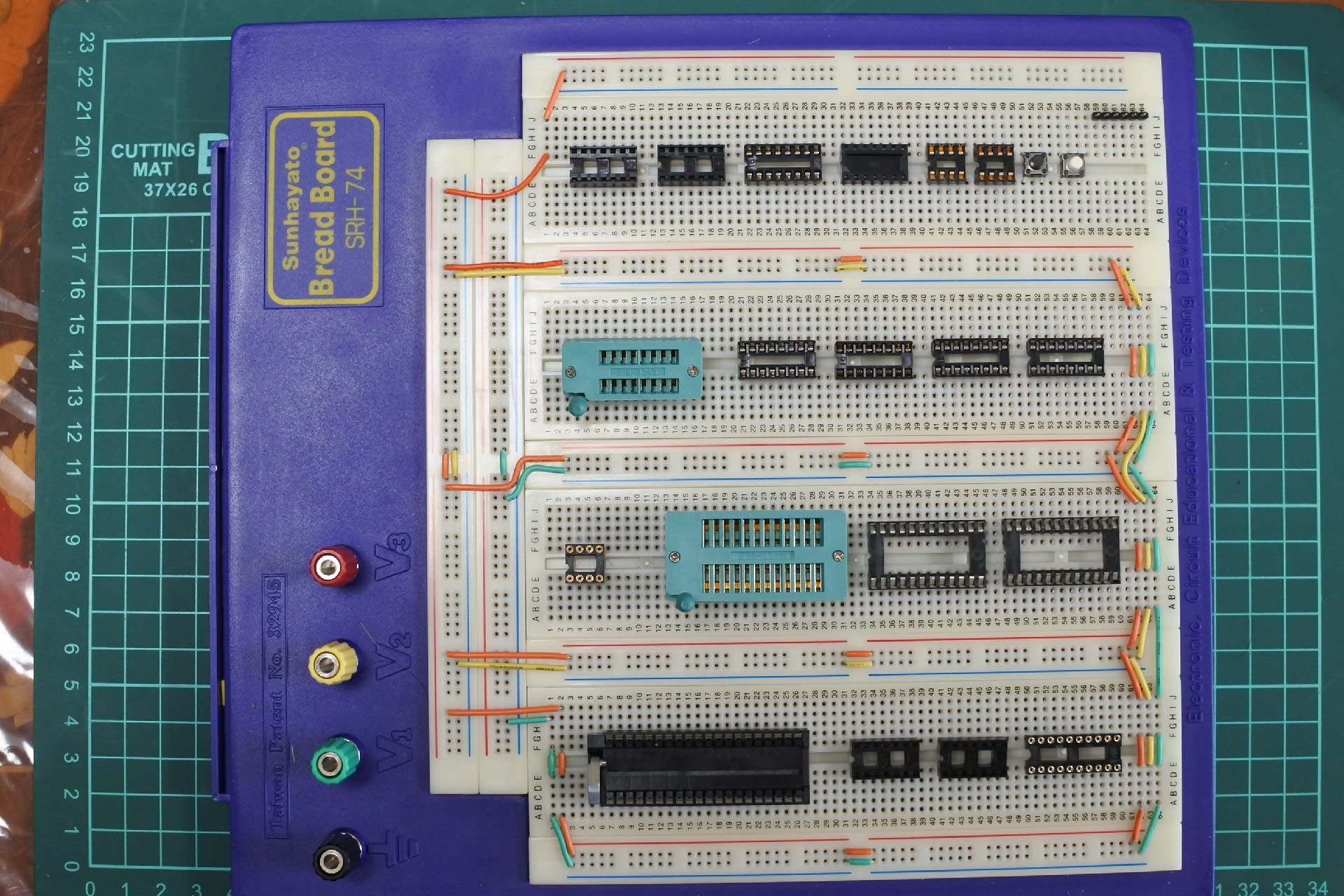

このボードではこれ以上やることはたぶん無いので、次はプログラムが書ける評価ボードを作ろうと思います。レイアウトはこんな感じを予定。

つづく。

どうして気がついたのか、というあたりからとりあえず順を追って書いてみます。

Lチカ(Intel 4004 (その4) Lチカの巻)の次は簡単なモニタプログラムやインタプリタ言語が動くボードを作りたいなと思って、回路図を引いたりレイアウトを考えたりしていたのですが、部品を注文して届くまでにやることが無くなったので、アセンブラについて調べたり、ユーザーズマニュアルを調べていました。

前回使ったディスアセンブラのところに、アセンブラとエミュレータ(INTEL 4004 SYSTEM EMULATOR)もあり、開発ツールに使えそうな感じ。エミュレータ用のサンプルプログラム(MCS-4 EVALUATION KIT USING THE 4001-0009)もあったので、ロードしてみると、2バイト目がリターン命令(BBL)です。

あれ?これはどこかで見たような・・・と思い、ROMのダンプリストとdiffをとってみたところ、なんと3バイト違うだけで残り253バイトは一致しています。

最初は、ROMリーダーが不完全でbit化けしてるんだろうなと思ったのですが、20が30はあるにしても、02が20、しかも2箇所はちょっと考えにくいです。

エミュレータのところにあった資料(MCS-4 Evaluation Kit using 4001-4009)にソースがあるので見てみると、

FINは1バイト命令なので次の254はおかしいです。エミュレータのアセンブルリストでもFE ???になっています。

プログラムの意味を考えても、これはROMのダンプのFIM(20)が正しいのでしょう。マニュアルの誤植だと思われます。

次に、20が02になっているところ。エミュレータでは20になっていますが、マニュアルでは2です。

これはエミュレータ側が間違っているようです。エミュレータの作者に連絡したいけど、連絡先が書いてないなあ。

ここまで調べてようやく、あれ?そういえば、このROMのパッケージに4001-0009って書いてあるよ!(最後の9がかすれてるけど)

ということに気がつきました。

ググってみてもマニュアル以外の情報にはヒットせず。これってもしかしてCPUの4004よりレアなパーツなのではないだろうか。

マニュアルの回路図を見ると非常にシンプル。しかも、トランジスタのフィードバック回路は省略可(The circuit for single pass/continuous can be omitted if only continuous operation is sought.)ということなので作ってみることにしました。(ちなみに私はアナログ回路はさっぱりわからないのでトランジスタの回路は敬遠しているのですが、たぶんこれってたぶん7404とか7407とかのバッファで代用できるよね。)

クロック回路が結構面倒なのでROMリーダーから流用しようかと思ったのですが、全部新しく作る方が見た目も良いので1日がかりでブレッドボードに組み立てました。で、電源を入れてみたのですが想定通りの波形は出ません。(そういう状態だと電源を入れていること自体がリスクなので写真を撮るのは省略しています。)

信号を見てみると、クロックはOK。しかし、4004が出力するはずのSYNC信号が出ていません。順に信号を確認したところ、RESET信号が出ていないことを発見。リセット信号を作る部分の配線ミスでした。

これでOKかと思って再度トライ。しかしまだSYNCが出ません。

うーん、4004と4001は動作確認済みだから、まだ動作確認してない4002が壊れていてSYNC端子に変な信号を出している可能性があるな!

と思って、Lチカボードで全チップの動作を確認したのですが全部正常。おかしいなあ。と思って回路図を確認したところ・・・

あれ?SYNC, CLK1, CLK2じゃなくて、CLK1, CLK2, SYNCなの?!

CLKの接続が間違っていて、CLK2(クロックドライバの出力, ドライブ力強い)をSYNC(4004の出力)に突っ込んでいました・・・

壊れなくて良かったあ。

教訓: 組んだ回路がおかしいときは部品よりも自分の配線を疑うべし。

クロック周りを直したところ、ちゃんとSYNC信号が出ました!(上から、CLK1, CLK2, SYNC)

ちなみにこの評価ボード、LEDが点いたり、画面にメッセージが出たりはしません。

「プログラムの動作を見るにはオシロスコープを使え」と書いてあります。

というわけで、信号を観測してみます。想定される信号は下記の通り。

(1), (2), (3)がちゃんと見えました。

(1)

(2)

(3)

(3)

このボードではこれ以上やることはたぶん無いので、次はプログラムが書ける評価ボードを作ろうと思います。レイアウトはこんな感じを予定。

つづく。