Z80(Z84C0020PEG)をオーバークロックして33MHzで動かすことに成功しましたので、とりあえず備忘録としてまとめておきます。

回路図やプログラム等一式はGitHubに置いてあります。

Tang Nano 20K用のGPIOを5Vトレラントにするアダプタを作ったのでその応用例としてZ80のメモリシステムを作ったというストーリーになっていますが、昔のCPU(Z80に限らず)のメモリシステムをTang Nanoに実装するために5Vインターフェースを作ったというのが正確なところです。

レベル変換用のICはSN74CB3T3245という長い名前のICを使用。レベル変換についていろいろググってたら見つかったこのページ(5V系・3.3V系信号レベル変換)で知りました。

データシートには「レベルシフタ搭載バススイッチ」とあります。5V→3.3Vはレベル変換しますが、基本的には「スイッチ」なので、3.3V→5Vは変換せずに3.3Vの信号がそのまま5V側に出力されます。5VTTLの閾値は1.5V,5VCMOSの閾値は2.5Vなので問題無く動作するということのようです。

レベル変換用ICにはSN74CB3T3245の他に、LBF0108、TXS0108、TXB0108というデバイス(いずれもTexas Instruments製)などもあり、TIのレベル変換関連の資料を見ると最近の資料にはSN74CB3T3245は載っておらず、LBF0108を勧めている感じもあったのですが、実物を入手していろいろ比較した結果、結局SN74CB3T3245が一番良さそうという結論に落ち着きました。

最初に作った変換基板にTangNano20Kを搭載したのがこれ。幅を間違えてしまっていました。

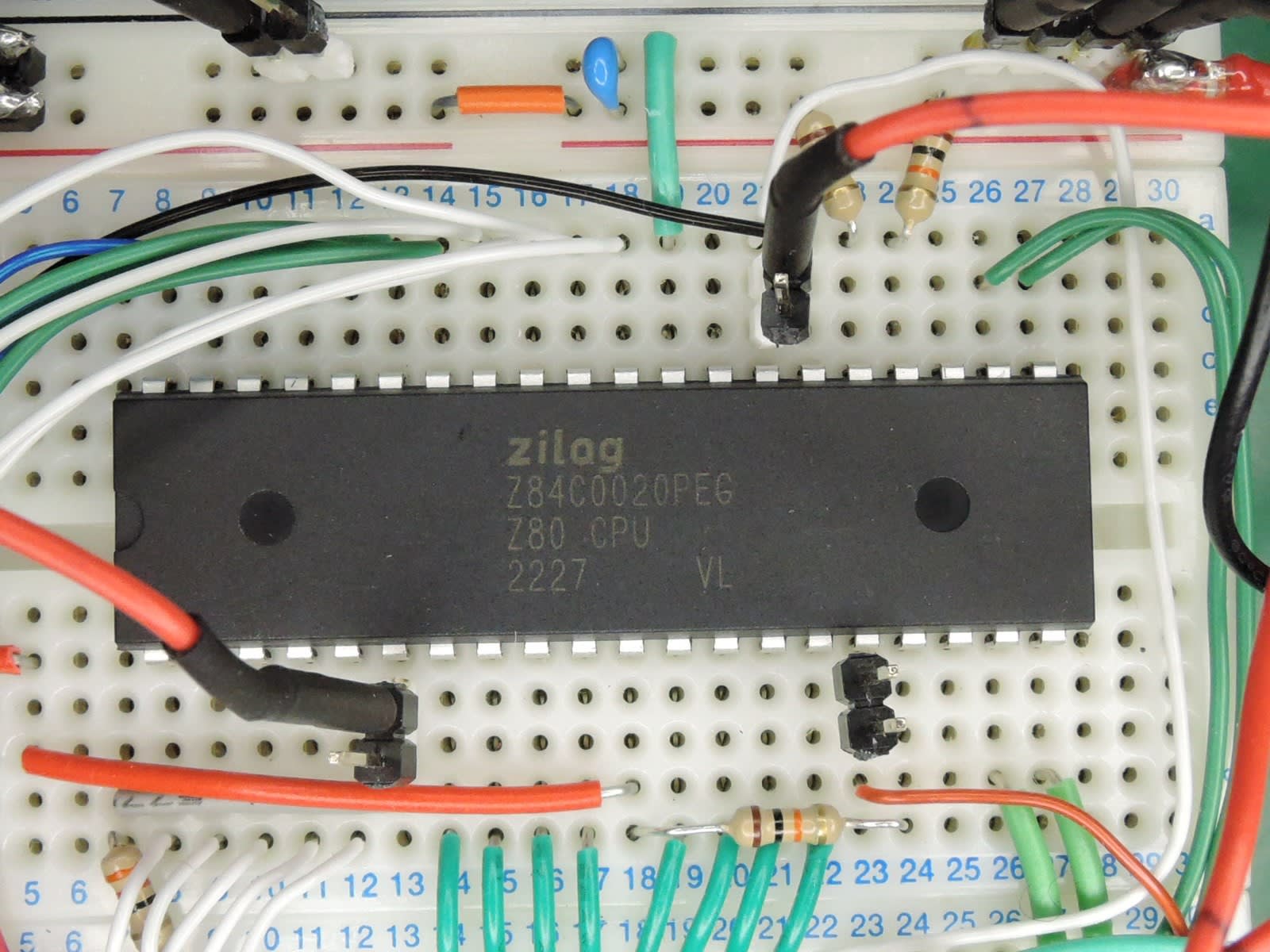

機能的には問題無いはずなのでとりあえずこれを使ってブレッドボードでZ80と接続。

なんとなく動いてるんだけど、メモリがちゃんと認識されてなかったりして不安定。

データシートを読み返していたらクロックはTTLレベルじゃだめでHレベルはVcc-0.6V必要ということを発見。

74AHCT04を使ってクロックを5Vまで引き上げたところわりと安定して動作するようになりました。

この雑な配線でも12MHzで動作。とはいえさすがにこの配線はダメだろうと思ってもう少し真面目に配線しなおしました。

そしたらブレッドボードで27MHzで動作してしまいました。ただちょっと不安定。ブレッドボードでは限界っぽいので基板の到着を待ちます。

基板が完成したので部品を載せ替え。

しかしおかしなことに27MHzでは動作してくれなくなってしまいました。20MHzでは動作するので回路に問題は無さそう。

メモリアクセスのタイミングの問題かなと思い、TangNano側のロジックを変更してみました。メモリはクロックに同期させる方が安定するだろうと思ってクロックエッジでMREQ_nやRD_n、WR_nを見て読み書きしていたのですが、(~MREQ_n & ~RD_n)や(~MREQ_n &~WR_n)のエッジで(クロックとは非同期で)読み書きするように変更したところ問題解決。変なことするよりメモリ本来の動作に忠実に実装する方が良かったようです。

安定して動くようになったのでいよいよオーバークロックの実験。Z84C0020PEGはデータシート上のスペックはDC~20MHzです。

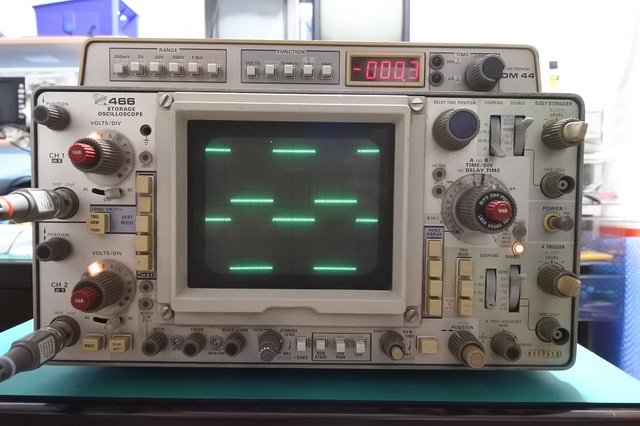

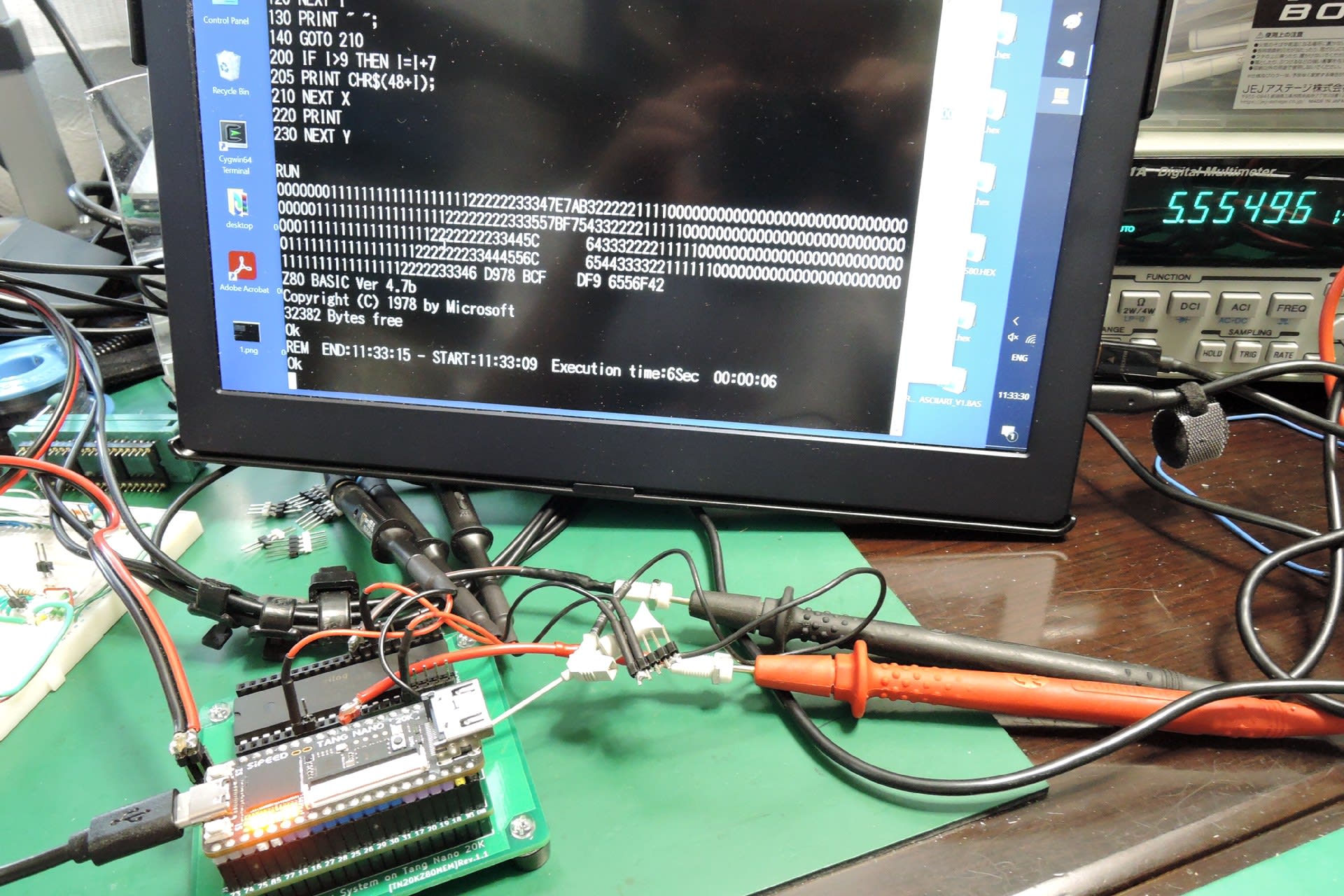

まずは27MHz。電源はTangNano経由のUSB給電という適当な設定。これでもASCIIART.BASは無事完走しました。

データシートには、

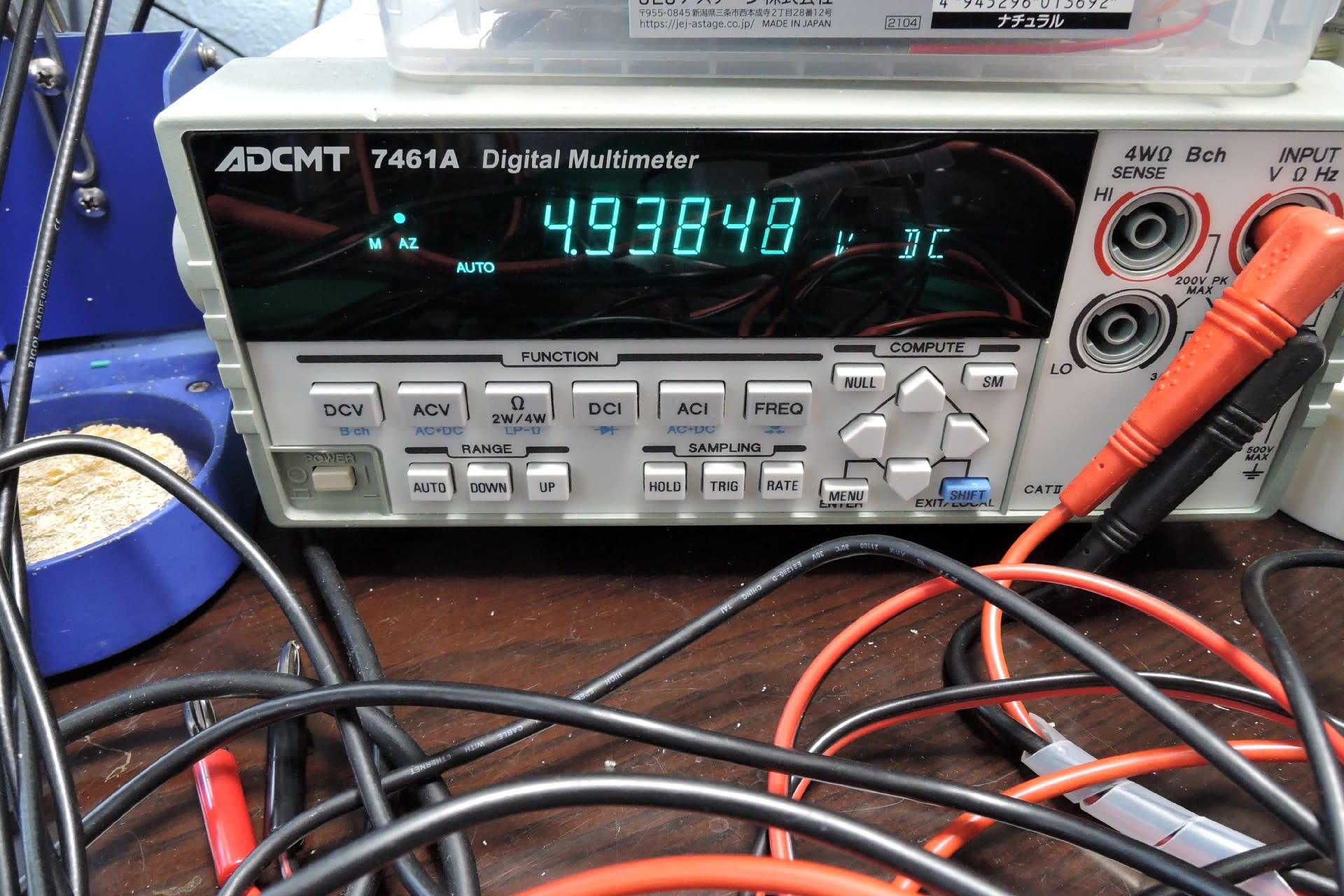

とありますので、Vccの電圧は5.5V程度までなら安心して上げられます。

試してみたところ、クロック31.5MHzでVcc=5.55Vで途中で暴走。Vcc=5.6Vだとわりと安定して動作している感じでした。

31.5MHzというのはちょっとキリが悪いので、33MHzに挑戦してみることにしました。データシートを見ると、絶対最大定格は7.0Vです。

そういうことならVcc=6.0Vは大丈夫でしょう。試してみたところあっさり動作しました。

動画はこちら。

以上、Z84C0020PEGをVcc=6.0V, Clock=33MHzで動かしてASCIIART.BASを36秒で完走したお話でした。