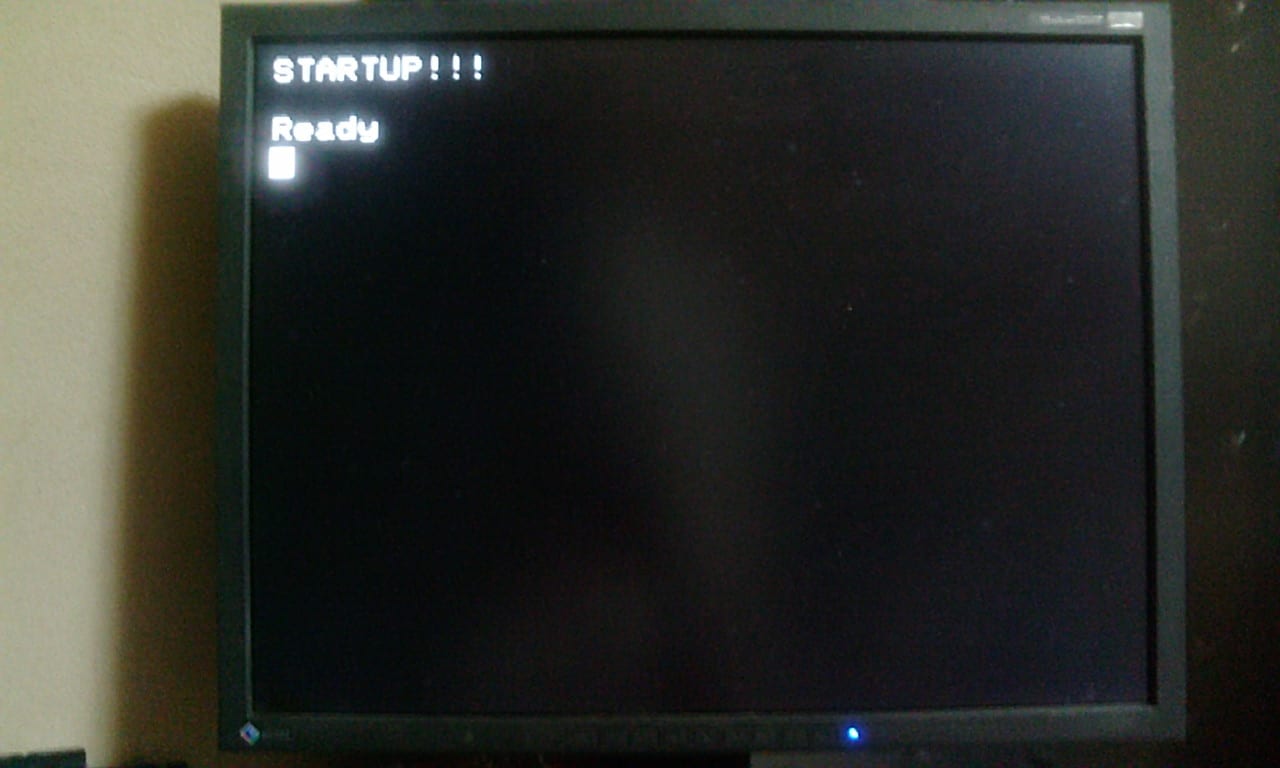

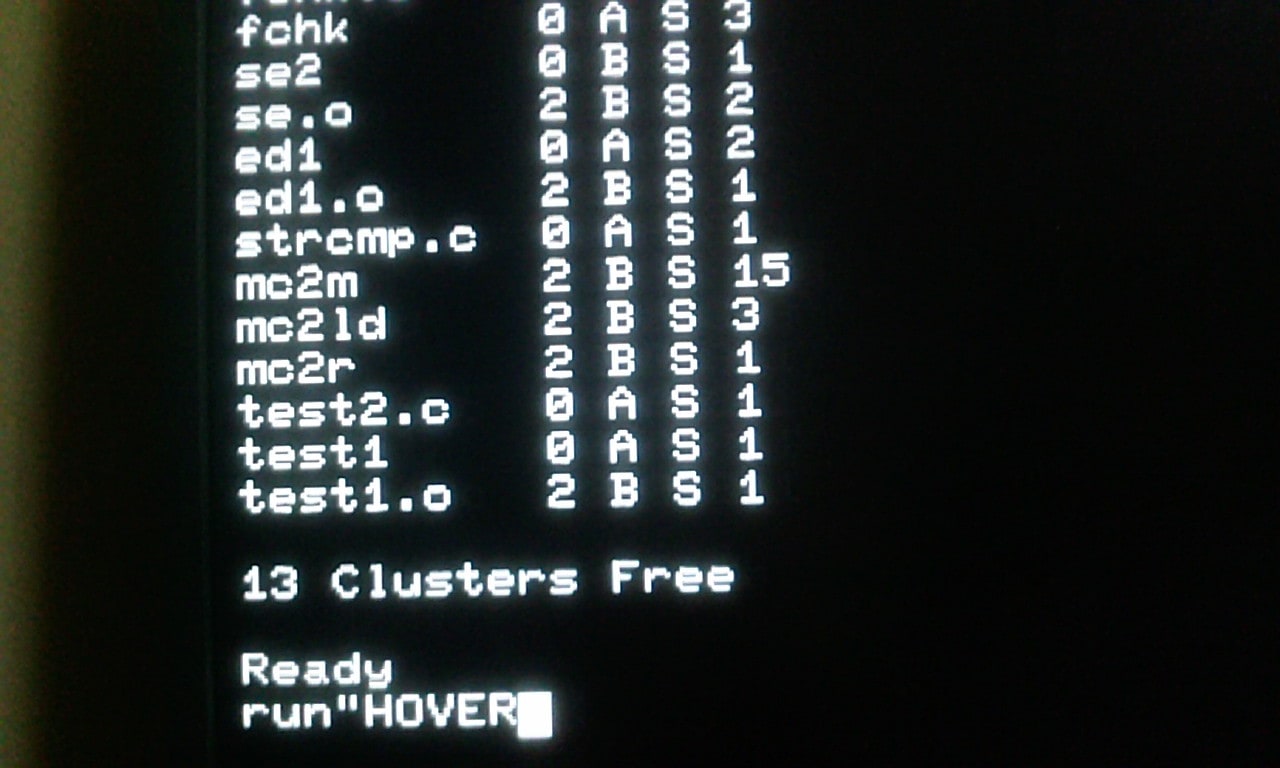

一つ前の記事のFM-7のプリンタポート接続SPIシリアルフラッシュメモリ用

ブートROMのソースです。アセンブラはedas20を使用しました。

テスト用のコードがいろいろついてますが、$2E00~$2FFFが

ブートROM部分です。ブートROMのプログラム領域480バイトを

ほぼ使い切っているため、機能追加はわりと厳しそうです。

;Copyright (C) 2018 pakapoo http://blog.goo.ne.jp/purupoo. All rights reserved.

; パラレルポート セツゾク ノ シリアル

; フラッシュメモリ カラ BOOT スル BOOT ROM

; EBIOS6.A ヲ カイゾウ

;

; $FD00 BIT6 OUT STRB SCLK

; $FD01 BIT2 OUT D2 SS1

; $FD01 BIT1 OUT D1 SS0

; $FD01 BIT0 OUT D0 MO

; $FD02 BIT3 IN PE MI

;

;

ORG $3000

;

; TEST MAIN

;

LDX #RCB

JSR READ

RTS

;

ORG $3010

LDX #RCB

JSR WRITE

RTS

;

ORG $3020

LDX #RCB

JSR [$FBFA]

ANDA #$3F

;

RTS

;

;

ORG $3030

LDX #$3080

LBSR UNSEL

LDA #$9F

LBSR SPI

LDA SPIIN

STA ,X+

LDA #$00

LBSR SPI

LDA SPIIN

STA ,X+

LDA #$00

LBSR SPI

LDA SPIIN

STA ,X+

RTS

;

;

ORG $3060

LDX #$3100

LBSR UNSEL

LDA #$77

LBSR SPI

CLRA

LBSR SPI

LBSR SPI

LBSR SPI

L30601:EQU *

LBSR SPI

LDB SPIIN

STB ,X+

CMPX #$3180

BNE L30601

RTS

;

;

ORG $3090

LDA #100

L30901:PSHS A

JSR $3000

PULS A

DECA

BNE L30901

RTS

;

;

;

;

;

ORG $30C0

;

RCB:FCB 10

RCBST:FCB 0

RCBADR:FDB $3100

RCBTRK:FCB 0

RCBSCT:FCB 1

RCBSID:FCB 0

RCBUNT:FCB 0

TSTST:FDB 0

;

;

ORG $2E00

;

SPICD:EQU $FD08

SPIDT:EQU $FD09

PRT0:EQU $FD00

PRT1:EQU $FD01

PRT2:EQU $FD02

;

STRD:EQU $D7

FTOB:EQU $53

B1RD:EQU $D1

B1WT:EQU $84

BTOF:EQU $83

APRW:EQU $58

;

;

SCOFST:EQU 128

;

;

;

SS:EQU $FC29

SPIIN:EQU $FC2A

PNUM:EQU $FC2B

PNUML:EQU $FC2C

PAGE_H:EQU $FC2D

PAGE_L:EQU $FC2E

;

; BOOT

;

BRA BOOTL1

CLRA

NOP

RTS

LBRA WRITE

LBRA READ

BOOTL1:EQU *

CLR PRT0

DECA

STA PRT1

LDA #$FD

TFR A,DP

LDS #$FC7F

LBSR UNSEL

LDB <$FD04

BITB #$02

BNE BOOTL2

LDX $FBFC

BRA BOOTL3

BOOTL2:EQU *

;

;

LDA #$31

LBSR PUTC

LEAX BTRCB,PCR

LBSR READ

LDA #$32

LBSR PUTC

;

LDX #$0100

CLRA

TFR A,DP

JMP $0100

; BRA BOOTL3

;

;

BOOTL4:EQU *

LDX $FBFE

;

;

BOOTL3:EQU *

CLRA

;

COMINI:EQU *

TFR A,DP

; JMP ,X

;

;

LDU #$FD06

BSR COMIN1

LDU #$FD24

LDA #$04

COMIN2:BSR COMIN1

LEAU 2,U

DECA

BNE COMIN2

JMP ,X

;

COMIN1:EQU *

CLR 1,U

CLR 1,U

CLR 1,U

LDB #$40

STB 1,U

RTS

;

;

;

;

BTRCB:FCB $0A,0,$01,$00,0,1,0,0

;

;

; DRIVE TABLE

DRVTBL:FCB 4,4,2,2

;

;

UNSEL:EQU *

BSR CLKLO

PSHS A

LDA #$FF

STA PRT1

PULS A

RTS

;

;

CLKHI:EQU *

PSHS A

LDA #$40

CLKHI1:STA PRT0

PULS A

BSR WAIT

RTS

;

WAIT:EQU *

; PSHS A

; LDA #1

;WAIT1: DECA

; BNE WAIT1

; PULS A

RTS

;

CLKLO:EQU *

PSHS A

CLRA

BRA CLKHI1

;

;

SPIBIT:EQU *

PSHS B

LDB SS

ROLA

BCC SPIB1

ORB #$01

SPIB1:EQU *

STB PRT1

BSR CLKHI

PSHS A,B

LDB SPIIN

LDA PRT2

RORA

RORA

RORA

RORA

ROLB

STB SPIIN

PULS A,B

BSR CLKLO

PULS B

RTS

;

SPI:EQU *

BSR SPIBIT

BSR SPIBIT

BSR SPIBIT

BSR SPIBIT

BSR SPIBIT

BSR SPIBIT

BSR SPIBIT

BSR SPIBIT

RTS

;

;

;

;

SPIWT:EQU *

RTS

;

SSSEL:EQU *

BSR UNSEL

PSHS A,B

LDA 7,X

LEAY DRVTBL,PCR

LEAY A,Y

LDA ,Y

STA SS

PULS A,B

RTS

;

;

RDYCHK:EQU *

BSR SSSEL

LDA #STRD

BSR SPI

CLRA

BSR SPI

CLRA

BSR SPI

LDA SPIIN

LBSR UNSEL

RTS

;

;

; 4 BYTE COMMAND

;

CMD4:EQU *

BSR SSSEL

;

LBSR SPI

;

;

TST1:EQU *

LDB 5,X

DECB

LDY #PNUM

CLR 0,Y

STB 1,Y

;

LDB 6,X

LDA #16

MUL

ADDD ,Y

STD ,Y

;

LDB 4,X

LDA #32

MUL

ADDD ,Y

;

ADDD #SCOFST

;

PSHS A,B

LDA 7,X

CMPA #0

BEQ CMDL1

CMPA #2

BEQ CMDL1

PULS A,B

ADDD #1280

BRA CMDL2

CMDL1:EQU *

PULS A,B

;

;

CMDL2:EQU *

LSLB

ROLA

;

LSLB

ROLA

;

ANDA #$3F

;

PSHS B

STA PAGE_H

LBSR SPI

PULS A

STA PAGE_L

LBSR SPI

;

CLRA

LBSR SPI

;

;

LBSR UNSEL

RTS

;

;

;PNUM: FCB 0

;PNUML:FCB 0

;

;

CMD:EQU *

LBSR SSSEL

;

LBSR SPI

CLRA

LBSR SPI

CLRA

LBSR SPI

CLRA

LBSR SPI

;

RTS

;

;

;

READ:EQU *

LDA #FTOB

BSR CMD4

READL2:LBSR RDYCHK

CMPA #$AC

BNE READL2

LDA #B1RD

BSR CMD

CLRB

LDY 2,X

READL1:EQU *

CLRA

LBSR SPI

LDA SPIIN

STA ,Y+

DECB

BNE READL1

LBSR UNSEL

CLRA

RTS

;

;

WRITE:EQU *

LDA #B1WT

BSR CMD

CLRB

LDY 2,X

WTLP1:EQU *

LDA ,Y+

LBSR SPI

;

DECB

BNE WTLP1

;

LBSR UNSEL

;

LDA #BTOF

LBSR CMD4

WTLP2:EQU *

LBSR RDYCHK

CMPA #$AC

BNE WTLP2

;

LDA #APRW

LBSR CMD4

WTLP3:EQU *

LBSR RDYCHK

CMPA #$AC

BNE WTLP3

;

LBSR UNSEL

CLRA

RTS

ENDADR:EQU *

;

;

PUTC:EQU *

PSHS A

LEAX ,S

LDD #1

BSR PUTS

PULS A

RTS

;

;

PUTS:EQU *

TFR X,Y

LEAS -6,S

LEAX ,S

PSHS A,B

LDA #20

STA ,X

CLR 1,X

STY 2,X

PULS A,B

STD 4,X

JSR $F17D

LEAS 6,S

RTS

;

LDA #$31

BSR PUTC

RTS

;

;

;

; INTERRUPT VECTOR

;

ORG $2FF0

FCB $FF,$FF,$FF,$FF,$FF,$FF,$FF,$FF

FCB $FF,$FF,$FF,$FF,$FF,$FF,$FE,$00