CPUにおける「リセット:RESET」回路とは、どんな役割があるんでしょう?

それは、大雑把に云って2つあります。 (本当はもう1つある)

① 最初に 電源が投入された時、Vcc(+5V)が安定するのと、かつ クロックの信号が安定して供給されるのを待つための時間調整。

→ 要は電源を入れてもしばらくの間 RESET=Lowを保ち、

周りの他の回路が安定してから やわらCPUが動き出す。

② プログラムが走っていようと、暴走していようと、RESET信号が入力されたら、それこそCPUが リセットされ、アドレス0番地から実行し直される。

この2点 です。

電源が投入されても しばらくは Lowに保たれる回路の 最も簡単な構成は、R(抵抗)を使って C(コンデンサ)に電気をゆっくり貯める ↓ こんな回路でしょう。

Vccは 5Vとし、仮に抵抗を1KΩ、コンデンサを 10uF とします(計算し易いように!)

では、あなたは この時 (緑の点の電圧が) Lowに保たれる 時間 を 自分で計算できますか?

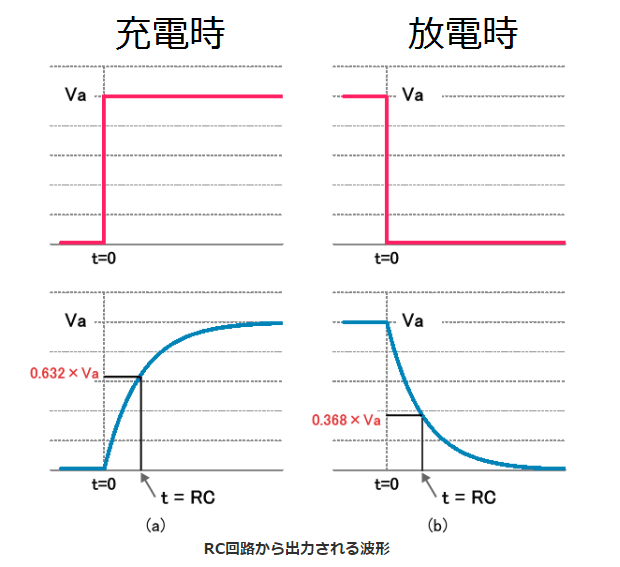

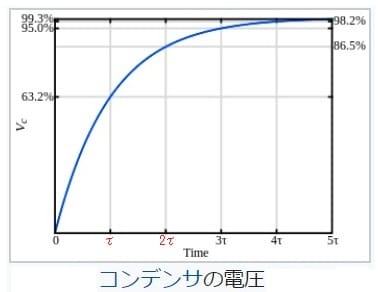

この回路が(コンデンサが)「充電される時」と「放電される時」の電圧波形は、↓ こんな 感じになるはずです。

上の赤いのがVcc(5V)で、下の青いのが コンデンサのプラス側の電圧です。 電源電圧に対して その63.2%まで充電される時の時定数を τ (タウ) と言って、トランジスタの場合 0.69を使うのが普通でした。

つまり、

T = τ・R・C

が時間Tを計算する時の計算式で τ (タウ) =0.69 で計算すると だいたい合っていたのです。 T=時間、R=抵抗値、C=コンデンサ容量

なんか難しくて分かりづらいですよね? それと単位は?何でしょう??

具体例をあげてみます。

抵抗Rの単位をKΩ ・・・ つまり 1KΩなら そのまま 1

コンデンサC単位をuF (=マイクロ・ファラッド) ・・・ 10uFなら 10

とすると、

T = 0.69 x 1 x 10

=6.9

この時の Tの単位が mS(ミリ秒)とするのが 一番 分かり易いでしょう。

ーーーーー

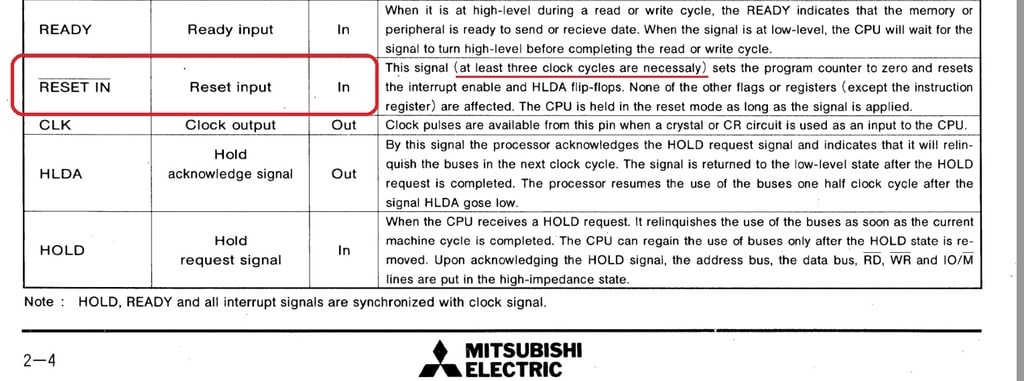

では、肝心の 8085AのCPUの場合、最低でどの位の時間(長さ)Lowにしておかないといけないのでしょう?

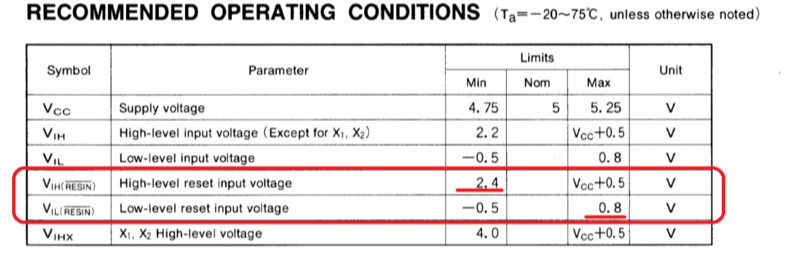

三菱の8085A のデータシート ↓ を見ると、

at least 少なくとも 3倍のクロック・サイクル時間は必要・・・となっています。 で、「1クロック・サイクル」って何mSなの? となりますが、

次の資料 ↓で、

短くとも 320uS= 0.32mS、長くとも 2mSとありますので、長い方を取れば

2mS x 3倍 = 6mS

(短い方だと 0.32x3=0.96 =約1mS。 これ以下のLowパルスだと リセットされないのか?)

本家Intelのデータシートにこんな記述を見つけました。

電源Vccが最低動作可能な電圧に達してから、↑ 少なくとも10mSは Lowに保たなければいけない。

ちなみに、電圧の63.2%まで充電される時を 1τ(タウ) とすると、

電圧の86.5%まで充電される時を 2τ(タウ) と言い、時間は倍になります。

充電が進むにつれて、どんどん充電速度が落ちて行き、充電されにくくなるんですね?

電源電圧5Vとして、その1τ(タウ) の 電圧で、本当に正しいのでしょうか?

5V x 0.632 = 3.16V

C-MOSレベルなら良いのでしょうが、TTLではもっと早く Hi と判断されてしまうはずです。 実際、こんな ↓ データがありました。

VIH(リセット入力端子にかぎり)= 最低でも 2.4V

VIL(リセット入力端子にかぎり)= 最高でも 0.8V

つまり、通常のTTLの入力レベル 2.0Vよりは 少し高い・・・でも、最低でも2.4Vを超えたら RESET信号は終了した と 判断されてしまうんですね?

要するに このRCでは 6.9mSよりもっと 短く判断されてしまうんです!

そこで、抵抗を 3倍 に 増やして余裕を持たせてみました。↓ R1 が 1K⇒3KΩ

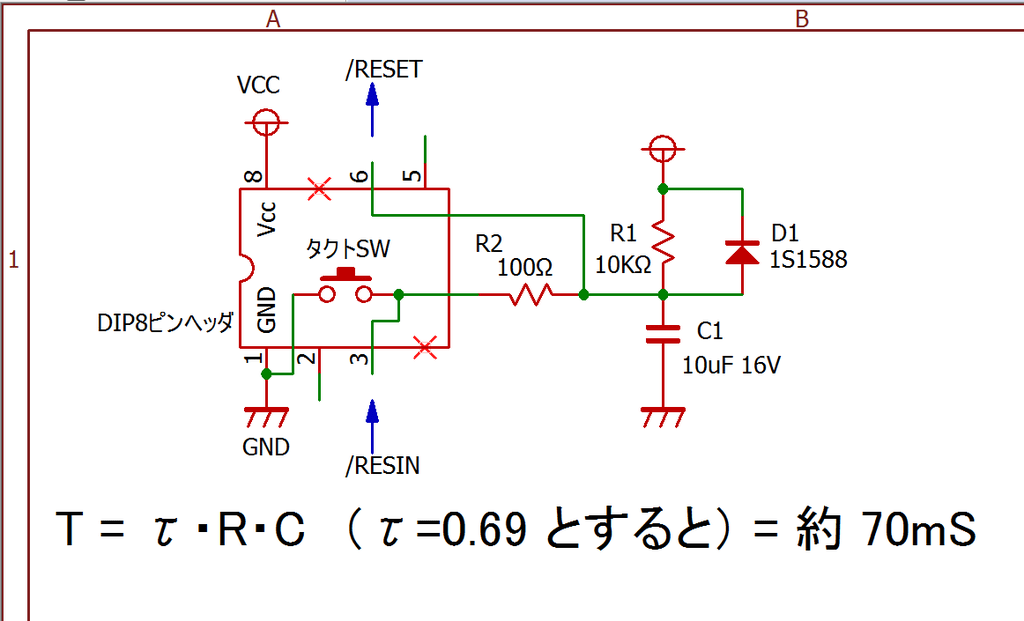

いっそのこと 10KΩ くらいでも良いでしょう (T = 約70mS)

D1のダイオードは、放電が速くなるように付けたもので、100Ωはコンデンサショートの時の保護です。 (0.8V 以下まで落ちれば良いので)

ーーー

ここで、回路設計に慣れている人の中には、

コンデンサが ゆっくり電圧があがっていくのだから、(HC14のような)ヒステリシス回路を入れないと心配だ! っと思う人もいるでしょう。

Hi と Lowの切り替わりの ギリギリの所で RESET信号が 「Hiと認識」「Lowと認識」を 激しく繰り返すのでは? と。

それを防ぐために おそらく ↓ こんな回路を設計しがち。

でも、おそらく こんな ヒステリシス内臓のインバイータ(14)を 2個も追加しなくとも大丈夫です。 (無駄なICは入れない! いつもの「習慣」だけで設計しない!!)

8085Aの RESET入力端子は、(最低でも 0.25V 差のある)ヒステリシス特性のある シュミット・トリガ回路(STの部分)を内蔵しています。 安全のため(0.6mA以上流さないと電圧が下がらないように)3KΩ相当のプルアップも内蔵されているようですね?

ーーー

さて、こういった RCによる時間の計算が面倒だ!という人には、インターネット上で簡単に時間計算ができるサイトがあります。

最初の単純な例: 1KΩ、10μF で やってみると

このサイトでは Min 7.6mS (~ 12.6mS)だったり、

また別のサイトでは、

10mSだったりします。 ここも ↓

実際はこれより短く判定されるので、余裕をもって長めにしておいた方が安全です。 そして こんな RC回路では まったく正確な時間は作れず、部品のバラツキ、誤差の方が大きいのです。 そんな認識でいてください。

ちなみに、TK-85 では、

R=10KΩ、C=22μF

他の SBC-8085 では、

R=47KΩ、C=10μF

でした。

(どのくらいの時間になるか ネットで計算してみてください)

さらに、

本家 Intelにデータシートには、具体的なリセット回路が載っていました。

R=75KΩ、C=1μF

これだと 約50mS のリセット時間となります。

これを そのまま真似しても良いのですが、75KΩ は手に入りにくいので 考えた末、↓ 二転三転しましたが、最終的に こんな値に落ち着きました。

R=10KΩ、C=10μF

これで 約70mS のリセット時間となります。

これなら部品も入手しやすいし、

70mSもあれば時間的にもかなり余裕があるはずです。