自作AVRコアにまだバグが残ってたよ。

原因掴むのにえらく時間が掛かった、最初はタイミングで化けたのかと思ってたので

VDPとの通信周りをずっと疑っていたんだけど、命令デコードのバグだったw

タイプミスでゼロが一個足りないだけだったんだけど、何故かずっと見過ごされてた。

これでようやくVDP側に抱かせたCPUによってSDカードからCGデータを

VDPのCGRAMエリアに展開できるようになる。

CG展開以外普段は暇だろうからサウンドもドライブでもさせるかな。

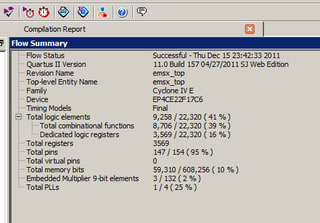

内部CPUからVDPをアクセス 着々と融合中

内包したCPUのROM容量が少ないので別途SDカードをアクセスするプログラムをしないと

画像等のデータが扱えない

■15日

SDからではなくとりあえずコンフィグROMから画像をロード なんかシュールw

色の再現性を良くするためにインターレースにしたんだけど、

垂直同期付近の等価パルスを入れていないので画面上部がブレちゃってますね。

負荷メーターが重いのは、内部通信をSPIではなくポート経由でソフト的に行ってるから、

オシロがあれば一発なんだけど、ソフト実装してポートをLEDで眺めてステップ実行という

貧弱な開発環境w

スプライト機能だけでなくGDCのようなラインや円の描画機能も加えようかな。

原因掴むのにえらく時間が掛かった、最初はタイミングで化けたのかと思ってたので

VDPとの通信周りをずっと疑っていたんだけど、命令デコードのバグだったw

タイプミスでゼロが一個足りないだけだったんだけど、何故かずっと見過ごされてた。

これでようやくVDP側に抱かせたCPUによってSDカードからCGデータを

VDPのCGRAMエリアに展開できるようになる。

CG展開以外普段は暇だろうからサウンドもドライブでもさせるかな。

内部CPUからVDPをアクセス 着々と融合中

内包したCPUのROM容量が少ないので別途SDカードをアクセスするプログラムをしないと

画像等のデータが扱えない

■15日

SDからではなくとりあえずコンフィグROMから画像をロード なんかシュールw

色の再現性を良くするためにインターレースにしたんだけど、

垂直同期付近の等価パルスを入れていないので画面上部がブレちゃってますね。

負荷メーターが重いのは、内部通信をSPIではなくポート経由でソフト的に行ってるから、

オシロがあれば一発なんだけど、ソフト実装してポートをLEDで眺めてステップ実行という

貧弱な開発環境w

スプライト機能だけでなくGDCのようなラインや円の描画機能も加えようかな。