以前SBC1802を作成したが、BASICだけでは面白くない。有り難いことに、インターネット上に関連ソフトが公開されている。そこでJR2XZYさんの記事(https://jr2xzy.blogspot.com/search/label/SBC1802)を参考にいくつかダウンロードして動かしてみた。

Membership Cardは前半32KBがRAM、後半32KBがROM。SBC1802は前半32KBがROMで、後半32KBがRAMとなっておりソフトにより動くものと動かないものがある。

MCBASIC3(SBC1802付属)

0番地ROM想定

baud rate 9600〜16800bps

入力はEF3使用

モニタ

0番地ROM想定の http://www.sunrise-ev.com/MembershipCard/MCSMP20A.binはそのまま動く

baud rate 9600〜16800bps

入力はEF3使用

Diskless Elf/OS

0番地ROM想定のhttp://www.sunrise-ev.com/MembershipCard/disklessElfOS.hex はSBC1802そのままで動く

baud rate 2400〜4600bps

入力はEF3使用

Pico/ElfのDisk-less ROM

8000番地ROM想定のhttp://www.elf-emulation.com/software/picoelf/pico_diskless.hexは動かない

baud rate 1200〜4600bps

入力はEF2使用

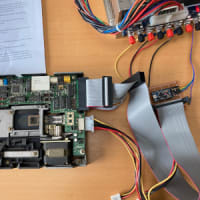

せっかくなのでJR2XZYさんの記事のボードを作成した。これにより8000番地ROM想定のpico_diskless.hexも動くはず。

片面万能ボードしかなかったので、上下逆に作成した。

CPUとICがぶつかるので、pinが完全に刺さらないが、電気的には問題ない

ところが動かない。オシロを使ってもわからない。ソフトも疑って逆アセンブラもrubyで書いてみたがわからない。最終ロジックアナライザで解決したので注意点として記載する。(アマゾンで購入した安いロジックアナライザ + pulseview(https://sigrok.org/wiki/PulseView)を使用)

JR2XZYさんのボードの動作原理

リセット後にはメモリへ出力されるA15は常に0。(前半32KB、後半32KBともROMをアクセスする(ミラー))

CPUが$8000以降をアクセス(CPUのA15がH)すると、74C74フリップフロップをTPAでトリガし、それ以降CPUのA15を反転させてメモリへ出力

(これによりCPUが前半32KBをアクセスする場合は、後半のRAMをアクセスし、後半32KBをアクセスする場合はROMをアクセスする)

例えばDiskless ELFではプログラム上はROMの最初は LBRA $8018。 0番地からこれを読み出しロングブランチを実行し、

$8018番地をフェッチした瞬間に、0~$7FFFで前半32KBをRAMがアクセス出来る状態とする。

非常に良く出来た仕組みであるが、私の環境では動かなかった。

原因1

CDP1802では、CLRがHになったあと0番地からアクセスを開始する。

良くデータシートを読むと

===https://www.renesas.com/eu/en/document/dst/cdp1802ac3-datasheet===

TPA and TPB are suppressed while reset is held

and the CPU is placed in S1. The first machine cycle after

termination of reset is an initialization cycle which requires 9

clock pulses. During this cycle the CPU remains in S1 and

register X, P, and R(0) are reset.

つまり0番地からアクセス開始する前にinitialization cycleが動くとのこと。

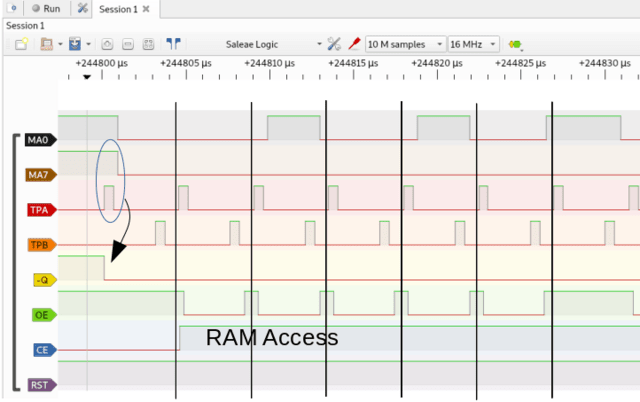

この情報だけでは気づかなかったが、ロジックアナライザで見るとTPAやTPBが出ている。

その上MA7までHになっている。これが原因で74HC74のセットが0番地アクセス前に起きてしまう。

この結果RAMの内容を実行し動かなかったと考えられる。

ロジックアナライザで確認(矢印部に注意) CE=Hなので、RAMをアクセスしている。

対応1

そこで余っていた74HC74の1/2を使い、クロックにMRD(OE)を使用することでリセットを0番地フェッチ以降に延長した。

0000 LBR 8018H

8018 LDI FF

801A PLO R2

を実行

ロジックアナライザで確認 8018アクセス時に-Q=Hとなり、0-7fffがRAM領域に変更される。

原因2

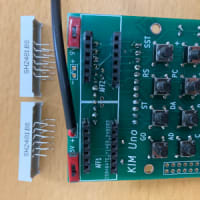

これは完全に私の回路の理解が十分でなかったことが原因で、最初はこのようにしていた。

これだとA7も反転してしまう。基板上パターンカットが2箇所となったが以下のように対応

その他

・ELFでは4MHzクロックであるのに対して、SBC1802では1.79MHz。ボーレートは最初にキーボードからリターンを入力することで自動的に変更されるが、9600には追従出来ないようだ。 9600*1.79/4.00=4296 のため、puttyでボーレートを変更しながら実験したところ、1200〜4600baudで通信が出来ることが確認できた。MCBASIC3やMCSMP20Aでは調整されているためか9600〜16800baudで動作が確認出来た。

・1802のinitialization cycleのMA7であるが、必ずHになるわけではない。Hの場合とLの場合が繰り返される。原因が理解出来なかったがリセットを引き伸ばせば必ず動くので良しとした。

※コメント投稿者のブログIDはブログ作成者のみに通知されます