CMOSの遅延時間に対する電源電圧および閾値電圧の依存性

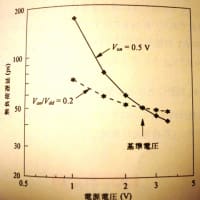

CMOSの遅延時間に対する電源電圧および閾値電圧の依存性を考える。

閾値電圧を0.5Vとし、定まったデバイスに対して電源電圧を低下させると真性遅延時間は急速に増加する。これはVddの減少によるIon/Vdd:コンダクタンスの減少に起因している。

VonがVddに比例して下げられれば低電圧下でもほとんどの動作性能を維持することが可能である。Von/Vdd=0.2と一定に保った場合、真性遅延時間の低下は緩和される。スイッチング抵抗は

Rsw=f(Vdd)/(K-(Von/Vdd))

と表すことが出来る。ただしこれはVon/ Vdd<0.5の時に成立する式である。

CMOSの動作時の電力消費は

P=C・Vdd^2・f

であらわされる。Cはクロック周期中に充放電される容量、fはクロック周波数である。デバイスレベルで電力消費を小さくするには電源電圧を下げる必要がある。

しかしながら高性能を求めるデバイスでは同時に閾値電圧も下げる必要がある。

一方で閾値電圧を下げることは待機電流Ioffを大幅に増加させてしまう。

待機時の消費電力は

Poff=W・Vdd・Ioff=W・Vdd・I0・exp(-qVt/(mkT))

とあらわされる。これらのことからVdd-Vt設計における電力消費と遅延時間のトレードオフにより定性的に表すことが出来る。

デバイスの目的によりVddとVtを調整して狙いのパフォーマンスが得られるようにしていく必要がある。電力を考えれば低電源電圧で高い閾値で動作させる必要がある。

寄生抵抗、寄生容量の遅延への影響

図にS/D抵抗のスイッチング抵抗への影響を示している。pMOSは単位幅辺りに流れる電流が低いために同じ割合の劣化に対しnMOSに対して高いRsdが許容できる。

S/D抵抗を原因とする性能低下を予測する概算は固有のスイッチング抵抗Rsdに75%~100%を加える式で表すことが出来る。

ΔRswn≒(0.75-1.0)Rsdn、ΔRswp≒(0.75-1.0)Rsdp

軽い負荷のCMOS回路ではGate-DrainのOverLap容量が遅延に影響する。

これは入力だけでなく出力容量にも加わりFB効果があるためである。

入力容量:Gate-Source容量+Gate-Drain容量

出力容量:Gate-Drain容量

さらにはミラー効果により入出力容量の寄与はもとの2倍になる。

ミラー効果とは充放電されるコンデンサの両側サイドの電圧が時間的に変化する際に容量が増加してしまう現象である。

図のような充電されつつある3つのコンデンサを考える。

充電電流は

i=C1・d(V-Vdd)/dt+C2・d(V-V2)/dt+C3・dV/dt

となりC1C3はミラー効果は存在しない。dV2/dt=-dV/dtの時

i=(C1+2C2+C3)・dV/dtとなり

充放電に関して2倍の容量を持っているようにみなせる。

出力容量の大部分は接合容量とDrain-基板容量で構成される。

接合容量は折り返しゲート構造を用いることにより低減できる。

CMOSの遅延時間に対する電源電圧および閾値電圧の依存性を考える。

閾値電圧を0.5Vとし、定まったデバイスに対して電源電圧を低下させると真性遅延時間は急速に増加する。これはVddの減少によるIon/Vdd:コンダクタンスの減少に起因している。

VonがVddに比例して下げられれば低電圧下でもほとんどの動作性能を維持することが可能である。Von/Vdd=0.2と一定に保った場合、真性遅延時間の低下は緩和される。スイッチング抵抗は

Rsw=f(Vdd)/(K-(Von/Vdd))

と表すことが出来る。ただしこれはVon/ Vdd<0.5の時に成立する式である。

CMOSの動作時の電力消費は

P=C・Vdd^2・f

であらわされる。Cはクロック周期中に充放電される容量、fはクロック周波数である。デバイスレベルで電力消費を小さくするには電源電圧を下げる必要がある。

しかしながら高性能を求めるデバイスでは同時に閾値電圧も下げる必要がある。

一方で閾値電圧を下げることは待機電流Ioffを大幅に増加させてしまう。

待機時の消費電力は

Poff=W・Vdd・Ioff=W・Vdd・I0・exp(-qVt/(mkT))

とあらわされる。これらのことからVdd-Vt設計における電力消費と遅延時間のトレードオフにより定性的に表すことが出来る。

デバイスの目的によりVddとVtを調整して狙いのパフォーマンスが得られるようにしていく必要がある。電力を考えれば低電源電圧で高い閾値で動作させる必要がある。

寄生抵抗、寄生容量の遅延への影響

図にS/D抵抗のスイッチング抵抗への影響を示している。pMOSは単位幅辺りに流れる電流が低いために同じ割合の劣化に対しnMOSに対して高いRsdが許容できる。

S/D抵抗を原因とする性能低下を予測する概算は固有のスイッチング抵抗Rsdに75%~100%を加える式で表すことが出来る。

ΔRswn≒(0.75-1.0)Rsdn、ΔRswp≒(0.75-1.0)Rsdp

軽い負荷のCMOS回路ではGate-DrainのOverLap容量が遅延に影響する。

これは入力だけでなく出力容量にも加わりFB効果があるためである。

入力容量:Gate-Source容量+Gate-Drain容量

出力容量:Gate-Drain容量

さらにはミラー効果により入出力容量の寄与はもとの2倍になる。

ミラー効果とは充放電されるコンデンサの両側サイドの電圧が時間的に変化する際に容量が増加してしまう現象である。

図のような充電されつつある3つのコンデンサを考える。

充電電流は

i=C1・d(V-Vdd)/dt+C2・d(V-V2)/dt+C3・dV/dt

となりC1C3はミラー効果は存在しない。dV2/dt=-dV/dtの時

i=(C1+2C2+C3)・dV/dtとなり

充放電に関して2倍の容量を持っているようにみなせる。

出力容量の大部分は接合容量とDrain-基板容量で構成される。

接合容量は折り返しゲート構造を用いることにより低減できる。