http://youtu.be/e2Jt4KV7yp0 動画

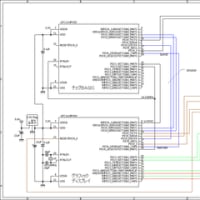

去年の12月に最終ターゲットをLatticeに決めて、Xilinxから回路図の移植を始めたのが苦行の始まり。

コンパイルしても全く動く気配をみせず、コンパイルも時間が掛かりバグった挙句にPCが破壊されると言うw

デバイスそのものは良いのに開発環境が糞という。

弄り始めた頃は本であった事もあって安心感もあったのに、めいっぱい煮え湯を飲まされた感じだ。

今年になってDE0-nanoを弄り始めて、先日オリジナルVDPもAlteraに持ってこようと思い移植作業を始めた。

Alteraで回路図はAVRソフトコアでやっていたけど、移植の度に1から作業しないとならない回路図は

非常にハンドリングが悪いので、オリジナルVDPは全部Verilogにしようと思った。

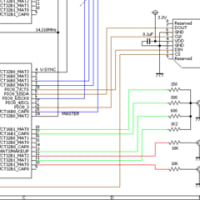

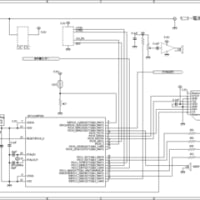

まずはXilinxで作った元の回路図を全て印刷。

verilog化の手掛かりにと回路図から変換された中間コードを探す、なぜかLatticeの中間コードを引き出してしまった。

Lattice用に悪戦苦闘している最中にもほんの少し改定してる部分もあったので、まぁコレでいいかって感じで。

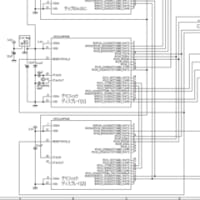

まずはコンパイルだけでも通るように、Latticeで使用していたライブラリを中身を作らずにインタフェースのみを実装して

一通り通るようにした。 軽いw そらそうか、全部端折られるからなw

軽快にコンパイルが通るのに気を良くして、本来なら回路図からverilog化する作業だった筈が、

空のままで良い筈のライブラリの実装を開始w ものの30分程度でライブラリが完成した。

全てを実装した筈なのに、全く動かないw なんでだ。

そのまま回路図とTRLをつき合わせて検証作業になだれ込んだw 本来のverilog化とは全く違う意味になってるw

回路図から生成された無機質な中間ソースを、回路図を見ながら見やすい形へ再配置及び結線。

結線名も無機質な名前から回路図を元に意味のある結線名へと変更作業することになった。

あまりにも無機質過ぎてそのままの中間ソースでは検証ができないと判断したからであった。

無機質な中間ソースを見やすい形にする作業の中で、Latticeの作業中には分からなかったバグが次々と浮上w

Lattice diamondの回路図からverilogへのトランスレートが全くの出鱈目である事が再度判明した。

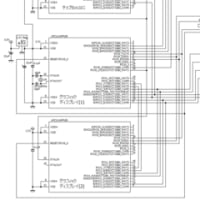

メーカー純正ツールでここまで酷いものとは夢にも思わなかったw

驚愕の事実っつーか、Lattice diamondで回路図使ってたら一生完成しないと言う事実が突きつけられた orz

Lattice diamondでの苦行は300時間以上を捧げていたので、もっと早くに見切りをつけるべきだったと後悔しきり。

そら挫折するわな、どんまい>過去の自分。

結線情報を本来の姿へ張り替えたら物凄くあっさりと完璧に動作しました。 まぁXilinxで動いてた物だから当たり前だが…

という事で、動作したソースコードを再度Latticeに持っていって幸せになれるかと思いきや、

マルツパーツ館からは既にLatticeのFPGAボードは無くなっていたというw

http://shop.cqpub.co.jp/hanbai/booklist/series/

書籍の方はまだ在庫あるみたいね、ふぅむ。

今のソースはverilogであってverilogにあらずw

回路図では無くなったのでとりあえず安心か。