NIOSを使ってみました(1)の続きになります。

NIOS IIのトリビアルな実装をしています。

(5) NIOS II eds(エンベデッド・デザイン・スイート)を起動してCのプログラムを作って、FPGAボードにダウンロード&実行する

いよいよ最後のステップです。

NIOS II edsを立ち上げると最初にworkspaceをどこにするかを聞いてきます。

Quartusのプロジェクトフォルダと一緒にするのがてっとりばやいです。一段階Softwareというフォルダを掘ってくれるので、ファイルが混ざったりすることもありません。

Fileメニュー → New → NIOS II Aplication and BSP from Templateを選びます。

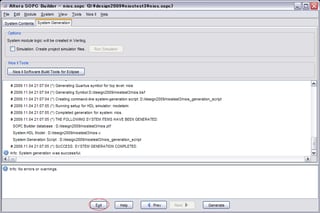

SOPC Information File Nameの欄にはQuartusのプロジェクトのフォルダにあるnios.sopcinfoを選びます。niosの部分はSOPC Builderの一番最初で決めたシステム名になります。

Project名を決めてやります。niostest3にしました。

左下のテンプレートはHello World Smallを選びました。このテンプレートは使用メモリが少ないのでブロックRAM上でも動作します。

Finishボタンを押します。

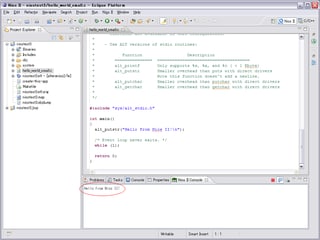

左のProject Explorerツリービューのプロジェクト名(今回はniostest3)をクリックして灰色に変えてから、Projectメニュー → Build Projectでプロジェクトをビルドします。

Runメニュー → Runを選びます。

Run Asというダイアログが出るのでNIOS II Hardwareを選んで(クリックして灰色に変えて)、OKを押します。

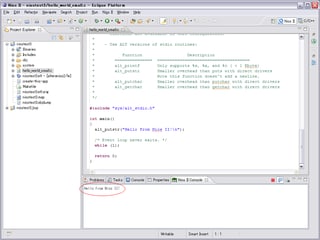

下のNios II Consoleに実行結果が出ます。今回は"Hello from Nios II!"というメッセージを表示します。中のプログラムは以下のようなものです。

ペリフェラルはsystem.hにメモリの番地が書いてあったりしますが、今回は何もないのでincludeしなくても平気です。

リセット(ボタン2)を押すともう一度"Hello from Nios II!"を表示してくれます。

このプログラムは無限ループなのでNios II Consoleの右上にある赤い四角を押してプログラムを終了してやります。

さて、以上で駆け足でしたがQuartusのプロジェクト作成から始まってNIOS II eds上での実行まで眺めてきました。結構、長いですね。

FPGAの部屋さんのまとめサイトを見ながら、独自ペリフェラル(Avalon-MMのスレーブ)を作ってみたりしました。

これからやりたいのは、DE0に搭載されているSDRAMをNiosから使うことです。

分かっていないのは、Nios II上で開発したソフトをROM化する方法です。PCと通信しなくても電源オンですぐ動き出すようにしたいです。ブロックRAMと同じ名前の.hexファイルがあって、これがブロックRAMの初期値になるんじゃないかと思います。.elfファイルを.hexに変換するツールとかがあるのかもしれません。

それにしても、1週間たらずのうちに2度もQuartusをインストールすることになるとは思ってませんでした。

おまけです。

NIOS II edsをインストールしたフォルダの下のbinというフォルダにnios2-terminal.exeというプログラムがあります。このプログラムを使うとNIOS II edsを使わなくてもDE0ボードと通信できます。TeraTermのJTAG UART版みたいなプログラムです。

NIOS IIのトリビアルな実装をしています。

(5) NIOS II eds(エンベデッド・デザイン・スイート)を起動してCのプログラムを作って、FPGAボードにダウンロード&実行する

いよいよ最後のステップです。

NIOS II edsを立ち上げると最初にworkspaceをどこにするかを聞いてきます。

Quartusのプロジェクトフォルダと一緒にするのがてっとりばやいです。一段階Softwareというフォルダを掘ってくれるので、ファイルが混ざったりすることもありません。

Fileメニュー → New → NIOS II Aplication and BSP from Templateを選びます。

SOPC Information File Nameの欄にはQuartusのプロジェクトのフォルダにあるnios.sopcinfoを選びます。niosの部分はSOPC Builderの一番最初で決めたシステム名になります。

Project名を決めてやります。niostest3にしました。

左下のテンプレートはHello World Smallを選びました。このテンプレートは使用メモリが少ないのでブロックRAM上でも動作します。

Finishボタンを押します。

左のProject Explorerツリービューのプロジェクト名(今回はniostest3)をクリックして灰色に変えてから、Projectメニュー → Build Projectでプロジェクトをビルドします。

Runメニュー → Runを選びます。

Run Asというダイアログが出るのでNIOS II Hardwareを選んで(クリックして灰色に変えて)、OKを押します。

下のNios II Consoleに実行結果が出ます。今回は"Hello from Nios II!"というメッセージを表示します。中のプログラムは以下のようなものです。

#include "sys/alt_stdio.h"

int main()

{

alt_putstr("Hello from Nios II!¥n");

while(1) ;

}

ペリフェラルはsystem.hにメモリの番地が書いてあったりしますが、今回は何もないのでincludeしなくても平気です。

リセット(ボタン2)を押すともう一度"Hello from Nios II!"を表示してくれます。

このプログラムは無限ループなのでNios II Consoleの右上にある赤い四角を押してプログラムを終了してやります。

さて、以上で駆け足でしたがQuartusのプロジェクト作成から始まってNIOS II eds上での実行まで眺めてきました。結構、長いですね。

FPGAの部屋さんのまとめサイトを見ながら、独自ペリフェラル(Avalon-MMのスレーブ)を作ってみたりしました。

これからやりたいのは、DE0に搭載されているSDRAMをNiosから使うことです。

分かっていないのは、Nios II上で開発したソフトをROM化する方法です。PCと通信しなくても電源オンですぐ動き出すようにしたいです。ブロックRAMと同じ名前の.hexファイルがあって、これがブロックRAMの初期値になるんじゃないかと思います。.elfファイルを.hexに変換するツールとかがあるのかもしれません。

それにしても、1週間たらずのうちに2度もQuartusをインストールすることになるとは思ってませんでした。

おまけです。

NIOS II edsをインストールしたフォルダの下のbinというフォルダにnios2-terminal.exeというプログラムがあります。このプログラムを使うとNIOS II edsを使わなくてもDE0ボードと通信できます。TeraTermのJTAG UART版みたいなプログラムです。