今月号のトラ技にデジタル・デザイン・テクノロジ誌の創刊号の付録基板の写真が出ています。LatticeXP2というFPGAのボードです。ぷるぷるさんにこの記事のコメントで教えていただきました。以前、shirouさんのコメントでもLatticeとのことでしたが、いよいよ明らかになりました。

写真のチップには上段からLFXP2-5E、5TN144C、A838RH20と書かれています。FPGAの部屋さんに解説があります。なひたふさんの記事「LatticeのXP2をはじめます」に特徴がまとめられています。

メーカーのLatticeXP2のページから拾ってきたスペックです。

ホームページには5と書いてありますが、LUT数は5kです。LatticeXP2もXilinx Spartan3と同じで2LUTが1sliceのようです。2.5k slice搭載ということでしょうか。XC3S250Eが2448slice、4896LUTなので、ほぼ同規模といった感じです。ブロックRAMはXC3S250Eが216kbit(24kバイト)なので少し小さくなります。

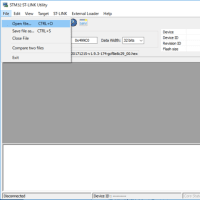

ダウンロードケーブルの回路図を探してみました。

http://www.fpga.com.cn/lattice/lattice_cable.pdf (pdfです)

ここにもあるみたいです。

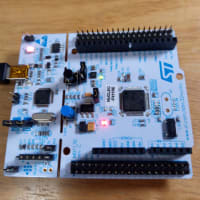

フラッシュ内蔵なのでコンフィグROMは不要です。写真からすると、たぶん3.3Vの水晶発振器が必要です。表面実装タイプとDIPタイプがどちらでも実装できるようなパターンになっています。3.3Vの水晶発振器はマルツで買えます(以前書いた「マルツに3.3V水晶発振器」)。

U2として14ピンのICが実装されていて、8pinのU3は未実装です。10pinのCN3はJTAGケーブルでしょうか。

初めてなので、とても楽しみです。

写真のチップには上段からLFXP2-5E、5TN144C、A838RH20と書かれています。FPGAの部屋さんに解説があります。なひたふさんの記事「LatticeのXP2をはじめます」に特徴がまとめられています。

メーカーのLatticeXP2のページから拾ってきたスペックです。

LUT 数 5 分散 RAM (Kbits) 10 EBR SRAM (Kbits) 166 EBR SRAM ブロック数 9 sysDSP ブロック数 3 18x18 乗算器数 12 PLL 数 2 最大ユーザI/O数 172

ホームページには5と書いてありますが、LUT数は5kです。LatticeXP2もXilinx Spartan3と同じで2LUTが1sliceのようです。2.5k slice搭載ということでしょうか。XC3S250Eが2448slice、4896LUTなので、ほぼ同規模といった感じです。ブロックRAMはXC3S250Eが216kbit(24kバイト)なので少し小さくなります。

ダウンロードケーブルの回路図を探してみました。

http://www.fpga.com.cn/lattice/lattice_cable.pdf (pdfです)

ここにもあるみたいです。

フラッシュ内蔵なのでコンフィグROMは不要です。写真からすると、たぶん3.3Vの水晶発振器が必要です。表面実装タイプとDIPタイプがどちらでも実装できるようなパターンになっています。3.3Vの水晶発振器はマルツで買えます(以前書いた「マルツに3.3V水晶発振器」)。

U2として14ピンのICが実装されていて、8pinのU3は未実装です。10pinのCN3はJTAGケーブルでしょうか。

初めてなので、とても楽しみです。

どうやって、書き込むのかは気になるところですね。確かにザイリンクスのケーブルとかを流用できるとうれしいです。

もしかして、なひたふさんの設計だったりすると、mitoujtagもあるかもしれませんね。